TJA1027 1. General description LIN 2.2A/SAE J2602 transceiver

... A loss of power (pins VBAT and GND) has no impact on the bus line or on the microcontroller. No reverse currents flow from the bus into pin LIN. The current path from VBAT to LIN via the integrated LIN slave termination resistor remains. The LIN transceiver can be disconnected from the power supply ...

... A loss of power (pins VBAT and GND) has no impact on the bus line or on the microcontroller. No reverse currents flow from the bus into pin LIN. The current path from VBAT to LIN via the integrated LIN slave termination resistor remains. The LIN transceiver can be disconnected from the power supply ...

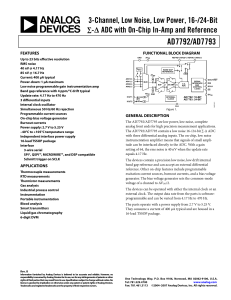

AD7792/AD7793 3-Channel, Low Noise, Low Power, 16/24-Bit ∑

... with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the internal clock ...

... with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the internal clock ...

... order to allow small remote sites with just a few Ethernet connections to be able to use the same access switch configurations as large campus Ethernet designs • Network security—Protects the network and users from malicious attacks by applying security using Catalyst Infrastructure Security Featur ...

AD7792 数据手册DataSheet下载

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

AD7980 数据手册DataSheet下载

... supply, VDD. It contains a low power, high speed, 16-bit sampling ADC and a versatile serial interface port. On the CNV rising edge, it samples an analog input IN+ between 0 V to REF with respect to a ground sense IN−. The reference voltage, REF, is applied externally and can be set independent of t ...

... supply, VDD. It contains a low power, high speed, 16-bit sampling ADC and a versatile serial interface port. On the CNV rising edge, it samples an analog input IN+ between 0 V to REF with respect to a ground sense IN−. The reference voltage, REF, is applied externally and can be set independent of t ...

NVT2001; NVT2002 1. General description Bidirectional voltage level translator for open-drain and

... circuit is designed to be supplied by Vref(B). To ensure the high-impedance state during power-up or power-down, EN must be LOW. All channels have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over dis ...

... circuit is designed to be supplied by Vref(B). To ensure the high-impedance state during power-up or power-down, EN must be LOW. All channels have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over dis ...

AD5280,82 - Analog Devices

... 256-position, digitally controlled variable resistors (VRs) 2 . The devices perform the same electronic adjustment function as a potentiometer, trimmer, or variable resistor. Each VR offers a completely programmable value of resistance between the A terminal and the wiper or the B terminal and the w ...

... 256-position, digitally controlled variable resistors (VRs) 2 . The devices perform the same electronic adjustment function as a potentiometer, trimmer, or variable resistor. Each VR offers a completely programmable value of resistance between the A terminal and the wiper or the B terminal and the w ...

AD7792/AD7793 3-Channel, Low Noise, Low Power, 16-/24-Bit ∑

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

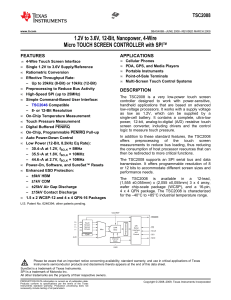

1.2V to 3.6V, 12-Bit, Nanopower. 4

... as low as 1.2V, which can be supplied by a single-cell battery. It contains a complete, ultra-low power, 12-bit, analog-to-digital (A/D) resistive touch screen converter, including drivers and the control logic to measure touch pressure. In addition to these standard features, the TSC2008 offers pre ...

... as low as 1.2V, which can be supplied by a single-cell battery. It contains a complete, ultra-low power, 12-bit, analog-to-digital (A/D) resistive touch screen converter, including drivers and the control logic to measure touch pressure. In addition to these standard features, the TSC2008 offers pre ...

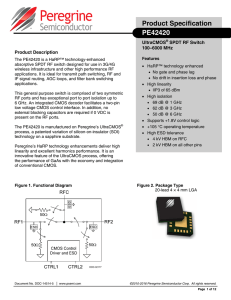

Datasheet - Peregrine Semiconductor

... Advance Information: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. Preliminary Specification: The datasheet contains preliminary data. Additional data ma ...

... Advance Information: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. Preliminary Specification: The datasheet contains preliminary data. Additional data ma ...

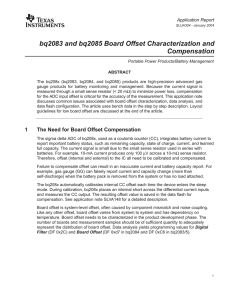

bq2083 and bq2085 Board Offset Characterization and Compensation

... measurement, followed by internal offset, which is the CC offset. The difference of the two offset numbers is written to Board Offset flash location by EVSW. The engineering unit for offset is 0.584 µV/count for the bq2083 and bq2085, and 0.146 µV/count for the bq2084. The positive sign indicates of ...

... measurement, followed by internal offset, which is the CC offset. The difference of the two offset numbers is written to Board Offset flash location by EVSW. The engineering unit for offset is 0.584 µV/count for the bq2083 and bq2085, and 0.146 µV/count for the bq2084. The positive sign indicates of ...

PTN3381D

... DVI v1.0 or HDMI v1.3a specification. By using PTN3381D, chip set vendors are able to implement such reconfigurable I/Os on multi-mode display source devices, allowing the support of multiple display standards while keeping the number of chip set I/O pins low. See Figure 1. The PTN3381D main high-sp ...

... DVI v1.0 or HDMI v1.3a specification. By using PTN3381D, chip set vendors are able to implement such reconfigurable I/Os on multi-mode display source devices, allowing the support of multiple display standards while keeping the number of chip set I/O pins low. See Figure 1. The PTN3381D main high-sp ...

Chapter 8 Lecture Presentation

... Options: Variable length field, allows packet to request special features such as security level, route to be taken by the packet, and timestamp at each router. Detailed descriptions of these options can be found in [RFC 791]. ...

... Options: Variable length field, allows packet to request special features such as security level, route to be taken by the packet, and timestamp at each router. Detailed descriptions of these options can be found in [RFC 791]. ...

PCA9517A 1. General description Level translating I

... The size of these pull-up resistors depends on the system, but each side of the repeater must have a pull-up resistor. This part designed to work with Standard mode and Fast mode I2C-bus devices in addition to SMBus devices. Standard mode I2C-bus devices only specify 3 mA output drive; this limits t ...

... The size of these pull-up resistors depends on the system, but each side of the repeater must have a pull-up resistor. This part designed to work with Standard mode and Fast mode I2C-bus devices in addition to SMBus devices. Standard mode I2C-bus devices only specify 3 mA output drive; this limits t ...

DS3906 Triple NV Low Step Size Variable Resistor Plus Memory General Description

... The DS3906 contains 16 bytes of User EEPROM plus 3 NV resistor registers. Refer to Table 1. Communication with the memory/registers is achieved through the I2Ccompatible serial interface and is described in subsequent sections. Each of the three resistors in the DS3906 has its own control register u ...

... The DS3906 contains 16 bytes of User EEPROM plus 3 NV resistor registers. Refer to Table 1. Communication with the memory/registers is achieved through the I2Ccompatible serial interface and is described in subsequent sections. Each of the three resistors in the DS3906 has its own control register u ...

The 2016 SNIA Dictionary

... The SNIA Dictionary contains terms and definitions related to storage and other information technologies, and is the storage networking industry's most comprehensive attempt to date to arrive at a common body of terminology for the technologies it represents. The terms go through a rigorous technica ...

... The SNIA Dictionary contains terms and definitions related to storage and other information technologies, and is the storage networking industry's most comprehensive attempt to date to arrive at a common body of terminology for the technologies it represents. The terms go through a rigorous technica ...

DS3906 Triple NV Low Step Size Variable Resistor Plus Memory

... The DS3906 contains 16 bytes of User EEPROM plus 3 NV resistor registers. Refer to Table 1. Communication with the memory/registers is achieved through the I2Ccompatible serial interface and is described in subsequent sections. Each of the three resistors in the DS3906 has its own control register u ...

... The DS3906 contains 16 bytes of User EEPROM plus 3 NV resistor registers. Refer to Table 1. Communication with the memory/registers is achieved through the I2Ccompatible serial interface and is described in subsequent sections. Each of the three resistors in the DS3906 has its own control register u ...

PCA2000-PCA2001

... The PCA2000 has a battery End Of Life (EOL) warning function. If the battery voltage drops below the EOL threshold voltage (which can be programmed for silver oxide or lithium batteries), the motor steps change from one pulse per second to a burst of four pulses every 4 seconds. The PCA2001 uses the ...

... The PCA2000 has a battery End Of Life (EOL) warning function. If the battery voltage drops below the EOL threshold voltage (which can be programmed for silver oxide or lithium batteries), the motor steps change from one pulse per second to a burst of four pulses every 4 seconds. The PCA2001 uses the ...

Cold-Junction Compensated Thermocouple-to-Digital Converter General Description Features

... updated when CS is high. Drive CS low to output the first bit on the SO pin. A complete serial-interface read of the cold-junction compensated thermocouple temperature requires 14 clock cycles. Thirty-two clock cycles are required to read both the thermocouple and reference junction temperatures (Ta ...

... updated when CS is high. Drive CS low to output the first bit on the SO pin. A complete serial-interface read of the cold-junction compensated thermocouple temperature requires 14 clock cycles. Thirty-two clock cycles are required to read both the thermocouple and reference junction temperatures (Ta ...

AD7688 数据手册DataSheet下载

... approximation, analog-to-digital converter (ADC) that operates from a single 5 V power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface port. The part also contains a low noise, wide bandwidth, ...

... approximation, analog-to-digital converter (ADC) that operates from a single 5 V power supply, VDD. It contains a low power, high speed, 16-bit sampling ADC with no missing codes, an internal conversion clock, and a versatile serial interface port. The part also contains a low noise, wide bandwidth, ...

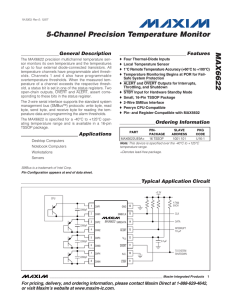

MAX6622 5-Channel Precision Temperature Monitor General Description Features

... does not cause either ALERT or OVERT to assert. A bit in the status register for the corresponding channel is set to 1 and the temperature data for the channel is stored as all 1s (FFh). It takes approximately 4ms for the MAX6622 to detect a diode fault. Once a diode fault is detected, the MAX6622 g ...

... does not cause either ALERT or OVERT to assert. A bit in the status register for the corresponding channel is set to 1 and the temperature data for the channel is stored as all 1s (FFh). It takes approximately 4ms for the MAX6622 to detect a diode fault. Once a diode fault is detected, the MAX6622 g ...

Document

... (Fig. 5), several devices can be connected physically in a bus network, and control of the transmit and receive conductors must be negotiated. For a multidrop connection, only one relay can communicate at a time. Software and hardware determine which device has permission to transmit, preventing dat ...

... (Fig. 5), several devices can be connected physically in a bus network, and control of the transmit and receive conductors must be negotiated. For a multidrop connection, only one relay can communicate at a time. Software and hardware determine which device has permission to transmit, preventing dat ...