LP8550 High-Efficiency LED Backlight Driver for Notebooks (Rev. E)

... Automatic PWM dimming at lower brightness values and current dimming at higher brightness values can be used to improve the optical efficiency. Internal EEPROM is used for storing the configuration data. This makes it possible to have minimum external component count and make the solution very small ...

... Automatic PWM dimming at lower brightness values and current dimming at higher brightness values can be used to improve the optical efficiency. Internal EEPROM is used for storing the configuration data. This makes it possible to have minimum external component count and make the solution very small ...

PCAL6408A

... expansion for most microcontroller families via the I2C-bus interface. NXP I/O expanders provide a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in battery-powered mobile applications for interfacing to sensors, push buttons, keypad, etc. I ...

... expansion for most microcontroller families via the I2C-bus interface. NXP I/O expanders provide a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in battery-powered mobile applications for interfacing to sensors, push buttons, keypad, etc. I ...

PCA9517A 1. General description Level translating I

... The size of these pull-up resistors depends on the system, but each side of the repeater must have a pull-up resistor. This part designed to work with Standard mode and Fast mode I2C-bus devices in addition to SMBus devices. Standard mode I2C-bus devices only specify 3 mA output drive; this limits t ...

... The size of these pull-up resistors depends on the system, but each side of the repeater must have a pull-up resistor. This part designed to work with Standard mode and Fast mode I2C-bus devices in addition to SMBus devices. Standard mode I2C-bus devices only specify 3 mA output drive; this limits t ...

LTC2436-1 - 2-Channel Differential Input 16

... after the first rising edge of SCK, the device begins outputting the conversion result. Taking CS high at this point will terminate the data output state and start a new conversion. There is no latency in the conversion result. The data output corresponds to the conversion just performed. This resul ...

... after the first rising edge of SCK, the device begins outputting the conversion result. Taking CS high at this point will terminate the data output state and start a new conversion. There is no latency in the conversion result. The data output corresponds to the conversion just performed. This resul ...

DS3901 Triple, 8-Bit NV Variable Resistor with Dual Settings and User EEPROM

... L0_SW: Selectable switch (see the Block Diagram) that allows for an external shunt resistor to be connected to the L0 pin. 0 = Switch L0_SW is open (default). 1 = Switch L0_SW is closed. BSC: A control bit that, when OR’d with the state of the BK_SEL pin, selects which bank of registers will be used ...

... L0_SW: Selectable switch (see the Block Diagram) that allows for an external shunt resistor to be connected to the L0 pin. 0 = Switch L0_SW is open (default). 1 = Switch L0_SW is closed. BSC: A control bit that, when OR’d with the state of the BK_SEL pin, selects which bank of registers will be used ...

6LoWPAN: The Wireless Embedded Internet

... John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, United Kingdom. For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wil ...

... John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, United Kingdom. For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wil ...

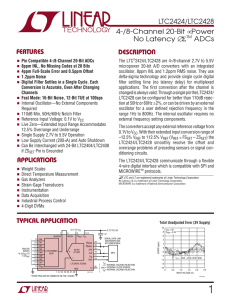

LTC2424/LTC2428 - 4-/8-Channel 20-Bit

... Note 9: The converter is in external SCK mode of operation such that the SCK pin is used as digital input. The frequency of the clock signal driving SCK during the data output is fESCK and is expressed in kHz. Note 10: The converter is in internal SCK mode of operation such that the SCK pin is used ...

... Note 9: The converter is in external SCK mode of operation such that the SCK pin is used as digital input. The frequency of the clock signal driving SCK during the data output is fESCK and is expressed in kHz. Note 10: The converter is in internal SCK mode of operation such that the SCK pin is used ...

NVT2008; NVT2010 1. General description Bidirectional voltage-level translator for open-drain and

... The NVT2008/NVT2010 are bidirectional voltage level translators operational from 1.0 V to 3.6 V (Vref(A)) and 1.8 V to 5.5 V (Vref(B)), which allow bidirectional voltage translations between 1.0 V and 5 V without the need for a direction pin in open-drain or push-pull applications. Bit widths of 8-b ...

... The NVT2008/NVT2010 are bidirectional voltage level translators operational from 1.0 V to 3.6 V (Vref(A)) and 1.8 V to 5.5 V (Vref(B)), which allow bidirectional voltage translations between 1.0 V and 5 V without the need for a direction pin in open-drain or push-pull applications. Bit widths of 8-b ...

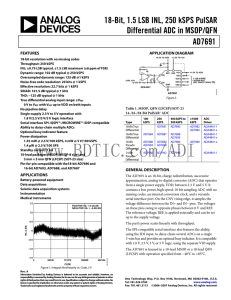

18-Bit, 1.5 LSB INL, 250 kSPS PulSAR Differential ADC in MSOP/QFN AD7691

... Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provides multiple features. It selects the interface mode of the ADC as follows: Chain mode is selected if SDI is low during the CNV rising edge. In this mode, SDI is ...

... Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provides multiple features. It selects the interface mode of the ADC as follows: Chain mode is selected if SDI is low during the CNV rising edge. In this mode, SDI is ...

LC88F52H0A

... 1) OSC1, RC and OSC0 oscillators automatically stop. 2) There are the six ways of releasing the HOLD mode. (1) Setting the reset pin to the low level (2) Setting at least one of the INT0, INT1, INT2, INT4, INT5, INT6, and INT7 pins to the specified level (3) Having an interrupt source established at ...

... 1) OSC1, RC and OSC0 oscillators automatically stop. 2) There are the six ways of releasing the HOLD mode. (1) Setting the reset pin to the low level (2) Setting at least one of the INT0, INT1, INT2, INT4, INT5, INT6, and INT7 pins to the specified level (3) Having an interrupt source established at ...

PTN3360D 1. General description Enhanced performance HDMI/DVI level shifter with active DDC

... differential signaling on the source side, to TMDS-type DC-coupled differential current-mode signaling terminated into 50 to 3.3 V on the sink side. Additionally, the PTN3360D provides a single-ended active buffer for voltage translation of the HPD signal from 5 V on the sink side to 3.3 V on the ...

... differential signaling on the source side, to TMDS-type DC-coupled differential current-mode signaling terminated into 50 to 3.3 V on the sink side. Additionally, the PTN3360D provides a single-ended active buffer for voltage translation of the HPD signal from 5 V on the sink side to 3.3 V on the ...

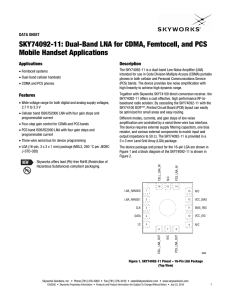

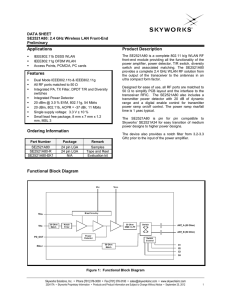

SKY74092-11 数据资料DataSheet下载

... SKY74100 DCR™, Printed Circuit Board (PCB) layout can easily be optimized for small areas and easy routing. ...

... SKY74100 DCR™, Printed Circuit Board (PCB) layout can easily be optimized for small areas and easy routing. ...

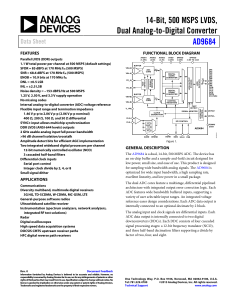

14-Bit, 500 MSPS LVDS, Dual Analog-to

... threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly reduce the system gain to avoid an overrange condition at the ADC input. In addition to the fast detect outputs, the AD9684 also offers signal monitoring capability. The signal moni ...

... threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly reduce the system gain to avoid an overrange condition at the ADC input. In addition to the fast detect outputs, the AD9684 also offers signal monitoring capability. The signal moni ...

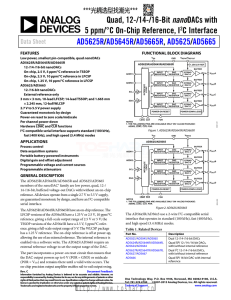

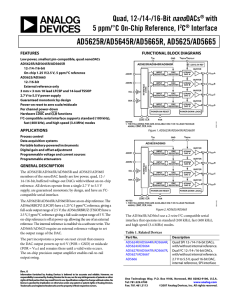

AD5625R/AD5645R/AD5665R, AD5625/AD5665 (Rev. C)

... LFCSP versions of the AD56x5R have a 1.25 V or 2.5 V, 10 ppm/°C reference, giving a full-scale output range of 2.5 V or 5 V; the TSSOP versions of the AD56x5R have a 2.5 V, 5 ppm/°C reference, giving a full-scale output range of 5 V. The WLCSP package has a 1.25 V reference. The on-chip reference is ...

... LFCSP versions of the AD56x5R have a 1.25 V or 2.5 V, 10 ppm/°C reference, giving a full-scale output range of 2.5 V or 5 V; the TSSOP versions of the AD56x5R have a 2.5 V, 5 ppm/°C reference, giving a full-scale output range of 5 V. The WLCSP package has a 1.25 V reference. The on-chip reference is ...

EN 301 192 - V1.6.1

... The present document can be downloaded from: http://www.etsi.org/standards-search The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorizati ...

... The present document can be downloaded from: http://www.etsi.org/standards-search The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorizati ...

AD5625R/AD5645R/AD5665R, AD5625/AD5665

... Power Supply Input. These parts can be operated from 2.7 V to 5.5 V, and the supply should be decoupled with a 10 μF capacitor in parallel with a 0.1 μF capacitor to GND. Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation. Analog Output Voltage from DAC C. The output a ...

... Power Supply Input. These parts can be operated from 2.7 V to 5.5 V, and the supply should be decoupled with a 10 μF capacitor in parallel with a 0.1 μF capacitor to GND. Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation. Analog Output Voltage from DAC C. The output a ...

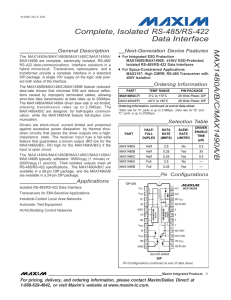

MAX1490AEPG WORD

... MAX1490B are complete, electrically isolated, RS-485/ RS-422 data-communications interface solutions in a hybrid microcircuit. Transceivers, optocouplers, and a transformer provide a complete interface in a standard DIP package. A single +5V supply on the logic side powers both sides of the interfac ...

... MAX1490B are complete, electrically isolated, RS-485/ RS-422 data-communications interface solutions in a hybrid microcircuit. Transceivers, optocouplers, and a transformer provide a complete interface in a standard DIP package. A single +5V supply on the logic side powers both sides of the interfac ...