Document

... (Fig. 5), several devices can be connected physically in a bus network, and control of the transmit and receive conductors must be negotiated. For a multidrop connection, only one relay can communicate at a time. Software and hardware determine which device has permission to transmit, preventing dat ...

... (Fig. 5), several devices can be connected physically in a bus network, and control of the transmit and receive conductors must be negotiated. For a multidrop connection, only one relay can communicate at a time. Software and hardware determine which device has permission to transmit, preventing dat ...

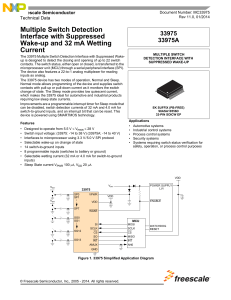

MC33975, MC9375A, Multiple Switch Detection Interface with

... The device also features a 22-to-1 analog multiplexer for reading inputs as analog. The 33975 device has two modes of operation, Normal and Sleep. Normal mode allows programming of the device and supplies switch contacts with pull-up or pull-down current as it monitors the switch change of state. Th ...

... The device also features a 22-to-1 analog multiplexer for reading inputs as analog. The 33975 device has two modes of operation, Normal and Sleep. Normal mode allows programming of the device and supplies switch contacts with pull-up or pull-down current as it monitors the switch change of state. Th ...

PCAL9535A 1. General description Low-voltage 16-bit I

... The PCAL9535A open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed. INT can be connected to the interrupt input of a microcontroller. By sending an int ...

... The PCAL9535A open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed. INT can be connected to the interrupt input of a microcontroller. By sending an int ...

Slide 1

... Paragraph 3.4.1 of the Amended Annex requires that ATN shall either use International Organization for Standardization (ISO) communication standards for Open System Interconnection (ISO) or use the Internet Society (ISOC) communications standards for the Internet protocol Suite (IPS) ICAO circulat ...

... Paragraph 3.4.1 of the Amended Annex requires that ATN shall either use International Organization for Standardization (ISO) communication standards for Open System Interconnection (ISO) or use the Internet Society (ISOC) communications standards for the Internet protocol Suite (IPS) ICAO circulat ...

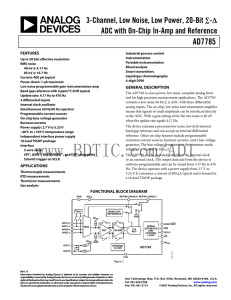

AD7785 3-Channel, Low Noise, Low Power, 20-Bit ∑-Δ

... continuous with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the inte ...

... continuous with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the inte ...

Latency - (SCTE) - New Jersey Chapter

... cable system, the majority of signals are reflections and microreflections that arrive after the desired signal. Cable modems and digital set top boxes must be able to handle pre and post (DELAYED) signals at levels defined by DVB standards. If the equalizer is pushed beyond those limits, errors wil ...

... cable system, the majority of signals are reflections and microreflections that arrive after the desired signal. Cable modems and digital set top boxes must be able to handle pre and post (DELAYED) signals at levels defined by DVB standards. If the equalizer is pushed beyond those limits, errors wil ...

LAMPIRAN A RANGKAIAN

... The AVR core com bines a rich instruction set with 32 general purpose w orking registers. All the 32 registers are directly connected to the Arithm etic Logic Unit (ALU ), allowing tw o independent registers to b e accesse d in on e single instructio n execute d in on e clo ck cycle . The resulting ...

... The AVR core com bines a rich instruction set with 32 general purpose w orking registers. All the 32 registers are directly connected to the Arithm etic Logic Unit (ALU ), allowing tw o independent registers to b e accesse d in on e single instructio n execute d in on e clo ck cycle . The resulting ...

PTN3355

... DPCD registers that are part of the VESA DisplayPort standard are described in detail in Ref. 1. The following describes the specific implementation by PTN3355 only. PTN3355 DisplayPort receiver capability and status information about the link are reported by DisplayPort Configuration Data (DPCD) re ...

... DPCD registers that are part of the VESA DisplayPort standard are described in detail in Ref. 1. The following describes the specific implementation by PTN3355 only. PTN3355 DisplayPort receiver capability and status information about the link are reported by DisplayPort Configuration Data (DPCD) re ...

ADS5281 数据资料 dataSheet 下载

... IOUT refers to the LVDS buffer current setting; RLOAD is the differential load resistance between the LVDS output pair. ...

... IOUT refers to the LVDS buffer current setting; RLOAD is the differential load resistance between the LVDS output pair. ...

ST7LNB0V2Y0

... microcontroller specifications version 1.0, the ST7LNB0V2Y0 does not scan the control pins in order to determine the slave configuration. Instead all configuration parameters must be programmed for each specific application, and an option list (see Section 8: Device configuration) must be filled-in ...

... microcontroller specifications version 1.0, the ST7LNB0V2Y0 does not scan the control pins in order to determine the slave configuration. Instead all configuration parameters must be programmed for each specific application, and an option list (see Section 8: Device configuration) must be filled-in ...

BACnet Fundamentals Course #801

... BACnet provides a universal model for creating building automation systems which can interoperate BACnet is a specification that a manufacturer can use to make interoperable systems to work in a BACnet environment. Owners and specifiers use BACnet as a tool for specification of interoperable systems ...

... BACnet provides a universal model for creating building automation systems which can interoperate BACnet is a specification that a manufacturer can use to make interoperable systems to work in a BACnet environment. Owners and specifiers use BACnet as a tool for specification of interoperable systems ...

TR 0006 - oneM2M

... This is a draft oneM2M document and should not be relied upon; the final version, if any, will be made available by oneM2M Partners Type 1. ...

... This is a draft oneM2M document and should not be relied upon; the final version, if any, will be made available by oneM2M Partners Type 1. ...

International Technical Support Organization Asynchronous

... When you send information to IBM, you grant IBM a non-exclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you. Copyright International Business Machines Corporation 1995. All rights reserved. Note to U.S. Government Users — Do ...

... When you send information to IBM, you grant IBM a non-exclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you. Copyright International Business Machines Corporation 1995. All rights reserved. Note to U.S. Government Users — Do ...

MAX14824 IO-Link Master Transceiver General Description Features

... The MAX14824 is an IO-LinkM master interface that integrates an IO-Link physical layer transceiver with an auxiliary digital input and two linear regulators. High port count IO-Link master applications are supported through in-band SPI addressing, and the 12MHz SPI interface minimizes host controlle ...

... The MAX14824 is an IO-LinkM master interface that integrates an IO-Link physical layer transceiver with an auxiliary digital input and two linear regulators. High port count IO-Link master applications are supported through in-band SPI addressing, and the 12MHz SPI interface minimizes host controlle ...

MC33972, Multiple Switch Detection Interface with Suppressed

... to the microprocessor unit (MCU) through a serial peripheral interface (SPI). The device also features a 22-to-1 analog multiplexer for reading inputs as analog. The analog input signal is buffered and provided on the AMUX output pin for the MCU to read. The 33972 device has two modes of operation, ...

... to the microprocessor unit (MCU) through a serial peripheral interface (SPI). The device also features a 22-to-1 analog multiplexer for reading inputs as analog. The analog input signal is buffered and provided on the AMUX output pin for the MCU to read. The 33972 device has two modes of operation, ...

Kinetis K22: 120 MHz Cortex-M4F up to 1MB Flash (80 pin)

... • Flash write voltage range: 1.71 to 3.6 V • Temperature range (ambient): –40 to 105°C ...

... • Flash write voltage range: 1.71 to 3.6 V • Temperature range (ambient): –40 to 105°C ...

An integrated CMOS optical receiver with clock and data recovery circuit

... data can be transported over vast distances without significant loss of signal integrity. However, there is an increasing challenge for users to directly and seamlessly access high capacity information from networks. The multimedia used by users is not efficient for high speed operations and the thr ...

... data can be transported over vast distances without significant loss of signal integrity. However, there is an increasing challenge for users to directly and seamlessly access high capacity information from networks. The multimedia used by users is not efficient for high speed operations and the thr ...

AD5246 数据手册DataSheet下载

... solution for 128-position adjustment applications. This device performs the same electronic adjustment function as a variable resistor. Available in four different end-to-end resistance values (5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ), these low temperature coefficient devices are ideal for high accuracy and sta ...

... solution for 128-position adjustment applications. This device performs the same electronic adjustment function as a variable resistor. Available in four different end-to-end resistance values (5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ), these low temperature coefficient devices are ideal for high accuracy and sta ...

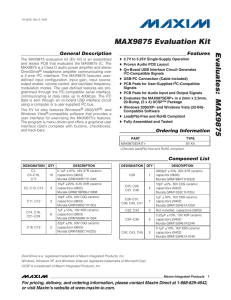

Evaluates: MAX9875 MAX9875 Evaluation Kit General Description Features

... operation. The Class D Oscillator group box controls and displays the oscillator frequency. The MAX9875 Master Controls group box provides the main controls for the MAX9875 IC. The Input Configuration, Input Gain, and Input Source group boxes configure the input configurations for the MAX9875 EV kit ...

... operation. The Class D Oscillator group box controls and displays the oscillator frequency. The MAX9875 Master Controls group box provides the main controls for the MAX9875 IC. The Input Configuration, Input Gain, and Input Source group boxes configure the input configurations for the MAX9875 EV kit ...

ESnet - Indico

... • ESnet provides network and collaboration services to Office of Science laboratories and to sites of other DOE programs in cases where this increases cost ...

... • ESnet provides network and collaboration services to Office of Science laboratories and to sites of other DOE programs in cases where this increases cost ...

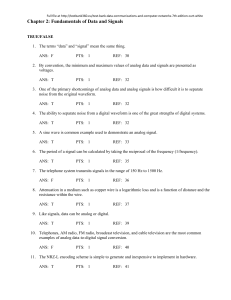

FREE Sample Here

... 25. Currently, ____________________ supports more than 110 different code charts (languages and symbol sets). ANS: Unicode PTS: 1 ...

... 25. Currently, ____________________ supports more than 110 different code charts (languages and symbol sets). ANS: Unicode PTS: 1 ...

PCAL9555A 1. General description Low-voltage 16-bit I

... The PCAL9555A open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed. INT can be connected to the interrupt input of a microcontroller. By sending an int ...

... The PCAL9555A open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed. INT can be connected to the interrupt input of a microcontroller. By sending an int ...