MAX19791 50MHz to 4000MHz Dual Analog Voltage Variable

... Both attenuators share a common analog control and can be cascaded together to yield 46dB of total attenuation range with a typical combined linear control slope of 16dB/ V (5V operation). ...

... Both attenuators share a common analog control and can be cascaded together to yield 46dB of total attenuation range with a typical combined linear control slope of 16dB/ V (5V operation). ...

ADF4360-9 数据手册DataSheet 下载

... Charge Pump Ground. This is the ground return path for the charge pump. Analog Power Supply. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin. AVDD must have the same value as DVDD. Analog Ground. This is the ground r ...

... Charge Pump Ground. This is the ground return path for the charge pump. Analog Power Supply. This ranges from 3.0 V to 3.6 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to this pin. AVDD must have the same value as DVDD. Analog Ground. This is the ground r ...

MC33290

... data rate is set by the fall time and the rise time. The fall time is set by the output driver. The rise time is set by the bus capacitance and the pull-up resistors on the bus. The fall time of the 33290 allows data rates up to 150 kbps using a 30 percent maximum bit time transition value. The seri ...

... data rate is set by the fall time and the rise time. The fall time is set by the output driver. The rise time is set by the bus capacitance and the pull-up resistors on the bus. The fall time of the 33290 allows data rates up to 150 kbps using a 30 percent maximum bit time transition value. The seri ...

AD5066 数据手册DataSheet 下载

... Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low, it powers on the SCLK and DIN buffers and enables the input shift register. Data is transferred in on the falling edges of the next 32 clocks. If SYNC is taken high before the 32nd falling edge ...

... Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low, it powers on the SCLK and DIN buffers and enables the input shift register. Data is transferred in on the falling edges of the next 32 clocks. If SYNC is taken high before the 32nd falling edge ...

NCP1351PRINTGEVB NCP1351 16 V/32 V – 40 W Printer Power Supply Evaluation Board

... timer duration of at least 500 ms (to be able to deliver the 62 W power peak during 400 ms), the timer capacitor C10 must be 1.5 mF. This value will be adjusted depending on the specification, according to the maximum peak power duration the adapter must sustain. If anyway a constant overpower prote ...

... timer duration of at least 500 ms (to be able to deliver the 62 W power peak during 400 ms), the timer capacitor C10 must be 1.5 mF. This value will be adjusted depending on the specification, according to the maximum peak power duration the adapter must sustain. If anyway a constant overpower prote ...

Physical Modeling of the Capacitance and Capacitive Coupling

... beyond [6], [7], and thereby, short and tiny through-oxide vias (TOVs) [see Fig. 1(c)] instead of TSVs can be used. For example, the TOV (with a diameter of < 3 μm and a height of ∼ 8 μm) fabricated in 0.18-μm technology [7] is already smaller than the TSV (with a diameter of ∼ 5 μm and a height of ...

... beyond [6], [7], and thereby, short and tiny through-oxide vias (TOVs) [see Fig. 1(c)] instead of TSVs can be used. For example, the TOV (with a diameter of < 3 μm and a height of ∼ 8 μm) fabricated in 0.18-μm technology [7] is already smaller than the TSV (with a diameter of ∼ 5 μm and a height of ...

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE)

... Multilevel inverters [2] are significantly different from the ordinary inverter where it generates more than two levels. The semiconductor devices are not connected in series to form one single high-voltage switch. In which each group of devices contribute to a step in the output voltage waveform. T ...

... Multilevel inverters [2] are significantly different from the ordinary inverter where it generates more than two levels. The semiconductor devices are not connected in series to form one single high-voltage switch. In which each group of devices contribute to a step in the output voltage waveform. T ...

Physics 212 Sample Question Bank II 2011

... in series to a battery. The quantity that is the same for the two wires is: (A) the potential difference across the length of each segment. (B) the current in each segment. (C) the current density in each segment. (D) the electric field in each segment. (E) the electron drift velocity in each segmen ...

... in series to a battery. The quantity that is the same for the two wires is: (A) the potential difference across the length of each segment. (B) the current in each segment. (C) the current density in each segment. (D) the electric field in each segment. (E) the electron drift velocity in each segmen ...

AD7899 数据手册DataSheet下载

... has finished. The function of the BUSY/EOC is determined by the state of CONVST at the end of conversion. See the Timing and Control Section. Read Input. Active low logic input which is used in conjunction with CS low to enable the data outputs. Chip Select Input. Active low logic input. The device ...

... has finished. The function of the BUSY/EOC is determined by the state of CONVST at the end of conversion. See the Timing and Control Section. Read Input. Active low logic input which is used in conjunction with CS low to enable the data outputs. Chip Select Input. Active low logic input. The device ...

555 - Faculty

... When the voltage at this pin is brought below 1/3 VCC the flip-flop is set causing pin 3 to produce a high state. Allowable applied voltage is between VCC (pin 8) and ground (pin 1). ...

... When the voltage at this pin is brought below 1/3 VCC the flip-flop is set causing pin 3 to produce a high state. Allowable applied voltage is between VCC (pin 8) and ground (pin 1). ...

IETE Journal of Research Unity/Variable-gain Voltage

... associated with actual DXCCII implementation, on the performance of the developed topologies are also included. Finally, simulation program with integrated circuit emphasis (SPICE) simulation results based on level 49, 0.25 µm TSMC complementary metal-oxide-semiconductor (CMOS) technology parameters ...

... associated with actual DXCCII implementation, on the performance of the developed topologies are also included. Finally, simulation program with integrated circuit emphasis (SPICE) simulation results based on level 49, 0.25 µm TSMC complementary metal-oxide-semiconductor (CMOS) technology parameters ...

Avtron Neutral Grounding Resistors Type ANG • Elements are triple

... to industrial distribution systems by limiting ground fault current to reasonable levels. In a typical solidly grounded four wire system, the neutral is tied directly to earth ground. This can cause high ground fault current (typically 10,000 to 20,000 amps) and excessive damage to transformers, gen ...

... to industrial distribution systems by limiting ground fault current to reasonable levels. In a typical solidly grounded four wire system, the neutral is tied directly to earth ground. This can cause high ground fault current (typically 10,000 to 20,000 amps) and excessive damage to transformers, gen ...

AD5246 数据手册DataSheet下载

... resistor. Available in four different end-to-end resistance values (5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ), these low temperature coefficient devices are ideal for high accuracy and stability variable resistance adjustments. The wiper settings are controllable through the I2C compatible digital interface, whic ...

... resistor. Available in four different end-to-end resistance values (5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ), these low temperature coefficient devices are ideal for high accuracy and stability variable resistance adjustments. The wiper settings are controllable through the I2C compatible digital interface, whic ...

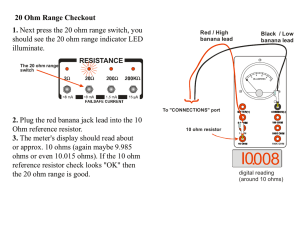

Notes: Intro Circuits & Ohm`s Law

... Example 2: A circuit has three resistors: 6.0 W, 4.0 W and a 12 W resistors in parallel along with a 24 V battery. Draw the circuit. Calculate the total resistance of the circuit. Calculate the total current through the circuit. What is the voltage across each resistor? Calculate the current ...

... Example 2: A circuit has three resistors: 6.0 W, 4.0 W and a 12 W resistors in parallel along with a 24 V battery. Draw the circuit. Calculate the total resistance of the circuit. Calculate the total current through the circuit. What is the voltage across each resistor? Calculate the current ...

Transistor Biasing

... (ii) Minimum proper base-emitter voltage (VBE) at any instant (iii) Minimum proper collector-emitter voltage (VCE) at any instant The conditions (i) and (ii) ensure that base-emitter junction shall remain properly forward biased during all parts of the signal. On the other hand, condition (iii) ensu ...

... (ii) Minimum proper base-emitter voltage (VBE) at any instant (iii) Minimum proper collector-emitter voltage (VCE) at any instant The conditions (i) and (ii) ensure that base-emitter junction shall remain properly forward biased during all parts of the signal. On the other hand, condition (iii) ensu ...

CMOS

Complementary metal–oxide–semiconductor (CMOS) /ˈsiːmɒs/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).The words ""complementary-symmetry"" refer to the fact that the typical design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.Two important characteristics of CMOS devices are high noise immunity and low static power consumption.Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or NMOS logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.The phrase ""metal–oxide–semiconductor"" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond.