Instruction Manual Model 728 Capacitance Meter BOONTON

... 2-7. PULSE BIAS (For specific applications contact the Application Engineering Department, Boonton Electronics.) The internal bias circuit of the 72B needs adequate bypassing of the 1 MHz test signal and therefore may be unsuitable for the application of pulses to bias the test speciment through the ...

... 2-7. PULSE BIAS (For specific applications contact the Application Engineering Department, Boonton Electronics.) The internal bias circuit of the 72B needs adequate bypassing of the 1 MHz test signal and therefore may be unsuitable for the application of pulses to bias the test speciment through the ...

nuclear electronics laboratory manual

... different active electronics components. It starts by introducing small electronics blocks, employing one or more active components. The most demanding exercises instruct a student in the design and construction of complete circuits, as used in commercial nuclear instruments. It is expected that a s ...

... different active electronics components. It starts by introducing small electronics blocks, employing one or more active components. The most demanding exercises instruct a student in the design and construction of complete circuits, as used in commercial nuclear instruments. It is expected that a s ...

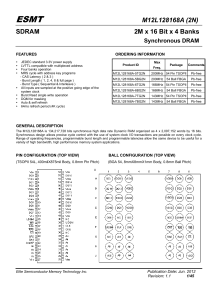

M12L128168A (2N) SDRAM 2M x 16 Bit x 4 Banks

... 5.During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst. New row active of the associated bank can be issued at tRP after the end of burst. 6.Burst stop command is valid at every burst length. 7. ...

... 5.During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst. New row active of the associated bank can be issued at tRP after the end of burst. 6.Burst stop command is valid at every burst length. 7. ...

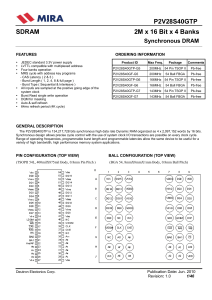

P2V28S40GTP SDRAM 2M x 16 Bit x 4 Banks

... This SDRAM is organized as four independent banks of 2,097,152 words x 16 bits memory arrays. The BA0~BA1 inputs are latched at the time of assertion of RAS and CAS to select the bank to be used for the operation. The banks addressed BA0~BA1 are latched at bank active, read, write, mode register set ...

... This SDRAM is organized as four independent banks of 2,097,152 words x 16 bits memory arrays. The BA0~BA1 inputs are latched at the time of assertion of RAS and CAS to select the bank to be used for the operation. The banks addressed BA0~BA1 are latched at bank active, read, write, mode register set ...

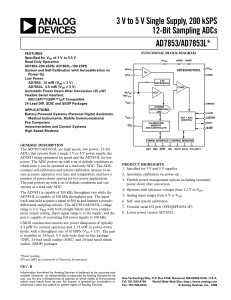

3 V to 5 V Single Supply, 200 kSPS 12

... t14 is derived form the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 100 pF capacitor. This means that the time quoted in the timing characteristics ...

... t14 is derived form the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 100 pF capacitor. This means that the time quoted in the timing characteristics ...

XHRA-2HPA Datasheet

... · Ensure that high speed signals (clocks, USB differential pairs) are routed as far away from off-board connectors as possible. · High-speed clock and periodic signal traces that run parallel should be at least 1.27mm away from USB_DP/USB_DN (see Figure 6). · Low-speed and non-periodic signal traces ...

... · Ensure that high speed signals (clocks, USB differential pairs) are routed as far away from off-board connectors as possible. · High-speed clock and periodic signal traces that run parallel should be at least 1.27mm away from USB_DP/USB_DN (see Figure 6). · Low-speed and non-periodic signal traces ...

www.ko4bb.com

... ripple, but may make loop unstable • Creates parasitic pole: p = 1/(R C2) • C2 < 1/10*C1 for stability • C2 > 1/50*C1 for low jitter • Smoothing cap reduces “IR”-induced VCO jitter to < 0.5% from 5-10% • fvco = KvcoIcpTerr/C2 • Larger C2/C1 increases phase error slightly Copyright, Dennis Fischett ...

... ripple, but may make loop unstable • Creates parasitic pole: p = 1/(R C2) • C2 < 1/10*C1 for stability • C2 > 1/50*C1 for low jitter • Smoothing cap reduces “IR”-induced VCO jitter to < 0.5% from 5-10% • fvco = KvcoIcpTerr/C2 • Larger C2/C1 increases phase error slightly Copyright, Dennis Fischett ...

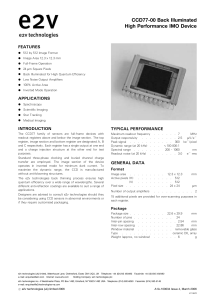

CCD77-00 Back Illuminated High Performance IMO Device

... For transfer to the A register, use the labelling of waveforms on the left of the diagram. Charge is transferred to the register when B13 and TGA are taken from high to low. For transfer to the C register, use the labelling of waveforms on the right of the diagram. Charge is transferred to the regis ...

... For transfer to the A register, use the labelling of waveforms on the left of the diagram. Charge is transferred to the register when B13 and TGA are taken from high to low. For transfer to the C register, use the labelling of waveforms on the right of the diagram. Charge is transferred to the regis ...

LP8550 High-Efficiency LED Backlight Driver for Notebooks (Rev. E)

... Automatic PWM dimming at lower brightness values and current dimming at higher brightness values can be used to improve the optical efficiency. Internal EEPROM is used for storing the configuration data. This makes it possible to have minimum external component count and make the solution very small ...

... Automatic PWM dimming at lower brightness values and current dimming at higher brightness values can be used to improve the optical efficiency. Internal EEPROM is used for storing the configuration data. This makes it possible to have minimum external component count and make the solution very small ...

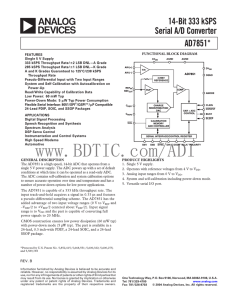

a 14-Bit 333 kSPS Serial A/D Converter AD7851

... The CONVST pulse width will only apply for normal operation. When the part is in power-down mode, a different CONVST pulse width will apply (see PowerDown section). ...

... The CONVST pulse width will only apply for normal operation. When the part is in power-down mode, a different CONVST pulse width will apply (see PowerDown section). ...

Fixed Frequency Current Mode Controller for Flyback Converters

... The NCP1236 includes all necessary features to build a safe and efficient power supply based on a fixed−frequency flyback converter. It is particularly well suited for applications where low part count is a key parameter, without sacrificing safety. • Current−Mode Operation with slope compensation: ...

... The NCP1236 includes all necessary features to build a safe and efficient power supply based on a fixed−frequency flyback converter. It is particularly well suited for applications where low part count is a key parameter, without sacrificing safety. • Current−Mode Operation with slope compensation: ...

Analog-to-Digital and Multivibrators

... • Charge builds up on the left capacitor, “pullingup” the voltage presented to the base of the transistor on the right. • When the base reaches about 0.7v the transistor on the right turns on. • Current now starts to flow through the 1K resistor on the far right, thus dropping the voltage level at t ...

... • Charge builds up on the left capacitor, “pullingup” the voltage presented to the base of the transistor on the right. • When the base reaches about 0.7v the transistor on the right turns on. • Current now starts to flow through the 1K resistor on the far right, thus dropping the voltage level at t ...

CD4027BC Dual J-K Master/Slave Flip

... Dual J-K Master/Slave Flip-Flop with Set and Reset General Description ...

... Dual J-K Master/Slave Flip-Flop with Set and Reset General Description ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.