71M6541DT/71M6541FT/71M6541GT/ Energy Meter ICs 71M6542FT/71M6542GT General Description

... Our Single Converter Technology® with a 22-bit deltasigma ADC, three or four analog inputs, digital temperature compensation, precision voltage reference, and a 32-bit computation engine (CE) support a wide range of metering applications with very few external components. The 71M654xT devices suppor ...

... Our Single Converter Technology® with a 22-bit deltasigma ADC, three or four analog inputs, digital temperature compensation, precision voltage reference, and a 32-bit computation engine (CE) support a wide range of metering applications with very few external components. The 71M654xT devices suppor ...

TDA8025HN

... XTAL1 or from a crystal (fxtal ≤ 26 MHz) connected between pins XTAL1 and XTAL2. The voltage level applied to pin ENCLKIN defines which clock signal is used. When pin ENCLKIN is HIGH, connect the external clock to pin XTAL1. Driving pin ENCLKIN LOW causes the external crystal to generate frequency f ...

... XTAL1 or from a crystal (fxtal ≤ 26 MHz) connected between pins XTAL1 and XTAL2. The voltage level applied to pin ENCLKIN defines which clock signal is used. When pin ENCLKIN is HIGH, connect the external clock to pin XTAL1. Driving pin ENCLKIN LOW causes the external crystal to generate frequency f ...

Subharmonic Mixers in CMOS Microwave Integrated Circuits Bradley Richard Jackson

... Extending the concept of the 2× subharmonic mixer, a 4× subharmonic mixer is proposed that operates in the 12 GHz Ku-band. This circuit is the first 4× subharmonic mixer in CMOS, and achieves a 6 dB conversion gain, which is the highest for any 4× subharmonic mixer regardless of circuit topology or ...

... Extending the concept of the 2× subharmonic mixer, a 4× subharmonic mixer is proposed that operates in the 12 GHz Ku-band. This circuit is the first 4× subharmonic mixer in CMOS, and achieves a 6 dB conversion gain, which is the highest for any 4× subharmonic mixer regardless of circuit topology or ...

MAX9311/MAX9313 1:10 Differential LVPECL/LVECL/HSTL Clock and Data Drivers General Description

... Clock and Data Drivers The MAX9311/MAX9313 are low skew, 1-to-10 differential drivers designed for clock and data distribution. A 2:1 mux selects between the two differential inputs, CLK0, CLK0 and CLK1, CLK1. The 2:1 mux is switched by the single-ended CLKSEL input. A logic low selects the CLK0, CL ...

... Clock and Data Drivers The MAX9311/MAX9313 are low skew, 1-to-10 differential drivers designed for clock and data distribution. A 2:1 mux selects between the two differential inputs, CLK0, CLK0 and CLK1, CLK1. The 2:1 mux is switched by the single-ended CLKSEL input. A logic low selects the CLK0, CL ...

a bist (built-in self-test) strategy for mixed

... digital loop so that the loop test is a digital driven one. In such a way, the test can be moved from the mixed-signal domain to the digital domain which is much easier and more cost-effective. According to the different resolution of the ADC or the DAC, the loop and the sequence of the testing step ...

... digital loop so that the loop test is a digital driven one. In such a way, the test can be moved from the mixed-signal domain to the digital domain which is much easier and more cost-effective. According to the different resolution of the ADC or the DAC, the loop and the sequence of the testing step ...

CSE 241A / ECE 260B, Winter 2003 UCSD

... Timing analysis can be guardbanded by scaling the coupling capacitance by a “Miller Coupling Factor” to account for push-in or push-out. Homework Q3: (a) explain upper and lower bounds on the Miller Coupling Factor for a victim wire that is between two parallel aggressor wires, assuming step transit ...

... Timing analysis can be guardbanded by scaling the coupling capacitance by a “Miller Coupling Factor” to account for push-in or push-out. Homework Q3: (a) explain upper and lower bounds on the Miller Coupling Factor for a victim wire that is between two parallel aggressor wires, assuming step transit ...

Interval Arithmetic Based Input Vector Control for RTL Subthreshold

... As IVC has little delay penalty, many researchers have proposed using IVC leakage power minimization. To the best of our knowledge, these techniques are at the logic level. Abdollahi, Fallah, and Pedram [6] propose gate-level leakage reduction with two techniques. The first technique is an input vec ...

... As IVC has little delay penalty, many researchers have proposed using IVC leakage power minimization. To the best of our knowledge, these techniques are at the logic level. Abdollahi, Fallah, and Pedram [6] propose gate-level leakage reduction with two techniques. The first technique is an input vec ...

35% Wiring

... The source of light is typically a argon-flouride laser The light passes through an array of lenses to reach the silicon substrate The resolution limit is given by: R = k1λ / NA ...

... The source of light is typically a argon-flouride laser The light passes through an array of lenses to reach the silicon substrate The resolution limit is given by: R = k1λ / NA ...

Zynq-7000 All Programmable SoC PCB Design and Pin Planning Guide

... A via is a piece of metal making an electrical connection between two or more points in the Z space of a PCB. V ias carry signals or power between layers of a PCB. In current plated-through-hole (PTH) te chnology, a via is formed by plating the inner surface of a hole drilled thr ough the PCB. In cu ...

... A via is a piece of metal making an electrical connection between two or more points in the Z space of a PCB. V ias carry signals or power between layers of a PCB. In current plated-through-hole (PTH) te chnology, a via is formed by plating the inner surface of a hole drilled thr ough the PCB. In cu ...

IEANNNI /

... maintaining means 56, and a logical OR circuit 57. The time constant means 51 raises or drops a voltage V0 (hereinafter, referred to simply as V0) over time. The ?rst voltage generating means 52 generates a constant voltage V1 (hereinafter, referred to simply as V1), and the second voltage generatin ...

... maintaining means 56, and a logical OR circuit 57. The time constant means 51 raises or drops a voltage V0 (hereinafter, referred to simply as V0) over time. The ?rst voltage generating means 52 generates a constant voltage V1 (hereinafter, referred to simply as V1), and the second voltage generatin ...

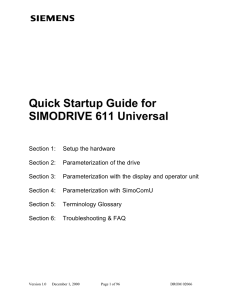

611U Quick Startup Guide V1.0

... Now you can power-up the drive. The following run-up should appear. For troubleshooting see ...

... Now you can power-up the drive. The following run-up should appear. For troubleshooting see ...

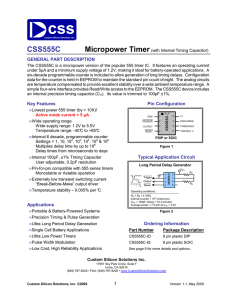

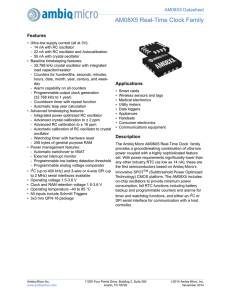

Datasheet - Ambiq Micro

... 4.2. Power Supply Parameters ................................................................................................... 14 ...

... 4.2. Power Supply Parameters ................................................................................................... 14 ...

Virtex-II XC2V40/XC2V1000NM Reference Board

... The Virtex-II Development Kit provides an easy to use development platform for prototyping and verifying Virtex-II based designs. The Virtex-II family is a platform FPGA developed for high performance, low to high-density designs utilizing IP cores and customized modules. The Virtex-II family delive ...

... The Virtex-II Development Kit provides an easy to use development platform for prototyping and verifying Virtex-II based designs. The Virtex-II family is a platform FPGA developed for high performance, low to high-density designs utilizing IP cores and customized modules. The Virtex-II family delive ...

RIGOL User’s Guide DM3068 Feb. 2014

... In order to prevent electric shock, DM3068 provides overvoltage protection for line-voltage mains connections meeting both of the following conditions: 1. The HI and LO input terminals are connected to the mains under Measurement Category II conditions, defined below. 2. The mains are limited to a m ...

... In order to prevent electric shock, DM3068 provides overvoltage protection for line-voltage mains connections meeting both of the following conditions: 1. The HI and LO input terminals are connected to the mains under Measurement Category II conditions, defined below. 2. The mains are limited to a m ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.