Design Techniques for 50GS/s ADC

... clocks in the entire sampler system are the 4 12.8GS/s clocks of the font-end samplers (Rank-1). An additional benefit of hierarchical sampling is the greatly reduced signal routing at the output of the front-end buffer; since it can limit the input bandwidth of the entire ADC, the bandwidth of this ...

... clocks in the entire sampler system are the 4 12.8GS/s clocks of the font-end samplers (Rank-1). An additional benefit of hierarchical sampling is the greatly reduced signal routing at the output of the front-end buffer; since it can limit the input bandwidth of the entire ADC, the bandwidth of this ...

Reduction of Peak Input Currents during Charge Pump

... however, we use a control circuit that continuously adjusts the clock frequency of the charge pump depending on the difference between the actual and desired value of the output voltage of the programmable charge pump. Therefore, the charge pump will use its maximum available clock frequency during ...

... however, we use a control circuit that continuously adjusts the clock frequency of the charge pump depending on the difference between the actual and desired value of the output voltage of the programmable charge pump. Therefore, the charge pump will use its maximum available clock frequency during ...

Programmable 27-Bit Parallel-to-Serial Receiver

... When receiving, the PLL locks to the incoming clock, CLK, and generates an internal high-speed clock at the line rate of the data lines. The data is serially loaded into a shift register using the internal high-speed clock. The deserialized data is presented on the parallel output bus with a recreat ...

... When receiving, the PLL locks to the incoming clock, CLK, and generates an internal high-speed clock at the line rate of the data lines. The data is serially loaded into a shift register using the internal high-speed clock. The deserialized data is presented on the parallel output bus with a recreat ...

Solution

... Here, fout = 2(NP + S)fREF . Thus, a channel spacing of fch dictates fREF = fch=2. The lock speed and the loop bandwidth are therefore scaled down by a factor of two, making the VCO phase noise more pronounced. One advantage of this approach is that the reference sideband lies at the edge of the adj ...

... Here, fout = 2(NP + S)fREF . Thus, a channel spacing of fch dictates fREF = fch=2. The lock speed and the loop bandwidth are therefore scaled down by a factor of two, making the VCO phase noise more pronounced. One advantage of this approach is that the reference sideband lies at the edge of the adj ...

ZW0201

... block includes a battery monitoring mode (no external connections needed). This mode is not supported by the API in Developers Kit v4.1x. The ADC supports both single and (continuous) multi conversion mode. It has a built-in comparator for generating interrupts when a threshold set by SW is exceeded ...

... block includes a battery monitoring mode (no external connections needed). This mode is not supported by the API in Developers Kit v4.1x. The ADC supports both single and (continuous) multi conversion mode. It has a built-in comparator for generating interrupts when a threshold set by SW is exceeded ...

USB-1408FS User`s Guide

... To connect the USB-1408FS to your system, connect the USB cable to a USB port on your computer or to an external USB hub that is connected to your computer. The USB cable provides power and communication to the USB-1408FS. The USB-1408FS installs as a composite device with separate devices attached. ...

... To connect the USB-1408FS to your system, connect the USB cable to a USB port on your computer or to an external USB hub that is connected to your computer. The USB cable provides power and communication to the USB-1408FS. The USB-1408FS installs as a composite device with separate devices attached. ...

MAX3676 622Mbps, 3.3V Clock-Recovery and Data-Retiming IC with Limiting Amplifier General Description

... into the MAX3676 to remove the input offset. DC-coupling to the ADI+ and ADI- inputs is not allowed, as this would prevent the proper functioning of the DC offsetcorrection circuitry. The differential input impedance (ZIN) is approximately 2.5kΩ. The impedance between OLC+ and OLC- (ZOLC) is approxi ...

... into the MAX3676 to remove the input offset. DC-coupling to the ADI+ and ADI- inputs is not allowed, as this would prevent the proper functioning of the DC offsetcorrection circuitry. The differential input impedance (ZIN) is approximately 2.5kΩ. The impedance between OLC+ and OLC- (ZOLC) is approxi ...

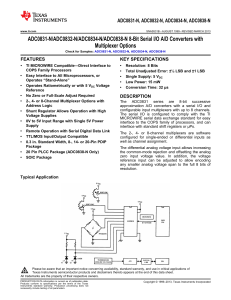

ADC0831/832/834/838 8-Bit Serial I/O ADCs w

... A 40% to 60% clock duty cycle range insures proper operation at all clock frequencies. In the case that an available clock has a duty cycle outside of these limits, the minimum, time the clock is high or the minimum time the clock is low must be at least 1 μs. The maximum time the clock can be high ...

... A 40% to 60% clock duty cycle range insures proper operation at all clock frequencies. In the case that an available clock has a duty cycle outside of these limits, the minimum, time the clock is high or the minimum time the clock is low must be at least 1 μs. The maximum time the clock can be high ...

FireSignal – towards remote participation

... ability of the instrument to repeat the measurement of a constant value. More precise measurements have less random error. ...

... ability of the instrument to repeat the measurement of a constant value. More precise measurements have less random error. ...

LMC555 CMOS Timer

... The LMC555 is a CMOS version of the industry standard 555 series general purpose timers. In addition to the standard package (SOIC, MSOP, and MDIP) the LMC555 is also available in a chip sized package (8 Bump micro SMD) using National's micro SMD package technology. The LMC555 offers the same capabi ...

... The LMC555 is a CMOS version of the industry standard 555 series general purpose timers. In addition to the standard package (SOIC, MSOP, and MDIP) the LMC555 is also available in a chip sized package (8 Bump micro SMD) using National's micro SMD package technology. The LMC555 offers the same capabi ...

Selecting an A/D Converter (Rev. A)

... the analog front end an error budget of one LSB (least significant bit). One good rule of thumb to follow when selecting analog components for a digitizing system is for each component to be five to ten times more accurate than the total system accuracy. Resolution should not be confused with accura ...

... the analog front end an error budget of one LSB (least significant bit). One good rule of thumb to follow when selecting analog components for a digitizing system is for each component to be five to ten times more accurate than the total system accuracy. Resolution should not be confused with accura ...

MAX1193 Ultra-Low-Power, 45Msps, Dual 8-Bit ADC General Description Features

... www.BDTIC.com/maxim ...

... www.BDTIC.com/maxim ...

TSC2017 数据资料 dataSheet 下载

... controller designed to work with power-sensitive, handheld applications that are based on an advanced low-voltage processor. It works with a supply voltage as low as 1.6V, which can be supplied by a single-cell battery. It contains a complete, ultra-low power, 12-bit, analog-to-digital (A/D) resisti ...

... controller designed to work with power-sensitive, handheld applications that are based on an advanced low-voltage processor. It works with a supply voltage as low as 1.6V, which can be supplied by a single-cell battery. It contains a complete, ultra-low power, 12-bit, analog-to-digital (A/D) resisti ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.