TPS40060 数据资料 dataSheet 下载

... The SW node of the converter will be negative during the dead time when both the upper and lower MOSFETs are off. The magnitude of this negative voltage is dependent on the lower MOSFET body diode and the output current which flows during this dead time. This negative voltage could affect the operat ...

... The SW node of the converter will be negative during the dead time when both the upper and lower MOSFETs are off. The magnitude of this negative voltage is dependent on the lower MOSFET body diode and the output current which flows during this dead time. This negative voltage could affect the operat ...

AN420

... Occasionally the analog signal provided by external sensors require an Analog to Digital conversion with a resolution of greater than 8 bits. In order to extract the full information for subsequent data processing within the microcontroller a higher resolution Analog to Digital is thus required. The ...

... Occasionally the analog signal provided by external sensors require an Analog to Digital conversion with a resolution of greater than 8 bits. In order to extract the full information for subsequent data processing within the microcontroller a higher resolution Analog to Digital is thus required. The ...

Frequency compensated LC networks for oscillators with the wide

... voltage input minimizes loading of the parallel LC network output, while the current output minimizes loading of the LC circuit input. A FET or a vacuum tube active device is a good example of such an amplifier, a FET cascode or a pentode tube gets even closer. In simulations I replaced the amplifie ...

... voltage input minimizes loading of the parallel LC network output, while the current output minimizes loading of the LC circuit input. A FET or a vacuum tube active device is a good example of such an amplifier, a FET cascode or a pentode tube gets even closer. In simulations I replaced the amplifie ...

packaging_test_pratices

... Repeat for all possible stuck at zero/one faults Requires long simulation times !. Toggle test ( counts how many times each node has changed) can be used to get a first impression of fault coverage. ...

... Repeat for all possible stuck at zero/one faults Requires long simulation times !. Toggle test ( counts how many times each node has changed) can be used to get a first impression of fault coverage. ...

MAX2620 10MHz to 1050MHz Integrated RF Oscillator with Buffered Outputs _________________General Description

... The value of CSTRAY is based on approximate performance of the MAX2620 EV kit. Values of C3 and C4 are chosen to minimize Rn (Equation 2) while not loading the resonant circuit with excessive capacitance. C03 and C04 are parasitic capacitors. The varactor’s capacitance range should allow for the des ...

... The value of CSTRAY is based on approximate performance of the MAX2620 EV kit. Values of C3 and C4 are chosen to minimize Rn (Equation 2) while not loading the resonant circuit with excessive capacitance. C03 and C04 are parasitic capacitors. The varactor’s capacitance range should allow for the des ...

FT7511 Reset Timer with Fixed Delay and Reset Pulse

... LOW for factory testing. The DSR pin MUST be forced to GND during normal operation. The DSR pin should never be driven HIGH or left to float during normal operation. The DSR pin state should never be changed during device operation; it must be biased prior to supplying the VCC supply. If there is a ...

... LOW for factory testing. The DSR pin MUST be forced to GND during normal operation. The DSR pin should never be driven HIGH or left to float during normal operation. The DSR pin state should never be changed during device operation; it must be biased prior to supplying the VCC supply. If there is a ...

差分放大器系列AD8323 数据手册DataSheet 下载

... Interface Specifications) certified cable modems and CATV settop boxes. Upstream data is modulated in QPSK or QAM format, and done with DSP or a dedicated QPSK/QAM modulator. The amplifier receives its input signal from the QPSK/QAM modulator or from a DAC. In either case the signal must be low-pass ...

... Interface Specifications) certified cable modems and CATV settop boxes. Upstream data is modulated in QPSK or QAM format, and done with DSP or a dedicated QPSK/QAM modulator. The amplifier receives its input signal from the QPSK/QAM modulator or from a DAC. In either case the signal must be low-pass ...

TSC2000 数据资料 dataSheet 下载

... panel resistance in the X+ lead does not affect the conversion due to the high input impedance of the A/D converter. Voltage is then applied to the other axis, and the A/D converter converts the voltage representing the X-position on the screen. This provides the X- and Y-coordinates to the associat ...

... panel resistance in the X+ lead does not affect the conversion due to the high input impedance of the A/D converter. Voltage is then applied to the other axis, and the A/D converter converts the voltage representing the X-position on the screen. This provides the X- and Y-coordinates to the associat ...

AD7641 数据手册DataSheet下载

... When MODE[1:0] = 0 (18-bit interface mode), this pin is Bit 0 of the parallel port data output bus and the data coding is straight binary. In all other modes, this pin allows the choice of straight binary/twos complement. When OB/2C is high, the digital output is straight binary; when low, the MSB i ...

... When MODE[1:0] = 0 (18-bit interface mode), this pin is Bit 0 of the parallel port data output bus and the data coding is straight binary. In all other modes, this pin allows the choice of straight binary/twos complement. When OB/2C is high, the digital output is straight binary; when low, the MSB i ...

AD7843

... However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent right ...

... However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent right ...

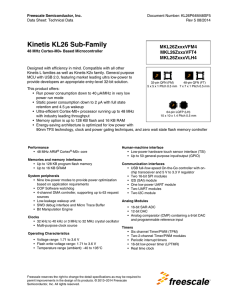

Kinetis KL26: 48MHz Cortex-M0+ 32-128KB Flash 32-64pin

... 1. All I/O pins are internally clamped to VSS through a ESD protection diode. There is no diode connection to VDD. If VIN greater than VIO_MIN (= VSS-0.3 V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed then a current limiting ...

... 1. All I/O pins are internally clamped to VSS through a ESD protection diode. There is no diode connection to VDD. If VIN greater than VIO_MIN (= VSS-0.3 V) is observed, then there is no need to provide current limiting resistors at the pads. If this limit cannot be observed then a current limiting ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.