asynchronous design in vlsi

... known as two phase protocol .both request and acknowledgment signal are implemented by voltages at different levels at different wires .in this protocol we don’t make any distinction between direction of voltage signals . Both rising and falling transition denote a single transition event. This prot ...

... known as two phase protocol .both request and acknowledgment signal are implemented by voltages at different levels at different wires .in this protocol we don’t make any distinction between direction of voltage signals . Both rising and falling transition denote a single transition event. This prot ...

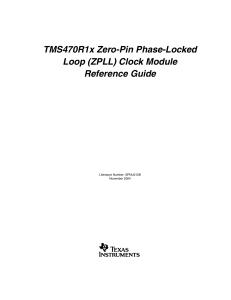

TMS470R1x Zero-Pin Phase-Locked Loop

... TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and application s using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safegua ...

... TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and application s using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safegua ...

ELEC 5970-001/6970-001 Special Topics in Electrical Engineering

... change to 1, necessary and sufficient condition is that both inputs have completed their 0 to 1 transitions. Thus, the first output transition is caused by two input transitions, one on each input. This subtracts 1 from the above upper bound. Next, consider the last transition at the output. The las ...

... change to 1, necessary and sufficient condition is that both inputs have completed their 0 to 1 transitions. Thus, the first output transition is caused by two input transitions, one on each input. This subtracts 1 from the above upper bound. Next, consider the last transition at the output. The las ...

Crocodile Clips - Junior University :: Homepage

... Construct simple circuits using crocodile clips. Make informed decisions over the choice of switches used in electronics circuits through practical experience of their operation. Incorporate logic gates as a means of controlling decisions within basic circuits. Discover ways of monitoring ci ...

... Construct simple circuits using crocodile clips. Make informed decisions over the choice of switches used in electronics circuits through practical experience of their operation. Incorporate logic gates as a means of controlling decisions within basic circuits. Discover ways of monitoring ci ...

`Flash` Analog-to-Digital Conversion

... represents the value of the voltage (or current) is known as an analog-to-digital converter (ADC). There are a number of different circuit topologies that perform ADC, each with its own set of advantages and disadvantages. The ‘flash’ ADC topology has the advantage that when a new analog voltage is ...

... represents the value of the voltage (or current) is known as an analog-to-digital converter (ADC). There are a number of different circuit topologies that perform ADC, each with its own set of advantages and disadvantages. The ‘flash’ ADC topology has the advantage that when a new analog voltage is ...

DATA SHEET For a complete data sheet, please also download:

... delay occurs when output Q goes HIGH (in the triggered start mode, the previously disabled oscillator will start-up). After the programmed time delay, the flip-flop stages are reset and the output returns to its original state. ...

... delay occurs when output Q goes HIGH (in the triggered start mode, the previously disabled oscillator will start-up). After the programmed time delay, the flip-flop stages are reset and the output returns to its original state. ...

g Accelerometers ADXL278 i

... The fixed fingers in the forcing cells are normally kept at the same potential as that of the movable frame. When the self-test digital input is activated, the voltage on the fixed fingers on one side of the moving plate in the forcing cells is changed. This creates an attractive electrostatic force ...

... The fixed fingers in the forcing cells are normally kept at the same potential as that of the movable frame. When the self-test digital input is activated, the voltage on the fixed fingers on one side of the moving plate in the forcing cells is changed. This creates an attractive electrostatic force ...

Aquaboy Deluxe - MadBeanPedals

... Please keep in mind that these evaluations are in degrees, not absolutes. IOW, it is entirely possible to build the ABDX with the v3205 to get the max delay and still get a very acceptable amount of fidelity (the design has mods to help with this). It’s just never going to sound as good as the MN300 ...

... Please keep in mind that these evaluations are in degrees, not absolutes. IOW, it is entirely possible to build the ABDX with the v3205 to get the max delay and still get a very acceptable amount of fidelity (the design has mods to help with this). It’s just never going to sound as good as the MN300 ...

ADuC812 FAQs

... A: MicroConverters can be serially reprogrammed in your system using Analog Devices’ Windows based download program (WSD.exe) to communicate through the chip’s UART. Alternatively, you can in-system-reprogram the MicroConverter from any other host processor using the same serial download protocol us ...

... A: MicroConverters can be serially reprogrammed in your system using Analog Devices’ Windows based download program (WSD.exe) to communicate through the chip’s UART. Alternatively, you can in-system-reprogram the MicroConverter from any other host processor using the same serial download protocol us ...

CERN/EP/ATE/DQ TTCvx _____________________________________________________________________________________

... LHC machine together with trigger and control information (L1A, BCR, ECR etc.) from the Central Trigger Processor to the sub-detector Read-Out Buffers and Front End systems. The two communications channels: A, carrying the L1A trigger, and B, carrying the control address/data or command packets, are ...

... LHC machine together with trigger and control information (L1A, BCR, ECR etc.) from the Central Trigger Processor to the sub-detector Read-Out Buffers and Front End systems. The two communications channels: A, carrying the L1A trigger, and B, carrying the control address/data or command packets, are ...

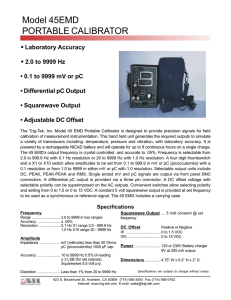

Pulse Generator HM8035

... features are the short rise time output, better than 3ns and typically 2ns and the flexibility of pulse duration and duty cycle from square-wave through to narrow, sliver-type pulses. Rise and fall time remain constant while the pulse width is modified. The instrument also offers manual triggered pu ...

... features are the short rise time output, better than 3ns and typically 2ns and the flexibility of pulse duration and duty cycle from square-wave through to narrow, sliver-type pulses. Rise and fall time remain constant while the pulse width is modified. The instrument also offers manual triggered pu ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.