ECE 6332: VLSI Design Project Review 1 Chunhu Zhang and Yu

... The direct amplification method (1) has some intrinsic drawbacks in that it is more vulnerable to the nonrandom influences coupled into the white noise source. The nonrandom influence must be at least an order of magnitude below the random noise source for the direct amplification technique to maint ...

... The direct amplification method (1) has some intrinsic drawbacks in that it is more vulnerable to the nonrandom influences coupled into the white noise source. The nonrandom influence must be at least an order of magnitude below the random noise source for the direct amplification technique to maint ...

74VHC4040 12-Stage Binary Counter 74VHC4040 12-Sta

... The VHC4040 is an advanced high-speed CMOS device fabricated with silicon gate CMOS technology. It achieves the high-speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation. The VHC4040 is a 12-stage counter which increments on the negative edge of ...

... The VHC4040 is an advanced high-speed CMOS device fabricated with silicon gate CMOS technology. It achieves the high-speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation. The VHC4040 is a 12-stage counter which increments on the negative edge of ...

MAX1248/MAX1249 +2.7V to +5.25V, Low-Power, 4-Channel, Serial 10-Bit ADCs in QSOP-16 _______________General Description

... The sampling architecture of the ADC’s analog comparator is illustrated in the equivalent input circuit (Figure 4). In single-ended mode, IN+ is internally switched to CH0–CH3, and IN- is switched to COM. In differential mode, IN+ and IN- are selected from two pairs: CH0/CH1 and CH2/CH3. Configure t ...

... The sampling architecture of the ADC’s analog comparator is illustrated in the equivalent input circuit (Figure 4). In single-ended mode, IN+ is internally switched to CH0–CH3, and IN- is switched to COM. In differential mode, IN+ and IN- are selected from two pairs: CH0/CH1 and CH2/CH3. Configure t ...

MAX186/MAX188 Low-Power, 8-Channel, Serial 12-Bit ADCs General Description

... Note 1: Tested at VDD = 5.0V; VSS = 0V; unipolar input mode. Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has been calibrated. Note 3: MAX186 – internal reference, offset nulled; MAX188 – external reference (VREF = + ...

... Note 1: Tested at VDD = 5.0V; VSS = 0V; unipolar input mode. Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has been calibrated. Note 3: MAX186 – internal reference, offset nulled; MAX188 – external reference (VREF = + ...

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE)

... and significantly broadened the frequency range of the amplifier. After two stage amplification of the signal has certain amplitude, the influence of the working points can be avoided by using the resistance capacitance coupling. The third stage emitter follower amplification quantity is 1; its main ...

... and significantly broadened the frequency range of the amplifier. After two stage amplification of the signal has certain amplitude, the influence of the working points can be avoided by using the resistance capacitance coupling. The third stage emitter follower amplification quantity is 1; its main ...

Ee316_4

... integrator ramps up (known as deintegrate phase) until v2 again reaches CMP threshold CMP output toggles and signals Control Logic to stop Counter issue EOC (end-of-conversion) command Accumulated count, N V v2 REF NTCLK RC Conversion ...

... integrator ramps up (known as deintegrate phase) until v2 again reaches CMP threshold CMP output toggles and signals Control Logic to stop Counter issue EOC (end-of-conversion) command Accumulated count, N V v2 REF NTCLK RC Conversion ...

CONTACTLESS DIAGNOSTICS OF THIN FILM LAYERS Vaclav Papez Stanislava Papezova

... comparator. The synchronizing impulse is generated in time, when the output signal of differentiator is passing through the zero level, and it corresponds to the peak of the output signal of differential amplifier. Just in time of synchronization pulse, the immediate frequency of sweeping generator ...

... comparator. The synchronizing impulse is generated in time, when the output signal of differentiator is passing through the zero level, and it corresponds to the peak of the output signal of differential amplifier. Just in time of synchronization pulse, the immediate frequency of sweeping generator ...

DS90CR281/DS90CR282 28-Bit Channel Link General Description

... The high-speed transport of LVDS signals has been demonstrated on several types of cables with excellent results. However, the best overall performance has been seen when using Twin-Coax cable. Twin-Coax has very low cable skew and EMI due to its construction and double shielding. All of the design ...

... The high-speed transport of LVDS signals has been demonstrated on several types of cables with excellent results. However, the best overall performance has been seen when using Twin-Coax cable. Twin-Coax has very low cable skew and EMI due to its construction and double shielding. All of the design ...

DM74LS123 Dual Retriggerable One

... to reduce I-R and Ldi/dt voltage developed along their connecting paths. If the lead length from CX to pins (6) and (7) or pins (14) and (15) is greater than 3 cm, for example, the output pulse width might be quite different from values predicted from the appropriate equations. A non-inductive and l ...

... to reduce I-R and Ldi/dt voltage developed along their connecting paths. If the lead length from CX to pins (6) and (7) or pins (14) and (15) is greater than 3 cm, for example, the output pulse width might be quite different from values predicted from the appropriate equations. A non-inductive and l ...

... The concept of indication or acknowledgement plays an important role in the design of asynchronous circuits for synchronization. Muller C-element is a state-holding element much like an asynchronous set-reset latch [1]. When both inputs are 0 the output is set to 0, and when both inputs are 1 the ou ...

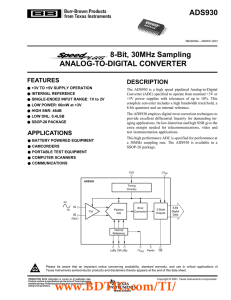

ADS930 数据资料 dataSheet 下载

... two-bit quantizer stage converts on the edge of the subclock, which is the same frequency of the externally applied clock. The output of each quantizer is fed into its own delay line to time-align it with the data created from the subsequent quantizer stages. This aligned data is fed into a digital ...

... two-bit quantizer stage converts on the edge of the subclock, which is the same frequency of the externally applied clock. The output of each quantizer is fed into its own delay line to time-align it with the data created from the subsequent quantizer stages. This aligned data is fed into a digital ...

DS1672 I C 32-Bit Binary Counter RTC

... capacitance (CL) of 6pF. For more information about crystal selection and crystal layout considerations, refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks. The DS1672 can also be driven by an external 32.768kHz oscillator. In this configuration, the X1 pin is connecte ...

... capacitance (CL) of 6pF. For more information about crystal selection and crystal layout considerations, refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks. The DS1672 can also be driven by an external 32.768kHz oscillator. In this configuration, the X1 pin is connecte ...

Data Sheet (current)

... ECLinPS is a trademark of Semiconductor Components Industries, LLC (SCILLC) ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, represen ...

... ECLinPS is a trademark of Semiconductor Components Industries, LLC (SCILLC) ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, represen ...

ADS5413-11 数据资料 dataSheet 下载

... The ADS5413−11 is a 11-bit pipeline ADC. Its low power (400 mW) at 65 MSPS and high sampling rate is achieved using a state-of-the-art switched capacitor pipeline architecture built on an advanced low-voltage CMOS process. The ADS5413−11 analog core operates from a 3.3 V supply consuming most of the ...

... The ADS5413−11 is a 11-bit pipeline ADC. Its low power (400 mW) at 65 MSPS and high sampling rate is achieved using a state-of-the-art switched capacitor pipeline architecture built on an advanced low-voltage CMOS process. The ADS5413−11 analog core operates from a 3.3 V supply consuming most of the ...

Evaluation Board User Guide UG-073

... By default, the evaluation board is set up to have a clock input on J10 that is distributed on the evaluation board via the clock distribution IC AD9512. One output of the AD9512 is configured to be used as a DAC clock input and a data clock input for the AD911x or AD971x while another one is intend ...

... By default, the evaluation board is set up to have a clock input on J10 that is distributed on the evaluation board via the clock distribution IC AD9512. One output of the AD9512 is configured to be used as a DAC clock input and a data clock input for the AD911x or AD971x while another one is intend ...

Dithering Digital Ripple Correlation Control for Maximum Power

... the highest DC measurement precision Noise-free resolution is DC equivalent of ENOB for AC RMS value of the measurement noise equal to standard deviation assuming noise source near ...

... the highest DC measurement precision Noise-free resolution is DC equivalent of ENOB for AC RMS value of the measurement noise equal to standard deviation assuming noise source near ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.