A Phase Interpolator CDR with Low-Voltage CML Circuits ..........Li

... CML circuits are the most popular for high speed applications. They can operate with low signal voltage at a low supply voltage and operate with higher operating frequency than CMOS circuits. CML circuit uses the differential signal which generated from differential stage is more linear than those f ...

... CML circuits are the most popular for high speed applications. They can operate with low signal voltage at a low supply voltage and operate with higher operating frequency than CMOS circuits. CML circuit uses the differential signal which generated from differential stage is more linear than those f ...

DS1123L 3.3V, 8-Bit, Programmable Timing Element General Description Features

... When LE is set at a high logic level, it enables the register and CLK clocks the data, D, into the register one bit at a time starting with the most significant bit. After all 8 bits are shifted into the DS1123L, LE is pulled low to end the data transfer and activate the new value. A settling time ( ...

... When LE is set at a high logic level, it enables the register and CLK clocks the data, D, into the register one bit at a time starting with the most significant bit. After all 8 bits are shifted into the DS1123L, LE is pulled low to end the data transfer and activate the new value. A settling time ( ...

AVR352: Using the Coulomb Counting ADC

... synchronization. A CC-ADC update busy bit, CADUB, can be used to check if an update is in progress or not. 2.1.1 Instantaneous Current Conversion mode (ICC-mode) In ICC-mode the CC-ADC provides a 13 bit signed result in approximately 3.9ms. This mode can be used when it is desired to get information ...

... synchronization. A CC-ADC update busy bit, CADUB, can be used to check if an update is in progress or not. 2.1.1 Instantaneous Current Conversion mode (ICC-mode) In ICC-mode the CC-ADC provides a 13 bit signed result in approximately 3.9ms. This mode can be used when it is desired to get information ...

DS1302 数据手册DataSheet 在线下载

... next eight SCLK cycles. Note that the first data bit to be transmitted occurs on the first falling edge after the last bit of the command byte is written. Additional SCLK cycles retransmit the data bytes should they inadvertently occur so long as CE remains high. This operation permits continuous bu ...

... next eight SCLK cycles. Note that the first data bit to be transmitted occurs on the first falling edge after the last bit of the command byte is written. Additional SCLK cycles retransmit the data bytes should they inadvertently occur so long as CE remains high. This operation permits continuous bu ...

MC68194 Carrier Band Modem (CBM)

... Figure 1−4. Phase−Coherent Modulation Scheme 1.3 MESSAGE (FRAME) FORMAT ...

... Figure 1−4. Phase−Coherent Modulation Scheme 1.3 MESSAGE (FRAME) FORMAT ...

- aes journals

... entire ADC. Two stage register offset averaging achieves ENOB of 3.71 bits. Hence no calibration is required. In this paper architecture of the proposed ADC is presented in section II. Comparator array is described in section III. Encoder design is discussed in section IV. Simulation results are giv ...

... entire ADC. Two stage register offset averaging achieves ENOB of 3.71 bits. Hence no calibration is required. In this paper architecture of the proposed ADC is presented in section II. Comparator array is described in section III. Encoder design is discussed in section IV. Simulation results are giv ...

Principles of Electronic Communication Systems

... Crystal oscillators provide highly accurate frequencies and their stability is superior to LC oscillators. The frequency of a crystal oscillator can be varied by changing the value of capacitance in series or parallel with the crystal. By making the series capacitance a varactor diode, frequency ...

... Crystal oscillators provide highly accurate frequencies and their stability is superior to LC oscillators. The frequency of a crystal oscillator can be varied by changing the value of capacitance in series or parallel with the crystal. By making the series capacitance a varactor diode, frequency ...

Encoders Frequently Asked Questions

... encoder, you should follow a few simple rules. Make sure that you do not choose a PPR that will exceed the maximum input frequency of the controller (or whatever device the encoder is driving). To calculate the max frequency of the encoder signal (in Hz): simply multiply the speed that the encoder w ...

... encoder, you should follow a few simple rules. Make sure that you do not choose a PPR that will exceed the maximum input frequency of the controller (or whatever device the encoder is driving). To calculate the max frequency of the encoder signal (in Hz): simply multiply the speed that the encoder w ...

AN-1002 APPLICATION NOTE

... phase-lock loop (PLL). The solution is based on Nicholls and Carleton’s paper and demonstrates the ability to provide holdover stability of 0.017 ppb (a CTE of 1.5 μs/day) using an OCXO with a stability of 0.45 ppb (a CTE of 38.9 μs/day). Note that the 0.45 ppb OCXO stability comes from 0.4 ppb for ...

... phase-lock loop (PLL). The solution is based on Nicholls and Carleton’s paper and demonstrates the ability to provide holdover stability of 0.017 ppb (a CTE of 1.5 μs/day) using an OCXO with a stability of 0.45 ppb (a CTE of 38.9 μs/day). Note that the 0.45 ppb OCXO stability comes from 0.4 ppb for ...

ECCE

... scissors. Microsurgery offers the advantage of minimal tissue trauma, precise surgery and better surgical results. ...

... scissors. Microsurgery offers the advantage of minimal tissue trauma, precise surgery and better surgical results. ...

Sensor Array 742 x 554 Pixels Frame Buffer

... gration capacitor C1 occurs at the beginning of each clock cycle and the sense amp then sits open waiting for bitline current to present itself anywhere within the 10ns cycle time. The integration capacitor holds the bitline current even after the word line goes low. This current is integrated on th ...

... gration capacitor C1 occurs at the beginning of each clock cycle and the sense amp then sits open waiting for bitline current to present itself anywhere within the 10ns cycle time. The integration capacitor holds the bitline current even after the word line goes low. This current is integrated on th ...

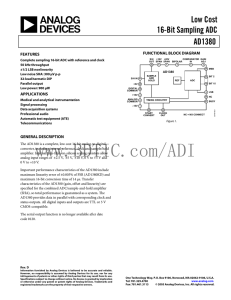

AD1380 数据手册DataSheet 下载

... gain and ±0.05% FSR for offset. These errors may be trimmed to zero by the use of external trim circuits as shown in Figure 3 and Figure 4. Linearity error is defined for unipolar ranges as the deviation from a true straight line transfer characteristic from a zero voltage analog input, which calls ...

... gain and ±0.05% FSR for offset. These errors may be trimmed to zero by the use of external trim circuits as shown in Figure 3 and Figure 4. Linearity error is defined for unipolar ranges as the deviation from a true straight line transfer characteristic from a zero voltage analog input, which calls ...

Digital Transmission

... not desirable because the DC component does not pass through some components of a communication system such as a transformer. This leads to distortion of the signal and may create error at the output. The DC component also results in unwanted energy loss on the line. So a good line coding scheme sho ...

... not desirable because the DC component does not pass through some components of a communication system such as a transformer. This leads to distortion of the signal and may create error at the output. The DC component also results in unwanted energy loss on the line. So a good line coding scheme sho ...

Elite Sttes stem 98%

... A voltage to frequency converter 34 is connected to receive Still another object is to accomplish the foregoing in a 45 the output on line 32 and provides a frequency output fl on line 36 where f1 = k, The voltage to frequency converter manner which is compatible for use with either analog or 34 may ...

... A voltage to frequency converter 34 is connected to receive Still another object is to accomplish the foregoing in a 45 the output on line 32 and provides a frequency output fl on line 36 where f1 = k, The voltage to frequency converter manner which is compatible for use with either analog or 34 may ...

APPLICATION NOTE AN/96031 TDA8790M EVALUATION BOARD DOCUMENTATION

... of the main TDA8790 characteristics. It is realized with a two layer PCB. The following features are included : - One single power supply (+8V +/-10%) is required to generate the supplies needed by the on-board ICs. Connection via banana plugs or grips is possible. To avoid supply connection errors, ...

... of the main TDA8790 characteristics. It is realized with a two layer PCB. The following features are included : - One single power supply (+8V +/-10%) is required to generate the supplies needed by the on-board ICs. Connection via banana plugs or grips is possible. To avoid supply connection errors, ...

Embedded Systems - Notes 6

... Inputs Multiplexing – Typically share a single ADC among multiple inputs – Need to select an input, allow time to settle before sampling ...

... Inputs Multiplexing – Typically share a single ADC among multiple inputs – Need to select an input, allow time to settle before sampling ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.