* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download nssc spice lab elec1

Survey

Document related concepts

Variable-frequency drive wikipedia , lookup

Current source wikipedia , lookup

Electrical substation wikipedia , lookup

Resilient control systems wikipedia , lookup

Control theory wikipedia , lookup

Alternating current wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Control system wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Topology (electrical circuits) wikipedia , lookup

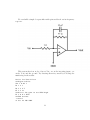

Buck converter wikipedia , lookup

Regenerative circuit wikipedia , lookup

Mains electricity wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Two-port network wikipedia , lookup

Opto-isolator wikipedia , lookup

Rectiverter wikipedia , lookup

Transcript

NSSC SPICE LAB ELEC1 James Morad / Ben Godfrey June 27, 2015 1 INTRODUCTION SPICE (Simulation Program with Integrated-Circuit Emphasis) is a useful tool for circuit analysis. By feeding the program the appropriate text file, called a stack, we will model the DC and AC characteristics of the circuit described in our stack. At the heart of the stack is the netlist - a convenient way of representing your circuit in text form. When starting out in SPICE, it will be helpful to keep these tips in mind: • Your stack will have the extension .cir • Every SPICE stack begins with a commented line. This is room for you to place a title for your circuit and is not optional. • An asterisk (*) placed at the beginning of a new line will comment out a line • A plus sign (+) placed at the beginning of a new line will append the new line will append the new line to the previous line. • Case does not matter • Every stack must have a .END statement • If you’re using the free version of SPICE3+NUTMEG, be careful with tutorial focused on PSPICE. The commands are not interchangeable. 1.1 Writing your first netlist The best way to learn (or at least in this case) is by example. Let’s take a look at a simple circuit and its corresponding netlist. On the circuit below, I have labeled the nodes with numbers so that building the netlist will just 1 be a follow the numbers game. It will help to go through your own circuit and label every node with a number when building a netlist. First SPICE netlist * The format for the DC voltage is: V[whatever name you choose] NODE1 NODE2 DCVal * where NODE1 is the +5V rail and NODE2 is the ground rail. This is arbitrary Vsource 1 0 5 * The format for resistor is: R[whatever name you choose] NODE1 NODE2 ResistorVal * where the resistors terminals physically attach to those nodes R1 1 2 4.7K * The format for capacitors is the same. First letter must be C. C1 2 0 1M R2 2 3 270 R3 3 0 1.1k C2 3 0 50m 2 2.1 Example Scenarios DC operating point aka quiescent point aka q-point analysis In this scenario we will use SPICE to calculate the node voltages in a resistor network 2 The netlist is a fairly simple task given the numbered nodes, so let’s throw on the rest of the stack needed to actually perform our analysis: EXAMPLE 2 Vin 1 0 5V R1 1 2 4.7K R2 1 3 330 R3 2 4 2.7K R4 3 4 910 R5 3 0 18K R6 4 0 1.1K ***End of netlist ***Begin control block. Everything within the control block ***can be done directly from the SPICE command line interface. .control op ***The OP command performs an operating point analysis of the circuit print all 3 ***The print command prints on the output (terminal) what you tell it to. ***Change "all" to "V(2)" and observe the output. .endcontrol ***End control block .end Now, assuming you have copied the above into a text file and saved it is Example2.cir, fire up your version of SPICE. From the SPICE terminal, navigate to the directory containing Example2.cir, type out the name of the file, and hit enter. The result should appear as follows: Spice 1 -> Example2.cir Circuit example 2 v(1) = 5.000000e+00 v(2) = 3.418327e+00 v(3) = 4.279681e+00 v(4) = 2.509707e+00 vin#branch = -2.51931e-03 The terminal displays the node voltages (1-4) as well as vin# branch, the branch current at the Vin node. Verify that these results are correct by running through the nodal analysis by hand. Assume the following branch currents • i1 is the current running from node 1 to node 4 • i2 is the current from from node 1 to node 3 • i3 is the current from node 3 to node 4 • i4 is the current from node 3 to ground • i5 is the current from node 4 to ground This generates the following system of equations 1. 7.4i1 + 1.1i5 = 5 2. 0.33i2 + 18i4 = 5 3. 0.33i2 + 0.91i3 + 1.1i5 = 5 4 4. i2 = i3 + i4 5. i1 + i3 = i5 Row reduce to solve this system of equations: 7.4 0 0 0 1.1 0 0.33 0 18 0 0 0.33 0.91 0 1.1 0 1 −1 −1 0 1 0 1 0 −1 5 5 5 0 0 ⇒ 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0.33653 2.18279 1.94503 0.23776 2.28755 Solving for the node voltages gives the same values as produced in Spice. Now try to comment out the entire control block from Example2 and save the stack. Run Example2.cir from the SPICE command line and enter in the commands OP and PRINT by hand. Verify that the results are expected. 2.2 Transient analysis Transient analysis allows us to follow the voltage at the nodes of our system over time. We will start with this section by looking at the voltage decay in an LRC network with some initial condition. Before SPICE, solving for the time dependence of the voltage in an LRC network meant setting up a differential equation and doing all sorts of busy work. With SPICE, you can plot a graph of the voltage or current at any node within a matter of seconds (depending on how fast you type)! In the following diagram, take the value of the inductor (L1 ) to be 100 Henries. 5 EXAMPLE 3 LRC ***Begin netlist Vin 1 0 PULSE (0V 5V 0 .1s .1s 10s) R1 1 2 100 C1 1 0 1m L1 2 0 100 ***End netlist ***Specify initial condition (5V at node 1) with .IC command .IC V(1) = 5 ***Perform transient analysis .TRAN .1s 20s ***Begin control block .control run plot V(1) V(2) .endcontrol ***End control block .end The output should show up on your monitor as two plots on the same set of axes, as shown below 6 Now, we will look at the same network with no initial condition and pulsed voltage from a source connected to node 1. EXAMPLE 3 LRC ***Begin netlist ***Voltage source is pulsed by using the pulse modifier ***PULSE([initial_V] [final_V] [start_time] [rise_time] [fall_time] [length_pulse ***a missing modifier that I did not include in my code comes after the length_pu ***adding the modifier will allow you to specify the period of your pulse if you ***wish your pulse to be periodic Vin 1 0 PULSE (0V 5V 0 .1s .1s 3s) R1 1 2 100 C1 1 0 1m L1 2 0 100 ***End netlist ***Specify initial condition (5V at node 1) with .IC command 7 .IC V(1) = 5 ***Perform transient analysis .TRAN .1s 20s ***Begin control block .control run plot V(1) V(2) .endcontrol ***End control block .end The output from this stack is shown below. 8 2.3 AC analysis Our last sections will show you how to perform an AC analysis of your circuit and, more importantly, how to plot the frequency response of the circuit. Let’s start by taking a look at the stack we’re going to use for the following low-pass filter. Low Pass filter ***Begin netlist Vin 1 0 AC 1 R1 1 2 4.7 C1 2 0 1u ***End netlist ***Begin control block .control ***The AC command performs an AC analysis on the circuit ***DEC tells AC to output in decades, i.e. logarithmic plot ***10 tells us to plot 10 points per decade ***100 is the starting frequency on our plot ***100k is the final frequency on our plot ac dec 10 100Hz 100KHz ***We can plot a Bode plot by telling the PLOT command to ***plot V(2)/V(1) on a decibel scale with the DB() command plot db(V(2)/V(1)) .endcontrol ***End control block 9 .end The output is below: Now try to build a high-pass filter and verify that the plot is correct by calculating the corner frequency. Finally, let’s use what SPICE was for and introduce an integrated circuit element: the ideal operational amplifier. The ideal op-amp can be modeled in the following way 10 We can build a simple low-pass filter with gain and check out its frequency response. This system has four nodes. One at Vin, one at the inverting input, one at the Vout, and the ground. Try drawing them in yourself by following the numbering in the netlist. Active Low Pass filter ***Begin netlist Vin 1 0 AC 1 R1 1 2 1 R2 2 3 4.7 C1 2 3 1u ***Notice the gain is set VERY high. E1 3 0 0 2 1E10 ***End netlist .control ac dec 10 100 100K 11 plot db(V(3)/V(1)) .endc .end The output plot should be identical to that of the passive low-pass filter with one exception: we now have gain. Confirm that the corner frequency makes sense by using an ideal op amp model and calculating the corner. 12 3 13 LUX Amplifier 4 Assignment Model the Schmitt trigger above using the NPN model with parameters shown below using the following model: .MODEL QSTD NPN(is=1.0e-16 + bf=100 + br=0.1 + rb=50 + rc=10 + tf=0.12ns + tr=5ns + cje=0.4pf + pe=0.8 + me=0.4 + cjc=0.5pf + pc=0.8 + mc=0.333 + ccs=1pf + va=50) See Getting Down with Spice 2 for how to add a BJT 14 Create a Sallen-Key low-pass filter based off of the following design with a corner frequency of 20 [kHz] 15