* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Homework 4:Power, Scaling, Wires and Logic (ms

Ground (electricity) wikipedia , lookup

Wireless power transfer wikipedia , lookup

Standby power wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Power factor wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Electrical substation wikipedia , lookup

Power over Ethernet wikipedia , lookup

Electric power system wikipedia , lookup

Stray voltage wikipedia , lookup

Three-phase electric power wikipedia , lookup

Audio power wikipedia , lookup

Electrification wikipedia , lookup

Voltage regulator wikipedia , lookup

Pulse-width modulation wikipedia , lookup

History of electric power transmission wikipedia , lookup

Power engineering wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Opto-isolator wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Buck converter wikipedia , lookup

Alternating current wikipedia , lookup

Distribution management system wikipedia , lookup

Voltage optimisation wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Power supply wikipedia , lookup

Power inverter wikipedia , lookup

Mains electricity wikipedia , lookup

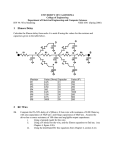

EE 141 Fall 1999 Homework Set #4 Due Wed. Oct 6 1999, 5.00 pm Problem 1) Consider a simple CMOS inverter circuit. Let the circuit be driven by a squarewave input signal with period T = 20ns and the total output load capacitance is equal to 1pF. The power supply is 5V. a) Calculate the expected average power dissipation. b) Assume the voltage is reduced with a factor 2. Discuss qualitatively the impact on the average power dissipation, taking into account the reduction in period of the input signal forced by the reduction of the supply voltage. Problem 2) Consider the pseudo-nMOS inverter shown below. Given that Vdd= 5V, VTn = | VTp | = 1 V, kn = 100 A/V2, kp = 40 A/V2, = 0.2 V1/2, F = -0.3 V, = 0 USE THE LONG-CHANNEL TRANSISTOR MODEL, I.E. YOU MAY ASSUME THAT VDSAT = . a) Find VOH, VOL b) Find static power dissipation when 1- Vin is low and 2- Vin is high c) Calculate tpLH, tpHL, and tp. Are the rising and falling delays equal? Why or why not? Use a 50fF cap at the output as the load capacitance. d) If channel length modulation is not neglected, would VOL be larger, smaller or the same. Problem 3) A microprocessor was fabricated using a 0.35 m technology and was able to operate at 100Mhz, consuming 10 watts using a 3.5 V power supply. a) Using fixed voltage scaling, what will the speed and power consumption of the same processor be if scaled to 0.1 m technology? b) If the supply voltage in the scaled 0.1 m part was reduced to 1.0 V what will the power consumption and speed be? c) What supply should be used to maintain the power at 10 watts? At what speed would it operate? d) Are there any power increases associated with constant voltage scaling? If so, What should the new scaling factor W, be to maintain approximately constant power? Assume short-channel devices. Problem 4) A two-stage buffer is used to drive a metal wire of 1cm. The first inverter is a minimumsize inverter with an input capacitance Ci of 10fF and a propagation delay tp0 of 175psec when loaded with an identical gate. The width of the metal wire is 3.6 m. The sheet resistance of the metal is 0.08 /, the capacitance value of the metal is 0.03 fF/m2, and the fringing field capacitance is 0.04 fF/m. a) What is the propagation delay tw over the metal wire? b) Compute the optimal size of the second inverter. What is the minimum delay through the buffer-wire combination. Problem 5) Consider the logic gate given above a) Determine the logic function of the gate b) Draw the pull-down network (ensure you use a minimum number of transistors) c) Determine an ordering of the input signals, such that the PMOS network can be laid out on a contiguous diffusion strip. d) Size the PMOS transistors such that the resistance of the PMOS network is always equal or smaller than a single minimum-size PMOS device, yet is minimal in area.