* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download ms-word

Survey

Document related concepts

Current source wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Opto-isolator wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Distribution management system wikipedia , lookup

Semiconductor device wikipedia , lookup

Power electronics wikipedia , lookup

Two-port network wikipedia , lookup

Power inverter wikipedia , lookup

History of the transistor wikipedia , lookup

Transcript

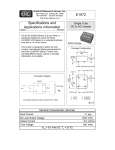

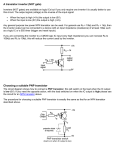

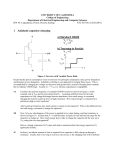

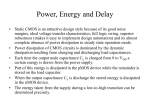

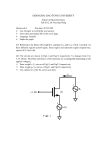

EE141 Fall 1999 Homework Set #3 Due Wed. September 22, 5:00pm The goal of this homework set is to find out how well the hand analysis parameters given in tables 3.2 and 3.5 predict the performance of our technology. Tables 3.2 and 3.5 can be found on pages 71 and 80 of Digital Integrated Circuits, 2nd edition, Chapter 3, available on the web. Problem 1) a) Assuming the geometry and layers shown in the figure below, use max with the mmi25 technology to find the minimum NMOS transistor dimensions which do not violate any design rules. Calculate the transistor length, width, source/drain area and source/drain perimeter. List the design rules which determined these values. poly nfet ct ndif TIPS: Use Shift-G to access the grid menu. Set the coarse grid to 0.1 m and the fine grid to 0.01 m. Use Shift-Y to explain the design rule violations within the current selection area. b) We need to design a minimum sized CMOS inverter which is a standard for our technology. Assuming a manufacturing grid of 0.01 m and a supply voltage of 2.5V, use the unified MOSFET model and the parameters in Table 3.2 to find the minimum sized PMOS transistor which sets VM=VDD/2 (you may assume that the minimum PMOS dimensions are identical to the minimum NMOS dimensions). Calculate the length, width, source/drain area and source/drain perimeter for this transistor. c) Use the unified MOSFET model to find VIL and VIH. d) Use HSPICE and the g25.mod typical transistor models to find VM, VIL, and VIH. Compare these with your calculated values. Turn in a print-out of your HSPICE input deck. Problem 2) a) Use the hand analysis parameters from Table 3.5 to determine the input and output capacitances of the inverter you determined in problem 1 (assuming VDD=2.5V). Vin Cin Vout Cout b) Use HSPICE and the typical g25.mod models to measure Cin. Since the eventual goal is to predict tpLH and tpHL, measure CinLH (capacitance in the 0 to VDD/2 region) and CinHL (capacitance in the VDD/2 to VDD region). TIPS: Drive the input with a DC current source of 1 A. Perform a transient analysis of about 10ns. Use “.IC V(in)=0” to set the initial condition at the input Use the following measure statements to calculate the capacitance: .MEASURE t1 TRIG AT=0 TARG V(in) VAL=1.25 CROSS=1 .MEASURE CinLH PARAM=’1u*t1/1.25’ .MEASURE t2 TRIG V(in) VAL=1.25 CROSS=1 TARG V(in) VAL=2.5 CROSS=1 .MEASURE CinHL PARAM=’1u*t2/1.25’ Compare the measured and calculated values of input capacitance. Explain briefly why CinLH is larger than CinHL. c) Use the hand analysis parameters from Table 3.2 to determine Ron for the NMOS and PMOS transistors. Calculate the tpHL, tpLH, trise, and tfall using the RC model with both the hand calculated values from part a) and the measured values from part b). Assume that the inverter is loaded with an identical inverter. Compare these values to measured values from an HSPICE simulation using the typical g25.mod models. TIPS: Model the load as a second inverter (don’t use a linear capacitor). Drive the inverter chain with a piecewise-linear source with a 0%-100% rise/fall time of 40ps. Use the .MEASURE command to find the result. d) Assuming a constant load capacitance, could you reduce the average propagation delay of the inverter by changing the size of the PMOS transistor? What limit would you reach? Problem 3) R Consider the simple RC circuit shown on the right. Assume that we want to charge the capacitor from zero volts to some final voltage V0. For each of the functions of Vin shown below, calculate the energy dissipated in the resistor. Assume in parts b) and c) that T is much greater than RC. Vin C Vin Vin Vin V0 V0 V0 1 V 2 0 t t0 a) t0 t0 T b) t t0 t0 T c) t