ENHANCEMENT OF DEFECT DIAGNOSIS BASED ON THE ANALYSIS OF CMOS DUT BEHAVIOUR

... Figure 3.17. Predicted vs. measured IDDQ values in the presence of downstream current......................... 60 Figure 3.18. Graphical representation of the quality parameters. ............................................................. 61 Figure 3.19. Diagnosis flow for bridging defects. ...... ...

... Figure 3.17. Predicted vs. measured IDDQ values in the presence of downstream current......................... 60 Figure 3.18. Graphical representation of the quality parameters. ............................................................. 61 Figure 3.19. Diagnosis flow for bridging defects. ...... ...

STM1810

... When VCC falls below 1 V, the RST output no longer sinks current, but becomes an open circuit. In most systems this is not a problem, as most MCUs do not operate below 1 V. However, in applications where RST output must be valid down to 0 V, a pull-down resistor may be added to hold the RST output l ...

... When VCC falls below 1 V, the RST output no longer sinks current, but becomes an open circuit. In most systems this is not a problem, as most MCUs do not operate below 1 V. However, in applications where RST output must be valid down to 0 V, a pull-down resistor may be added to hold the RST output l ...

the pin diode circuit designers` handbook

... Low-pass filters may significantly increase the switching time of the PIN diode. If a switching time of 100 ns is needed, the low-pass filter must show very little loss to frequencies up to 30 MHz (ie, the filter's cutoff frequency is at least 30 MHz). Shorter switching times require higher filter c ...

... Low-pass filters may significantly increase the switching time of the PIN diode. If a switching time of 100 ns is needed, the low-pass filter must show very little loss to frequencies up to 30 MHz (ie, the filter's cutoff frequency is at least 30 MHz). Shorter switching times require higher filter c ...

NE02 Brochure

... interrupting capabilities than their multi-pole interrupting rating. See discussion for section 240.85 on slash ratings and single pole interrupting capabilities. How does one know in practical applications if an overcurrent protective device’s interrupting rating is sufficient? It is necessary to u ...

... interrupting capabilities than their multi-pole interrupting rating. See discussion for section 240.85 on slash ratings and single pole interrupting capabilities. How does one know in practical applications if an overcurrent protective device’s interrupting rating is sufficient? It is necessary to u ...

MAX9322 LVECL/LVPECL 1:15 Differential Divide-by-1/Divide-by-2 Clock Driver General Description

... reproduces or divides one of two differential input clocks at 15 differential outputs. An input multiplexer selects from one of two input clocks with input switching frequency in excess of 1.0GHz. The 15 outputs are arranged in four banks with 2, 3, 4, and 6 outputs, respectively. Each output bank i ...

... reproduces or divides one of two differential input clocks at 15 differential outputs. An input multiplexer selects from one of two input clocks with input switching frequency in excess of 1.0GHz. The 15 outputs are arranged in four banks with 2, 3, 4, and 6 outputs, respectively. Each output bank i ...

ESD Protection Layout Guide

... The impedance presented to IESD is a function of any impedance inherent with the TVS (in the diode array and the package of the TVS) and the PCB Layout between the ESD Source and the TVS ground. A TVS is generally designed to offer as low of an impedance to ground for IESD as its overall design cons ...

... The impedance presented to IESD is a function of any impedance inherent with the TVS (in the diode array and the package of the TVS) and the PCB Layout between the ESD Source and the TVS ground. A TVS is generally designed to offer as low of an impedance to ground for IESD as its overall design cons ...

ADM9690 数据手册DataSheet 下载

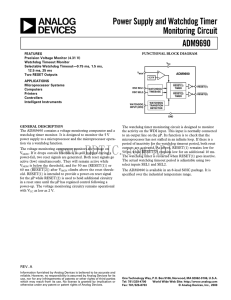

... 60 ms (RESET(2)) after VMON climbs above the reset threshold. RESET(1) is intended to provide a power-on reset signal for the µP while RESET(2) is used to hold additional circuitry in a reset state until the µP has regained control following a power-up. The voltage monitoring circuitry remains opera ...

... 60 ms (RESET(2)) after VMON climbs above the reset threshold. RESET(1) is intended to provide a power-on reset signal for the µP while RESET(2) is used to hold additional circuitry in a reset state until the µP has regained control following a power-up. The voltage monitoring circuitry remains opera ...

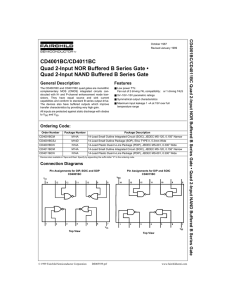

CD4011BC Quad 2-Input NAND Buffered B Series Gate

... The CD4001BC and CD4011BC quad gates are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. They have equal source and sink current capabilities and conform to standard B series output drive. The devices also have buffered outputs ...

... The CD4001BC and CD4011BC quad gates are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. They have equal source and sink current capabilities and conform to standard B series output drive. The devices also have buffered outputs ...

CD4001BC * CD4011BC Quad 2-Input NOR/NAND Buffered B

... The CD4001BC and CD4011BC quad gates are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. They have equal source and sink current capabilities and conform to standard B series output drive. The devices also have buffered outputs ...

... The CD4001BC and CD4011BC quad gates are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. They have equal source and sink current capabilities and conform to standard B series output drive. The devices also have buffered outputs ...

Installation Manual

... Electronic Solar Switch ...........................................................100 ...

... Electronic Solar Switch ...........................................................100 ...

3: Nodal Analysis

... (1) Nodal Analysis - systematic; always works (2) Circuit Manipulation - ad hoc; but can be less work and clearer Reminders: A node is all the points in a circuit that are directly interconnected. We assume the interconnections have zero resistance so all points within a node have the same voltage. ...

... (1) Nodal Analysis - systematic; always works (2) Circuit Manipulation - ad hoc; but can be less work and clearer Reminders: A node is all the points in a circuit that are directly interconnected. We assume the interconnections have zero resistance so all points within a node have the same voltage. ...

possible questions - Merrillville Community School

... WHAT IS THE RESISTANCE MEASURED AT POINTS A & B? ...

... WHAT IS THE RESISTANCE MEASURED AT POINTS A & B? ...

74HC4851; 74HCT4851 1. General description 8-channel analog multiplexer/demultiplexer with

... inputs/outputs (Y0 to Y7) and a common input/output (Z). The devices feature injection-current effect control, which has excellent value in automotive applications where voltages in excess of the supply voltage are common. With E LOW, one of the eight switches is selected (low impedance ON-state) by ...

... inputs/outputs (Y0 to Y7) and a common input/output (Z). The devices feature injection-current effect control, which has excellent value in automotive applications where voltages in excess of the supply voltage are common. With E LOW, one of the eight switches is selected (low impedance ON-state) by ...

gate circuit

... Methods for Switching- on the thyristor The switching process of the thyristor is called “ Firing”, because after Switching process is ceased, WHERE the firing signal may can removed with purpose to reduce the gate loss .There're several methodS Applied to realize this purpose : 1-Gate-firing metho ...

... Methods for Switching- on the thyristor The switching process of the thyristor is called “ Firing”, because after Switching process is ceased, WHERE the firing signal may can removed with purpose to reduce the gate loss .There're several methodS Applied to realize this purpose : 1-Gate-firing metho ...

Service Manual, I.B. 1510 - Industrial Batteries and Chargers

... variations of +10% will have almost no effect on the operating curve. All chargers are designed for convection cooling with no derating, up to an ambient temperature of 40°C, 104°F (if properly installed per the Installation and Operating Instructions manual). All models have an Equalize cycle that ...

... variations of +10% will have almost no effect on the operating curve. All chargers are designed for convection cooling with no derating, up to an ambient temperature of 40°C, 104°F (if properly installed per the Installation and Operating Instructions manual). All models have an Equalize cycle that ...

Current source

A current source is an electronic circuit that delivers or absorbs an electric current which is independent of the voltage across it.A current source is the dual of a voltage source. The term constant-current 'sink' is sometimes used for sources fed from a negative voltage supply. Figure 1 shows the schematic symbol for an ideal current source, driving a resistor load. There are two types - an independent current source (or sink) delivers a constant current. A dependent current source delivers a current which is proportional to some other voltage or current in the circuit.