* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download RT1 - Faculty of Engineering

Scattering parameters wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Alternating current wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Negative feedback wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Audio power wikipedia , lookup

Opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Signal-flow graph wikipedia , lookup

Current source wikipedia , lookup

Distribution management system wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Power MOSFET wikipedia , lookup

Regenerative circuit wikipedia , lookup

Current mirror wikipedia , lookup

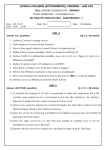

EMF4086 RF Transistor Circuit Design RT1 FACULTY OF ENGINEERING LAB SHEET EMF4086 RF TRANSISTOR CIRCUIT DESIGN TRIMESTER 2 (2014/2015) RT1 – RF Amplifier Design *Note: On-the-spot evaluation may be carried out during or at the end of the experiment. Students are advised to read through this lab sheet before doing experiment. Your performance, teamwork effort, and learning attitude will count towards the marks. F. Kung 1 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 RT1 – Designing A Constant Power Gain Amplifier Introduction In this experiment you are going to design a simple single-stage bipolar junction transistor (BJT) amplifier with a power gain of +20dB into 50 load and operating at 600MHz. The design is carried out using the software Advance Design System by Agilent Technologies. Follow the procedures outlined below. Overview of Design Procedures A typical design flow for small signal amplifier is shown in Figure 1: DC biasing design Defining amplifier Characteristics S-parameters measurement Requirement not met Stability check Plotting gain circles, mismatch circles and noise figure circles Power Supply and d.c. biasing Source Network Amplifier Determine optimum source and load impedance Load Network Verify Gain, bandwidth , VSWR, noise figure etc of amplifier END Requirement met Figure 1 – Amplifier block diagram and small-signal amplifier design cycle. We are going to design a small-signal amplifier with a specific gain at 600MHz, the other parameters such as input and output VSWR (voltage standing wave ratio) and noise F. Kung 2 Oct 2014 EMF4086 RF Transistor Circuit Design figure are not considered. implemented. RT1 Therefore only the steps underlined in Figure 1 are The Detailed Design Procedures Step 1 – Run ADS software Log into Windows workstation (username and password would be supplied to you). Run Advance Design System software from the start menu as shown in Figure 2 or from the icon on the desktop. or Figure 2 – Running ADS. Step 2 – Create a new project From the main window of ADS, create a new project named “EMG4086” under the folder “D:\ADS\default\”. Figure 3 – Creating a new project “EMG4086”. F. Kung 3 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 A new Schematic window will automatically appears once the project is properly created. Otherwise you can manually open a new Schematic window by double clicking the Create New Schematic button Figure 4 below. on the main window. The work area is shown in Component Palette Selection List Component history Component Palette GND node Wire Wire/node name Insert variable Data Display Simulate Tuning Component Library Work Area Figure 4 – The schematic work area. Step 3 – Drawing the basic circuit The first step is to choose a suitable transistor for the job. For this example we select the NPN wide-band transistor BFR92A. This transistor comes in an SOT-23 package and has a transition frequency fT of 5.0GHz. Both Infineon Technologies and NXP Semiconductor (formerly Phillips Semiconductors) manufacture this device. You can get a model of this transistor from the component library . Use the search function to look for “bfr92a” as illustrated in Figure 5A. There are many versions of the model, you should use the one with the description “BRF92A: SOT23 Package….”. This model simulates the transistor based on the laws of the device physic, taking into account the package parasitic capacitance and inductance. The other models are ‘black box’ models based on S-parameters measurement. These are only accurate for a certain d.c. bias condition. Datasheet for this transistor can also be obtained from the manufacturers websites. The actual transistor is shown in Figure 5B. F. Kung 4 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Figure 5A – Getting the transistor BFR92A from the component library. C B E Figure 5B – Top view of BFR92A transistor from NXP Semiconductor. Use the following component pallette to access the components button: Lumped Component Palette – inductor, resistor and capacitor Sources -Time Domain Palette – d.c. voltage source Simulation-DC – DC simulation control . . . Construct the circuit as shown in Figure 6. This is a common-emitter configuration with RF chokes Lb1 and Lb2 to isolate the d.c. biasing components from the transistor. F. Kung 5 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Figure 6 – The basic amplifier circuit for d.c. simulation. Step 4 – Perform d.c. Simulation to Ensure Transistor is Operating in Active Region Run the d.c. simulation by clicking the simulation button on the Schematic window . You can view the d.c. voltage and current on every nodes and wires on the circuit by activating the d.c. annotation command as shown in Figure 7 below. Go to the Simulate menu and select annotate dc solution. The important voltages and current are shown in Table 1. Observe that BE junction of Q1 is forward biased while BC junction or Q1 is reversed biased, thus the transistor is operating in active region. The collector current IC and VCE affects the value of the small-signal S-parameters to be obtained later. F. Kung 6 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Figure 7 – To display the d.c. solution results on the schematic window. VB VC 1.39V 5.0V Table 1 – The d.c. solution. VE 0.60V IC 5.9mA Step 5 – Modify the Schematic S-Parameter Simulation After performing the d.c. simulation, modify the schematic of Figure 6 for S-parameters simulation. Include the coupling capacitors Cc1 and Cc2. Accessing the SimulationS_Param component palette, insert the control and termination for Sparameters simulation. Set the parameters for simulation and termination as shown in Figure 8. Note the numbering of the termination, 1 for input port and 2 for output port. We are going to run frequency sweep from 50MHz to 1.0GHz at a step of 1.0MHz. The software actually run a linear small-signal frequency domain simulation and calculates the S-parameter using 1 Vi Z o I i ai 2 Zo 1 Vi Z o I i bi 2 Zo S ij F. Kung bi aj 7 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 where Vi and Ii are the voltage and current on the ith node. Figure 8 – Schematic for performing S-parameter simulation. Before you run the simulation for Figure 8, save the schematic as “bjt_amplifier.dsn” as illustrated in Figure 9. Figure 9 – Saving the schematic or network (as it is known in ADS). Step 6 – Perform S-Parameter Simulation Run the simulation of the schematic in Figure 8. A Data Display window will automatically pop up, if it does not you can manually call up a Data Display window using the button on the Schematic window. You can now display the S-Parameters S11, S22, S12 and S21 as a function of frequency as shown in Figure 10. F. Kung 8 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Select S11 and click the “Add” button to include the trace in the plot. Repeat for S12, S2 and S22. Figure 10 – Selecting a trace to be shown in a plot. The complete S-parameters are shown in Figure 11 and Figure 12. Since the Sparameters are complex quantities, S12 and S21 are shown as X-Y plot of the magnitude and phase versus frequency. S11 and S22 are displayed in Smith Chart format. Use the button to insert X-Y plot and the button to insert a Smith Chart. Hint: By using a Marker, you can read the value from the graph. Double-clicking on each line allows you to change the property of the lines such as thickness and colour. F. Kung 9 Oct 2014 RT1 0.12 110 0.10 100 phase(S(1,2)) mag(S(1,2)) EMF4086 RF Transistor Circuit Design 0.08 0.06 0.04 90 80 70 0.02 60 0.00 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 0.0 1.0 0.1 0.2 0.3 0.5 0.6 0.7 0.8 0.9 1.0 0.7 0.8 0.9 1.0 freq, GHz freq, GHz 20 200 15 100 phase(S(2,1)) mag(S(2,1)) 0.4 10 5 0 0 -100 -200 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 0.0 0.1 freq, GHz 0.2 0.3 0.4 0.5 0.6 freq, GHz Figure 11 – X-Y Plot of S12 and S21 versus frequency. Hint: You can check the values of individual points on the curves by using a “marker”. Go to the “Marker” command on the Data Display window’s menu and select “New”. Then click your mouse pointer on the corresponding curve. S(1,1) S(2,2) Frequency 50MHz to 1.0GHz Figure 12 – Smith Chart display of S11 and S22 versus frequency. F. Kung 10 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Step 7 – Stability Check After obtaining the S-parameters, we could check the stability of the amplifier circuit at various frequencies. This can be carried out by plotting the Roulette stability factor (K) and D which are function of S-parameters: 2 K 1 S11 S 22 2 D 2 2 S12 S 21 D S11S 22 S12 S 21 When K > 1 and |D| < 1, the amplifier is unconditionally stable, otherwise it is conditionally stable or totally unstable. We can plot K and |D| by defining equations in the Data Display window. Insert an equation using the button . The definition for K and |D| are shown in Figure 13. These are then plotted as X-Y plot and is depicted in Figure 15. Note that ADS also has built-in function to define the parameter K, which is the function stab_fact( ). Figure 13 – Definition for Roulette Stability Factor K and |D|. To insert data from equation, use the button to insert an X-Y plot and select “Equations” from the “Datasets and Equations” drop-down menu. Make sure the dataset is “bjt_amplifier”, which is the name of the schematic. F. Kung 11 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Figure 14 – Selecting the equation data instead of simulation data to plot K and |D|. m1 freq=600.0MHz K=0.956 Marker’s textbox Marker 1.2 m1 1.0 K 0.8 0.6 D D K 0.4 0.2 0.0 -0.2 -0.4 -0.6 -0.8 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 freq, GHz Figure 15 – K and |D| versus frequency. F. Kung 12 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Using a marker, it is seen from Figure 15 that K<1 and |D|<1 at f = 600MHz. Therefore the amplifier is conditionally stable. The means there are certain source and load impedance which might cause the amplifier to become unstable and oscillate. To determine the region of instability, we must plot the Source Stability Circle and Load Stability Circle in the next step. Step 7 – Plotting Stability Circles Before we proceed, save the schematic as a new file name “bjt_amplifier_600Mhz.dsn”. The preceding simulation for “bjt_amplifier.dsn” runs the S-Parameters simulation for a range of frequency. Now we would like to specifically concentrate on the frequency 600MHz, our frequency of interest. Hence the name “bjt_amplifier_600MHz.dsn”. Modify the S-Parameter simulation control as shown in Figure 16 for single point simulation. Figure 16 – Single point simulation at 600MHz. Simulate the new schematic and a new Data Display window will appear (or you can manually call up a new one). Now define two equations as in Figure 17. These equations uses built-in functions s_stab_circle( ) and l_stab_circle( ). These functions actually implement the stability circle equations for source reflection coefficient s and load reflection coefficient L as follows: L S s S 22 DS11* S 22 11 2 D S11 D * 2 DS 22* 2 2 S12 S 21 S 22 * 2 D 2 S12 S 21 2 S11 D 2 Figure 17 – Definition for source and load stability circles. The s_stab_circle( S,51) function plots the Source Stability Circle for s using current S-parameters value and forming the circle using 51 data points. Similarly for F. Kung 13 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 l_stab_circle(S,51) plots the Load Stability Circle for L using 51 data points. Use the table button 18. to display the values of S11 and S22 and 600MHz as shown in Figure Figure 18 – S11 and S22 at 600MHz. The stability circles are plotted on the extended Smith Chart in Figure 19. From Figure 17, |S11| and |S22| are less than unity at 600MHz, hence the stable region is outside the circles from stability theory (see lecture notes). Thus if we were to design an amplifier, the source reflection coefficient and the load reflection coefficient as seen by the amplifier must reside in the stable region. The next step is to plot the locus of constant power gain, and to make sure that at least some part of the locus falls in the stable region. Load Stability Circle Source Stability Circle Stable source and load impedance region Magnitude = 1 Figure 19 – The Source and Load Stability Circles. The shaded region is the stable region for both source and load reflection coefficient. F. Kung 14 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Step 8 – Plotting the Constant Power Gain Circles and Finding the Optimum Load Impedance Using the Data Display window for “bjt_amplifier_600Mhz.dsn”, we add the following definition for constant power gain circles depicted in Figure 20. Eqn Gain_10 = gp_circle(S,10,51) Eqn Gain_15 = gp_circle(S,15,51) Eqn Gain_20 = gp_circle(S,20,51) Figure 20 – Definition for constant power gain circles, for 10dB, 15dB and 20dB. Again this is a built-in function in ADS, which plot all the L points on the Smith Chart, which fulfills x 10 log 10 G p . Here x is 10, 15 and 20. Gp 1 2 S 2 L 21 1 S 22 L 2 S11 DL 2 Power Gain For instance, the definition gp_circle(S,15,51) in Figure 19 means Gp(L) = 15dB circle using 51 data points and current S-Parameters. The constant power gain circles are plotted together with the Source and Load Stability Circles in Figure 21. Source stability circle Load stability circle 20dB Step 9 – Time Domain Simulation and Verfication Marker 15dB 10dB Magnitude = 1 Figure 21 – Constant power gain circles. F. Kung 15 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 An important observation in Figure 21 is that as we increase the power gain of the amplifier, the required load reflection coefficient L will move towards the margin of stability. This is reasonable because as we increase the gain of an amplifier, the tendency to oscillate increases as any small amount of feedback will result in uncontrolled positive feedback and hence oscillation. The amount of feedback in the amplifier is given by the S12. Since we want an amplifier with +20dB gain at 600MHz, the load reflection coefficient must falls on the Gp = 20dB circle. We choose the value marked by the marker in Figure 21. This value is the furthest away from the Load Stability Circle; hence it will be less affected by changes in the stability circle due to parameters variation of the transistor. From the marker position, the value of optimum load is approximately (Zo is the impedance value of components TERM1 and TERM2 in the schematic): Z L Z o 1.802 j 2.926 90.1 j146.3 Z o 50 At 600MHz, this load can be modeled by a 90.1Ohm resistor in series with 38.8nH inductor. If the actual load that is connected to the amplifier is not this network, we could employ an impedance transformation network to transform the actual load network to produce this equivalent value at 600MHz. Figure 22 – Equivalent load at 600MHz for amplifier. Step 9 – Time Domain Verification Now we want to perform a time domain simulation to verify our circuit. Save the current schematic as “bjt_amplifier_600MHz_td.dsn” and modify the schematic to the one shown in Figure 23. You will need to change the component palette to Sources-Time Domain and Simulation-Transient to access the Sine Voltage Source and the Transient Simulation Control buttons. You will also need to name the input and output node as Vin and Vout as in Figure 23. Access the Name Wire/Node button on the Schematic window. A dialog box as shown in Figure 23 will appear, type the name of the input node and click on the node to be named Vin in the schematic. Repeat the similar procedures for Vout. F. Kung 16 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Figure 23 – Name the input node as Vin and the output node as Vout. Output node Input node Figure 24 – The final schematic for time domain simulation. Finally run the simulation of the schematic in Figure 24. Plot the time domain waveform for Vin and Vout on a new Data Display window. The result is shown in Figure 25. F. Kung 17 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 800 700 600 Vout 500 400 300 200 Vin Vout, mV Vin, mV 100 0 -100 -200 -300 -400 -500 -600 -700 -800 10 12 14 16 18 time, nsec Figure 25 – Vout and Vin as a function of time. The time average power dissipated at the load can be estimated by: 2 Vout * 1 Vout 1 1 * PL Re Vout I out Re Vout 2 2 Z L * 2 Re Z L And the time average power input the amplifier can be estimated (we ignore the difference in phase between current and voltage) by: Ps F. Kung 1 1 Vin Vs Vin Vin I in * 2 2 Rs 18 Oct 2014 20 EMF4086 RF Transistor Circuit Design RT1 From Figure 24, |Vout| 0.78V and |Vin| 0.033V. Vs is the magnitude of the sinusoidal voltage source (0.1V) and Rs = 50, Re(ZL) = 90.1. PL 3.37610-3 W Ps 2.21110-5 W Finally power gain is given by: Gp = 10log10(PL/Ps) = 10log10( 152.7) = 21.84dB Which is quite near our frequency domain estimate using S-Parameter simulation. The Experiment Based on the procedures presented above, design the schematic of a small-signal RF amplifier for application at 800MHz, with minimum power gain of 12dB. Based your design on the NPN transistor BFR92A, and a supply voltage of 5V. Lab Report Submit your lab report to the technician of Intel Microelectronic Lab within 7 days from the date of experiment. You do not have to include the procedures. What is required is a paragraph on introduction stating the objective of the experiment, a few paragraphs on RF amplifier design procedure, the schematics and the result from Data Display window, include a short discussion of the results and a paragraph on conclusion. All report must be handwritten, except for graphics, which can be saved, and printed out later (You can also draw the results if you prefer). Marking Scheme Introduction to lab: 3 marks. Results (schematics, graphs and calculation): 5 marks. Discussion: 2 marks. TOTAL = 10 marks. References 1. D.M. Pozar, “Microwave engineering”, 3rd edition, 2005 John-Wiley & Sons. 2. R. Ludwig, R. Bretchko, “RF circuit design, theory and applications”, 2000 PrenticeHall International. F. Kung 19 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 0.12 110 0.10 100 phase(S(1,2)) mag(S(1,2)) Appendix I – Data Display for “bjt_amplifier.dsn” 0.08 0.06 0.04 90 80 70 0.02 60 0.00 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 0.0 1.0 0.1 0.2 0.3 0.5 0.6 0.7 0.8 0.9 1.0 0.7 0.8 0.9 1.0 freq, GHz freq, GHz 20 200 15 100 phase(S(2,1)) mag(S(2,1)) 0.4 10 5 0 0 -100 -200 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 0.0 0.1 0.2 0.3 0.4 0.5 0.6 freq, GHz S(2,2) S(1,1) freq, GHz Eqn K=stab_fact(S) Eqn D = mag(S(1,1)*S(2,2) - S(1,2)*S(2,1)) m1 freq=600.0MHz K=0.956 freq (50.00MHz to 1.000GHz) 1.2 m1 1.0 0.8 0.6 D K 0.4 0.2 0.0 -0.2 -0.4 -0.6 -0.8 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 freq, GHz F. Kung 20 Oct 2014 EMF4086 RF Transistor Circuit Design RT1 Appendix II – Data Display for “bjt_amplifier_600MHz.dsn” Eqn source_circle = s_stab_circle(S,51) Eqn load_circle = l_stab_circle(S,51) S(1,1) 0.263 / -114.092 S(2,2) 0.491 / -20.095 load_circle source_circle freq 600.0MHz indep(source_circle) (0.000 to 51.000) indep(load_circle) (0.000 to 51.000) Eqn Gain_10 = gp_circle(S,10,51) Eqn Gain_15 = gp_circle(S,15,51) Eqn Gain_20 = gp_circle(S,20,51) source_circle load_circle Gain_20 Gain_15 Gain_10 m1 m1 indep(m1)=28 Gain_20=0.755 / 35.369 freq=600.0000MHz impedance = Z0 * (1.271 + j2.579) indep(Gain_10) (0.000 to 51.000) indep(Gain_15) (0.000 to 51.000) indep(Gain_20) (0.000 to 51.000) indep(load_circle) (0.000 to 51.000) indep(source_circle) (0.000 to 51.000) F. Kung 21 Oct 2014