* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Test Procedure for the NCV8853GEVB Evaluation Board

Standing wave ratio wikipedia , lookup

Oscilloscope types wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Oscilloscope wikipedia , lookup

Audio power wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Index of electronics articles wikipedia , lookup

Analog television wikipedia , lookup

Superheterodyne receiver wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Phase-locked loop wikipedia , lookup

Oscilloscope history wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Integrating ADC wikipedia , lookup

Current source wikipedia , lookup

Wilson current mirror wikipedia , lookup

Radio transmitter design wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Surge protector wikipedia , lookup

Power MOSFET wikipedia , lookup

Operational amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Current mirror wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage regulator wikipedia , lookup

Power electronics wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Switched-mode power supply wikipedia , lookup

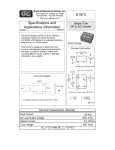

Test Procedure for the NCV8853GEVB Evaluation Board Table 1. DEMONSTRATION BOARD TERMINALS Pin Name VIN VOUT GND EN/SYNC PG PG+ Function Positive dc input voltage Regulated dc output voltage Common dc return Enable input and external clock synchronization input Digital power good output Power good pull-up. Use this pin only when pulling-up PG to an external voltage source. Table 2. ABSOLUTE MAXIMUM RATINGS (Voltages are with respect to GND) Rating Value Units Dc supply voltage (VIN) -0.3 to 36 V Dc supply voltage (EN/SYNC, PG, PG+) -0.3 to 6.0 V Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability. Table 3. ELECTRICAL CHARACTERISTICS (TA = 25°C, 6.0 V ≤ VIN ≤ 36 V, VEN/SYNC = 5.0 V, 0 ≤ IOUT ≤ 2.0 A, unless otherwise specified) Characteristics Output Voltage Voltage Accuracy Line Regulation Load Regulation Conditions Regulation IOUT = 1.0 A VIN = 13.2 V Switching Switching Frequency Soft-start Time SYNC Input Frequency Range Typical Value Units 5.0 2 0.04 0.12 V % % % 340 2.0 270 to 500 kHz ms kHz 3.33 5.0 A A 3.1 170 V °C Current Limit Average Current Limit Cycle-by-cycle Current Limit Input Undervoltage Lockout (UVLO) Thermal Shutdown 4/5/2013 Protections VIN decreasing TJ rising www.BDTIC.com/ON/ -1- www.onsemi.com PG PG_POS R6 VOUT U1 R1 GND VIN OPEN PG 1 PG VIN R2 30m 8 C1 0.1uF C3225X7S1H106K C2 C3 10uF 10uF C4 10uF VIN 10k EN/SY NC 2 C5 EN/SY NC 6800p R3 COMP C6 470p 3 FB 4 EN/SY NC ISNS COMP GDRV FB GND ISNS 7 6 GDRV VSW 5 R5 8.06k VOUT 15 uH XAL5050-153MEB GND D1 MBRA340T3 885300 R4 8.06k GND NTTFS5116PL Q1 L1 C8 VOUT C7 100 uF 0.1uF B45197A2107K409 GND 42.2k Figure 1: NCV885300EVB Board Schematic Operational Guidelines 1. Connect a dc input voltage, within the 6.0 V to 36 V range, between VIN and GND 2. Connect a load between VOUT and GND 3. Connect a dc enable voltage, within the 2.0 V to 5.5 V range, between EN/SYNC and GND 4. Optionally, for external clock synchronization, connect a pulse source between EN/SYNC and GND. The high state level should be within the 2.0 V to 5.5 V range, and the low state level within the 0.0 V to 0.8 V range, with a frequency within the 170 kHz to 500 kHz range. 5. Make sure that the output maintains 1 A at 5 volts. 6. Using an oscilloscope, test the switching frequency of the GDRV pin (pin 6) of U1. It should be ≈340 kHz when internally synchronized. 7. If using the optional external clock synchronization from step 4 the switching frequency should match the input source frequency. 8. To check the Input Undervoltage Lockout (UVLO) slowly decrease the input down towards 0 V. The board should turn off at around 3.1 V. 4/5/2013 www.BDTIC.com/ON/ -2- www.onsemi.com VIN IOUT ZOUT VEN VSY NC VEN Figure 2: NCV885300EVB Board Connections Power Good Operation 1. The Power Good pin (PG) allows you to digitally monitor the output voltage. When above 90% of the expected value, the PG signal is in a high state. By default, it is pulled high to VOUT through a 10kΩ resistor. 2. Optional: To pull the PG pin high using a signal other than VOUT, please make the following board modifications: a. Remove R1 from the board. b. Populate R6 with a 10 kΩ resistor. c. Connect the a voltage source between PG+ and GND (please see the Absolute Maximum Ratings table for more information). d. PG is now ready to digitally monitor VOUT using an external pull-up. 4/5/2013 www.BDTIC.com/ON/ -3- www.onsemi.com Typical Performance Regulation Figure 3: Line Regulation for 340 kHz and a 5.0 V output Figure 4: Load Regulation for 340 kHz and a 5.0 V output 4/5/2013 www.BDTIC.com/ON/ -4- www.onsemi.com