* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Low-Power Schottky TTL (74LS)

Survey

Document related concepts

Transcript

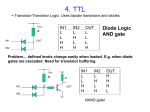

Low-Power Schottky TTL (74LS) 1/4 74LS00 quad 2-input NAND RB RC 20kΩ 8kΩ VCC=5V QP VA VB n 120Ω n QP2 4kΩ QS DD2 RBD 1.5kΩ RCD 3kΩ Vintage 1975 Scaled Resistors DTL input Why did we go back to DTL? n VOUT QO QD University of Connecticut RCP REP DD1 n n The Schottky diodes can be made smaller than QI, with lower parasitic capacitances, with post 1975 technology (6µm features). QS can not saturate, so it is not neccessary to remove its base charge with a BJT. 88 74LS Circuit Design 1/4 74LS00 quad 2-input NAND RB RC 20kΩ 8kΩ VCC=5V RCP n QP2 REP DD1 4kΩ QS DD2 RBD 1.5kΩ n QO RCD 3kΩ QD University of Connecticut VOUT RB and RC. Dominant in determining dissipation, these were scaled up by a factor of 8. 120Ω QP VA VB n n RBD and RCD. These were scaled up with R B and R C to maintain reasonable fanout. RCP and R EP. These affect speed, not power. They were not scaled significantly from 74S. DD1 and DD2. DD1 speeds the turn off of Q P2. DD2 sinks current from the load. Both improve tPHL. 89 74LS DC Dissipation 1/4 74LS00 quad 2-input NAND RB RC 20kΩ 8kΩ VCC=5V RCP 120Ω QP VA VB QP2 4kΩ QS DD2 1.5kΩ VOUT QO RCD 3kΩ QD University of Connecticut PL = REP DD1 RBD PH = PDC = 90 Advanced Low-Power Schottky TTL (74ALS / 54ALS Series) 1/4 74ALS00 quad 2-input NAND VCC=5V n RB RCS RC 40kΩ 60kΩ 15kΩ QIA VB RCP 50Ω QP QSB VA n n QP2 QIB REP DD1 4kΩ QS DSA VOUT DD2 QO DSB RBD 3kΩ RCD 6kΩ QD University of Connecticut n T.I., circa 1985 Derived from 74LS, but scaled-up resistors further decrease dissipation Improved transistor fabrication (3µm oxide-isolated transistors, vs. 6µm junction-isolated BJT’s for 74LS) Novel input circuitry also improves performance, but requires the use of lateral PNP’s. 91 74ALS Circuit Design 1/4 74ALS00 quad 2-input NAND VCC=5V RB RCS RC 40kΩ 60kΩ 15kΩ QIA VB RCP n QP QSB VA QP2 QIB REP DD1 4kΩ QS DSA RBD 3kΩ RCD 6kΩ QD University of Connecticut n VOUT DD2 QO DSB n n QSB increases base drive for QS, and improves tPHL. The input emitter followers compensate for the voltage shift of QSB. An added benefit is reduced IIL, and improved fanout. DSA and D SB remove base charge from QS, improving tPLH. tP P PDP 4ns (15pF) 1mW 4pJ 92 Fairchild Advanced Schottky TTL (74F /54F Series, a.k.a. FAST) 1/4 74F00 quad 2-input NAND RB 16kΩ RCS 10kΩ VCC = 5V n RCP 45Ω RC 4.1kΩ n QP VA VB QSB DIA QP2 DD1 REP 5kΩ DV DIB DSA DSB RBS 15kΩ University of Connecticut QS n VOUT n DD2 QO RBD 2kΩ RCD 3kΩ QD DBK DCK QK 1985, Fairchild Semiconductor Improved BJT fabrication DTL input with emitter follower provides good base drive to QS. “Miller killer” greatly improves switching performance DCO 93 74F /54F “Miller killer” The “Miller killer” circuit speeds up the low-to-high transition: VCC = 5V RCP 45Ω n QP DD1 REP 5kΩ DV QS n QP2 VOUT DD2 QO RBD 2kΩ n RCD 3kΩ QD University of Connecticut DBK n DCK QK DCO On a low-to-high transition, the voltage at the emitter of QP begins to increase while QO is still on. The varactor diode D V conducts, supplying base current to QK. (“K” for “killer”) QK turns on, and rapidly dissipates the charge stored in the basecollector capacitance of QO. Dynamic power dissipation is reduced by minimizing simultaneous conduction of the pullup and output transistors. 94 74F /54F Electrical Characteristics 1/4 74F00 quad 2-input NAND RB 16kΩ RCS 10kΩ VCC = 5V RCP 45Ω RC 4.1kΩ QP VA VB QSB DIA QP2 DD1 REP 5kΩ DV DIB DSA DSB RBS 15kΩ University of Connecticut QS VOH / VOL VIH / VIL Fanout P tP PDP 4.3 / 0.5V 2.1 / 1.8V 10 4mW 2.5 ns ( 15pF ) 10 pJ VOUT DD2 QO RBD 2kΩ RCD 3kΩ QD DBK DCK QK DCO 95 Advanced Schottky TTL (74AS /54AS Series) 1/6 74AS04 hex inverter RB 10kΩ RC 2kΩ VCC = 5V RCP 26Ω RBOD 30kΩ QP DS2 QP3 QS2 VIN RBP1 50kΩ DP QI REP 5kΩ DV DR1 QP2 VOUT QOD RBP2 1kΩ DR2 QS QIC QO DSI RBD 1kΩ RCD 2kΩ QD University of Connecticut DBK RBk 25kΩ RCk 100Ω QK DCO 96 74AS / 54AS Circuit Design n n n n n n Texas Instruments, circa 1985, derivative of 74LS series Input Transistor. Uses a PNP emitter follower like 74ALS. This lowers IIL and improves the fanout. Input Clamping. QIC replaces the input clamp diode used in other designs. Miller killer. The Miller killer is similar in design and operation to the subcircuit used in the 74F series. Pullup . QP3 increases the base drive for QP2 and also provides extra current to DV in the “Miller killer.” DP and DS2 help to discharge the base of QP2 during a high-tolow transition. University of Connecticut 97 Logic Family Comparison 100 Power Dissipation (mW) ECL III ECL 100k 74AS ECL 10k 74S RTL 930 10 74 74F 74LS 1 50 pJ line Improvements in the PDP result from circuit and device improvements. 74ALS 0.1 0.1 University of Connecticut 1 Within a particular family of logic gates, the PDP is fixed. Scaling resistors results in an even tradeoff between the power dissipation and the propagation delay. 10 tP (ns) w/ 15 pF load 100 98 TTL Off-Chip Data Rates tP (ns) 12 10 74ACT CMOS 8 6 4 2 0 74ALS (1mW) 74F (4mW) 74AS (20mW) 0 n n n 50 100 CL (pF) State-of-the-art CMOS circuits (0.35µ m feature size in 1997 A.D.) achieve on-chip propagation delays of about 100 ps! Driving highly capacitive off-chip loads, TTL outstrips CMOS by a factor of 2.5. Motherboards for PC’s and workstations use TTL extensively ... but this is changing as BiCMOS gains ground. University of Connecticut 99 TTL Logic Design Concepts University of Connecticut 100 TTL AND Gate 1/4 5408 / 7408 quad 2-input AND RB 4kΩ VCC=5V RCS 2kΩ RC 1.6kΩ DS VA QI QS2 VB QS QSD RSD 800Ω University of Connecticut RCP 130Ω n QP NAND n DL VOUT AND QO RD 1kΩ n Operation is similar to that of the NAND gate, but an extra inversion stage has been added. With all high inputs, QI is RA, QS2 and QSD are SAT, QS and QO are CO, and QP is FA. With a low input, QI is SAT, QS2 and QSD are CO, QS and QO are SAT, and QP is CO. 101 TTL NOR Gate 1/4 5402 / 7402 Quad NOR Gate RBA 4kΩ VA RBB 4kΩ RC 1.6kΩ QSA QIA n RCP 130Ω QP QIA VB VCC=5V n DL VOUT QSB QO n RD 1kΩ n University of Connecticut The NOR gate acts like two inverters, with paralleled drive splitters and a shared totem pole output. With a high input at A, QIA is RA, QSA and QO are SAT, and QP is CO. With both low inputs, QIA and QIB are SAT, QSA and QSB are CO, QO is CO, and QP is FA. The use of multiple emitters results in the “AND-OR-Invert” function. 102 TTL AND-OR-Invert Gates Shown is a “Three-input, two-wide” AND-OR-Invert Gate. n VCC=5V n RBA 4kΩ RBB 4kΩ QIA VA VB VC RC 1.6kΩ QP QSA DL VOUT QSB QO VA VB VC University of Connecticut QIA RCP 130Ω RD 1kΩ n Multiple-emitter BJT’s perform ANDing. Drive splitters provide the OR function. Together, the drive splitters and input transistors make up a “three-input expander.” The output stage is inverting as usual. Output stages are available alone and are called “line drivers.” 103 TTL XOR Gate RBA 4kΩ QIA VA VCC=5V RC 1.9kΩ RCX 2kΩ QSA RC 1.6kΩ QSDA QS DL VOUT QX1 VB QIB RC 1.9kΩ RCP 130Ω QP 1.2kΩ RBB 4kΩ 1/4 5486 / 7486 quad 2-input XOR QX2 QO RD 1kΩ VA VB QX1 QX2 VOUT QSB QSDB 1.2kΩ University of Connecticut 104 Open Collector TTL VCC=5V n 4kΩ 1.6kΩ n VA VB VC QI QS QO 1kΩ University of Connecticut VOUT n An “open-collector” TTL output can sink current, but can not source current. External pullup (inherently passive) is used. Open collector outputs can be wired together, resulting in the ANDing of those outputs. 105 “Wired Logic” with Open Collector TTL A A C B n n C B If either output A or B goes low, then C goes low. Hence, the wiring together of TTL open collector outputs results in the creation of the AND function. Wired logic cannot be implemented successfully with totem pole outputs. Can you see why? University of Connecticut 106 Integrated Injection Logic (I2L) University of Connecticut 107 I2L n n n TTL gates with even modest performance involve fairly complex circuits with low packing density. (74LS permits a packing density of 20 gates mm2 using 5µ m technology.) I2L allows a factor of ten improvement in packing density compared to 74LS - even approaching the packing density of CMOS. I2L exhibits much better PDP’s than TTL - even as low as 1 pJ! BUT... n I2 L can’t compete with CMOS in terms of DC dissipation. n I2 L exhibits a small logic swing compared to TTL or CMOS. University of Connecticut 108 Basic I2L A+B VCC IO A n n n n n A Q1 IO B B Q2 IO A+B Q3 The basic I2L building block is a multicollector BJT with a current source driving the base. The output transistors switch between cutoff and saturation. Multiple collectors are connected together to form “wired logic,” in similar fashion to open collector TTL outputs. How is “current hogging” prevented? What determines the fanout for I2L? What determines VOH? University of Connecticut 109 I2L and “Merged Transistors” VCC input VCC p n n n n n p n p n output The base of the PNP and the emitter of the NPN are both ntype, and connected to ground. They can be “merged.” Similarly, the PNP collector and NPN base are “merged.” Sometimes, I2L is also called MTL (Merged Transistor Logic). Whatever you call it, the structure is compact and results in high packing density in gates / mm2. University of Connecticut 110 Fabrication of Merged BJT’s VCC input C1 n+ p p n+ C2 C3 n+ n+ n+ n epitaxial layer n+ substrate n n n The PNP is lateral; the NPN is vertical, but “upside down.” All of the ground connections are made through the substrate, saving area on the top surface. The resistors and PNP emitters (“injector rails”) may be shared by multiple cells (“gate bars”) to further improve the packing density. University of Connecticut 111 Standard I2L Characteristics n 1ms propagation delay 100 10 n 1µs 100 n 10 1ns 1nW 10 100 1µW 10 power dissipation University of Connecticut 100 1mW n Fantastic on-chip PDP’s have been achieved (< 1pJ) with a 1V supply Off-chip loads are driven through TTL level translators. The packing density is ten times better than for 74LS. Fanout is limited to about 5. 112 Advanced I2L Circuitry n Schottky Integrated Injection Logic. The multiple collector regions are replaced by Schottky diodes. This improves the packing density. In addition, the reduced voltage swing improves the propagation delays. n Schottky Transistor Logic. STL is similar to Schottky I2L, but the switch transistors are Schottky clamped. Great performance has been demonstrated (0.2 pJ, 2.5 ns). The problem is complicated fabrication (two types of Schottky diodes must be made to allow finite voltage swing) and consequently low yield. n Integrated Schottky Logic. ISL is similar to Schottky I2L with two changes: The switch NPN is fabricated with the collector on the bottom and is clamped by an extra PNP. University of Connecticut 113