* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download DCDRew

Quantization (signal processing) wikipedia , lookup

Sound reinforcement system wikipedia , lookup

Multidimensional empirical mode decomposition wikipedia , lookup

Audio power wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Dynamic range compression wikipedia , lookup

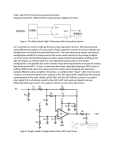

Negative feedback wikipedia , lookup

Integrating ADC wikipedia , lookup

Oscilloscope wikipedia , lookup

Public address system wikipedia , lookup

Rectiverter wikipedia , lookup

Oscilloscope types wikipedia , lookup

Oscilloscope history wikipedia , lookup

DCD ASIC Review 2014 1 • • • • DCD is implemented in UMC 0.18 um CMOS technology 3.2mm x 5mm DCD-B uses bump bonding on the UMC technology provided by EuroPractice. DCD has 256 analog channels each housing an input stage and ADCs (1 pipeline or 2 cyclic). ASIC Review 2014 2 DCDBPip TIA ADC 200 µm 5 mm ASIC Review 2014 3 • • • • The analog input stage performs various tasks. Keeps voltage constant, amplification, shaping, CM correction, pedestal correction The analog signal is digitized using current-mode cyclic or pipelined ADCs A large synthesized digital block decodes and derandomizes the ADC raw data which are then transmitted in a well sorted sequence to the DHP chips using fast parallel 8-bit digital outputs. ASIC Review 2014 4 • DCD Block ASIC Review 2014 5 • Analog Part with cyclic ADC ASIC Review 2014 6 • Analog Part with pipelined ADC ASIC Review 2014 7 • • • • Current-receiver based on a trans-impedance amplifier with a resistor on its output that amplifies the DEPFET current. Two current-mode cyclic ADCs (ADCR and ADCL) based on current-memory cells (CMC). Two-bit DAC for pedestal correction. Decoder for generating of the control signals for the ADC. ASIC Review 2014 8 • • • • The hearth of the block is a trans-impedance amplifier A ”bleeding resistor” Rs is connected between Vout and the input of the ADC. Since the ADC holds its input at a constant potential, the current flowing into the ADC is proportional to Iin The amplifier can operate in the mode to suppress common mode variations and amplify only the difference from the common mode signal. Novel voltage-drop insensitive current sources with enclosed NMOS transistors have been used for sensible currents like ISF ASIC Review 2014 9 • Signal receiver ASIC Review 2014 10 Common mode operation ASIC Review 2014 11 Single-Input Amplifier • • The single input amplifier is not able to distinguish between signal and crosstalk Amplifier bandwidth quite high ~ 100Mhz/2 5cm Crosstalk sources: Switching of DEPFET rows Fluctuations in power supply voltages EM environment Assumption: crosstalk affects all channels equally – “common mode noise” ADC ASIC Review 2014 12 Differential Amplifier • Differential amplifiers are not sensitive to common signals. ADC Output common mode feedback ADC + Input common mode feedback + ASIC Review 2014 13 Differential Amplifier • • • Problem: DEPFET signal is not differential. Idea: feed two DEPFET signals to a differential amplifier. Drawback: double hits are not amplified. ADC ADC Hit + + ASIC Review 2014 14 New: Multi-differential Amplifier • • Idea: extend the differential scheme to n inputs. The inputs are connected to n DEPFET rows. The amplifier is not sensitive common signals. ADC ADC ADC ADC ADC + ADC + ASIC Review 2014 15 New: Multi-differential Amplifier • • • The amplifier amplifies the difference from the mean value. In the case of large n, the mean value is not influenced by single hits. Behaves as the single input amplifier for the case of sparse signals. ADC ADC ADC ADC ADC + ADC + ASIC Review 2014 16 • • • • • • • • • The ADC uses redundant signed-digit (RSD) conversion. The algorithm starts with the comparison of the input signal with two thresholds, one positive and one negative. If the input signal is larger than the positive threshold, the pair of output code bits is set to 10, meaning +1, and a reference current is subtracted. If the input signal is lower than the negative threshold, the output code is set to 01 (-1) and the reference is added. If the input signal value is between the thresholds, the bits are set to 00 (0) and no arithmetical operation is carried out. The residue signal is multiplied by two and the result undergoes the same operation for the next bits. The conversion is not inuenced by the comparator osets, providing the osets are not larger than half of the threshold. Current-mode memory cells are used to implement the described A/D conversion algorithm. ASIC Review 2014 17 Cf Wr 1 Iin/Iout I1 Wr+Rd 2 Sw1 Iin/Iout 1 Sw1 4 Sw2 ASIC Review 2014 2 Sw2 C T1 A 3 Wr+Rd Wr A IO Ref VGS TC Ref2 sample state 1 sample state 2 S wr S r r 1. nc state3 lt lt 3. nc nc 2. 1. nc nc 4. 3. ck1 c c h0 wr lt memory cell l0 lt comparator rd rd lt lt rd 2. lt lt nc wr r 4. ck2 state1 rd state4 nc 2(S-h0R+l0R) ck3 state2 r nc h2 c wr 2(S-h0R+l0R) ck4 state3 2(2(S-h0R+l0R)-h1R+l1R) c state4 States: rd – read wr – write nc – not connected r – reset c – compare lt - latched sample state 1 S‘ l2 wr r r nc nc c c wr rd lt lt rd rd lt lt rd wr r r nc rd lt lt rd rd lt lt rd wr r r nc nc c c wr nc lt lt nc h1 l1 ck5 ck6 ck7 2(2(2(S-h0R+l0R)-h1R+l1R)–h2R+l2R) ck8 h3 ck9 2(2(2(2(S - h0R + l0R) - h1R + l1R) – h2R + l2R) – h3R + l3R) = Res Res ASIC Review 2014 l3 • ADC ASIC Review 2014 20 • Current memory cell ThHi ThLo Cf Cmp1 Cmp2 Rd WrB* Wr* Sw1 NotRd AND Not Wr 4 Sw5 NotWr Sub WrB Sw2 Add 2 VPSource VPSourceCasc Sw3 A 3 RefNWELL Iin Sw4 VAmpPBias DAC 1 NotRd En Logic SF AmpLow 24 μA VFBPBias RefIn RefIn VFBNCasc RefFB 12 μA VFBNBias (VPSource2) 24 μA TC RefIn ASIC Review 2014 21 • Comparator ResB Or th VPMOS LB VNMOS ResB RefIn 6X2 μA Th Comp In AmpLow IFBP 24 μA TP1 TP2 12 μA IFBN Vbias 24 μA Gate ASIC Review 2014 22 • Global bias block ASIC Review 2014 23 • Slow control ASIC Review 2014 24 • • • • • • • • • • • • • TCUM1 first implementation of the cyclic ADC based on current memory cells (CMC) – too slow and too large TCUM3 improved (for speed) implementation of the cyclic and pipelined ADC with CMCs – too large DCD1 72-channel readout chip for DEPFET – small cyclic ADCs (2/channel) and regulated cascode as receiver – 80ns sampling time and proper size – too high noise due to crosstalk DCD2 – fixed crosstalk problem (constant current consumption) – INL ~3.5 in some channels and noise ~50nA at 100ns sampling time DCDB1 256-channel chip with Belle II size – cyclic ADCs from DCD2 and transimpedance amplifers – works but noise a bit high at 100ns sampling time (120nA) DCDB2 – noise improved ~ 60nA at full speed – INL about 4 LSB in some channels DCDB4 cyclic – improved DCDB2 not tested yet DCDB pipelined – noise ~ 45nA at full speed – INL about 2.5 LSB (sometimes some channels have long codes) We believe, the problem has been understood and can be solved by resizing of transistors Still to be decided – should we use cyclic or pipelined version or both We need more measurements Measurements of DCD cyclic DC characteristics measurements ASIC Review 2014 25 Test all ADCs • Test results on DCD pipeline ADC gain 72nA/LSB (~110e @ gq 650pA/e) Noise: ~0.55LSB (60e @ gq 650pA/e) 90 80 1.4 1.2 70 DNL of All ADCs 5 DNL [ADU] 100 Peak-to-Peak INL of All ADCs INL [ADU] Mean Noise of All ADCs Noise [ADU] Gain [nA/ADU] Gain of All ADCs 4.5 10 9 4 8 3.5 7 1 60 3 50 40 0.6 30 220e 6 275e 0.8 2.5 5 2 4 1.5 3 1 2 0.5 1 0.4 20 0.2 10 0 0 20 40 60 ASIC Review 2014 80 100 0 0 20 40 60 80 100 0 0 20 40 60 80 100 0 0 20 40 60 80 100 26