* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download crooks

Portable appliance testing wikipedia , lookup

Mains electricity wikipedia , lookup

Alternating current wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Control system wikipedia , lookup

Automatic test equipment wikipedia , lookup

Curry–Howard correspondence wikipedia , lookup

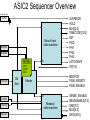

ASIC1 ASIC2 Things still to learn from ASIC1 Options for ASIC 1.011.1 1.2 Logic test structure for ASIC2 Things still to learn from ASIC1 Test beam a) b) c) d) e) Check labelling & operating conditions of hits-per-BT plot (back/red) Threshold scans of all sensors shown together, one plot for each of the four pixel architectures Spatial info – locations of noisy pixels Statistics of hits – beam profile? Per-pixel efficiency? Laser e) f) g) h) Bias optimisation for signal/noise Automated scan of every pixel to compare gain/noise Crosstalk analysis –scan around a 9x9 block of pixels – vs threshold Linearity Bench i) j) k) Threshold scan with VTH signals buffered / externally driven Full speed operation (189ns bunch crossing rate) Noise vs temperature Possible next sensors 3 weeks 4 weeks Sensor 1.01 24/3 a) b) c) d) e) ~ 8 weeks 19/5 (4 seats silicon) add preShape test structures extra pads? Sensor 1.2 h) i) j) k) PCB 1.0 bug fix SRAM write with full 3.3v level-shifting bug fix monostables (IOUTBIAS mirror transistors) bug fix ISENSEBIAS mirror transistor add nwell diodes around test structure pixels larger bond pads? Sensor 1.1 f) g) (4 seats silicon) add analog buffers for VTH and VRST signals? reduce / change pixel variants? tweak pixel design for noise/gain performance? … PCB 1.1 2nd hole for laser (4 seats silicon) PCB 1.X Possible next sensors Logic/Support Test Structure 12 weeks 14/7 a) b) c) d) e) f) g) h) i) j) k) 15/9 (+1 seat silicon) New test PCB(s) required Large pad-over-logic pad cells for bump-bond tests LVDS receiver and transmitter pad circuits Gray code counter for timestamp generation Clock generator (makes all sensor internal clocks from one external clock) Bunch train state machine Readout state machine Master controller (co-ordinates preceding logic blocks, resets, power-on safe states) Configuration controller (co-ordinates mask & trim programming, adding on-chip registers for current/voltage DACs etc. Current DAC circuits Voltage DAC circuits … ASIC2 Sequencer Overview Small test pad? OVRD Bunch train state machine MODE0 MODE1 MODE SEL • PRE-SPILL • SPILL • READ • IDLE REFCLK TOKIN TOKOUT SDATA Clk Gen En OVERRIDE HOLD MUX[2:0] TIMECODE[12:0] INIT FWD PHI1 PHI2 PHI3 LATCHSAFE OF[7:0] MSOPOR PIXEL RESETS PIXEL ENABLE Master En Readout state machine SENSE_ENABLE READENABLE[7:0] ORE[7:0] MUX[2:0] DATA[30:0] ASIC2 Services Sensor ID code …to readout unit DOUT Setup registers Current biases Voltage DACs CLK DIN Config controller DOUT_RDBK PHI1 PHI2 FAST PHI3 PHI1 PHI2 SLOW PHI3 PHI1 PHI2 RDBK PHI3 DIN_CONFIG BIAS1 BIAS2 BIAS3 BIAS4 VTH+ VTHVcasc1 Vcasc2 Example “1-seat” logic test structure 500x750 um logic blocks Wire bond pads for testing Bump bond pads • 240um bump bondable pads on 1mm pitch • Small wire-bond pads to test the generated logic signals • Implement as many of the logic blocks and signal distribution as possible • Folded design models a fullwidth logic slice serving a large array of pixels ASIC2 Concept • Logic columns – Power pads over the logic used to distribute global power supplies • Central row of control logic – 500um profile – Bump Bond Pads for control & IO signals • • • • • • Clocks Synchronisation Mode Configuration Serial data out Power