* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Properties of Digital Circuits

Electrical substation wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electrification wikipedia , lookup

Three-phase electric power wikipedia , lookup

Electric power system wikipedia , lookup

Audio power wikipedia , lookup

Stray voltage wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Current source wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

History of electric power transmission wikipedia , lookup

Power engineering wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Voltage optimisation wikipedia , lookup

Distribution management system wikipedia , lookup

Power inverter wikipedia , lookup

Mains electricity wikipedia , lookup

Opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

Power electronics wikipedia , lookup

Alternating current wikipedia , lookup

Buck converter wikipedia , lookup

Properties of Digital Circuits

Quantized States

Voltage Transfer Characteristic (VTC)

Voltage Levels

Noise Margins

Current Levels

Fan-In and Fan-out

Power Dissipation

Propagation Delay

Power-Delay Product

IC Packaging

Technology Trends of MOS Microprocessors and

Memories

ECE 3450

M. A. Jupina, VU, 2014

Some Key Lecture Objectives

Before performing the Properties of Digital Circuits practicum,

we need to look at the key properties of digital circuits used to

compare one technology with another.

How voltage levels of a technology not only define the logic

states of a technology, but also lead to a definition of noise

immunity for a technology.

An understanding of how current levels, “loading,” power

dissipation, and speed of operation are all inter-related.

Reference:

Fundamentals of Digital Logic, Chap 1, Sec 3.8, and App E.4.

ECE 3450

M. A. Jupina, VU, 2014

Transistor-Transistor-Logic (TTL)

TTL dominated the IC market from the 1960’s to

early 1980’s. This picture changed in the 1980s

due to two major factors:

Discrete logic gates in static CMOS

competitive in speed at a lower power cost.

The advent of programmable logic components such

as PLDs and FPGAs made it possible to program

complex random logic functions (equivalent to

hundreds of TTL gates) on a single component. This

results in a large reduction in board real-estate cost,

while adding flexibility.

ECE 3450

became

M. A. Jupina, VU, 2014

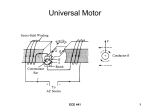

CMOS

CMOS stands for Complementary Metal-Oxide

Semiconductor. MOS field-effect transistors (nchannel and p-channel) are used to construct logic

gates.

FETs are voltage controlled and operate nearly as an

ideal switch.

MOSFETs advantages: Lower power consumption

than BJTs so billons of devices can be packed onto a

single chip (MOSFETs or what are now known as

FinFETs have dimensions in the deep sub-micron

range).

ECE 3450

M. A. Jupina, VU, 2014

CMOS

MOSFET

Gate Length

FinFET

Gate Length

Currently, how small is the gate length of a FinFET?

ECE 3450

M. A. Jupina, VU, 2014

Quantized States

Binary System

possible states: 1 or 0, on or off

positive logic: 1= high, 0 = low

negative logic: 1= low, 0 = high

Future Systems – multilevel logic

Ex: if three different on-off levels, then

23 = 8 logic states

ECE 3450

M. A. Jupina, VU, 2014

VTC of a TTL Inverter

Vi

Vo

Voltage Levels (VOH, VOL, VIL,VIH) are defined at dVo/dVi = -1

ECE 3450

M. A. Jupina, VU, 2014

VTC for a CMOS Inverter

Vout

V OH = V DD

Slope = –1

V OL = 0 V

VT

V IL

V IH

V

ECE 3450

( V DD – V T ) V DD

Vin

M. A. Jupina, VU, 2014

Table of Voltage Levels for

TTL Families

ECE 3450

M. A. Jupina, VU, 2014

PSPICE Schematic of LS7404 TTL Inverter

ECE 3450

M. A. Jupina, VU, 2014

PSPICE VTC Simulation of the LS7404

ECE 3450

M. A. Jupina, VU, 2014

PSPICE VTC Simulation of the LS7404

VIL = 0.7 V

VIH = 1.18 V

VOH = 4 V

VOL = 0.15 V

ECE 3450

M. A. Jupina, VU, 2014

Digital Properties Practicum

Measured VTC of LS7404

ECE 3450

M. A. Jupina, VU, 2014

Voltage Level Definitions

VIH – High Level Input Voltage

Vinput ≥ VIH to be recognized as a “1”

TTL Ex:

ECE 3450

VIH = 2V, thus at the input

a “1” is between 2V and VCC

M. A. Jupina, VU, 2014

Voltage Level Definitions

VOH – High Level Output Voltage

TTL Ex:

ECE 3450

VOH = 2.4V, thus at the output

a “1” is between 2.4V and VCC

M. A. Jupina, VU, 2014

Voltage Level Definitions

VIL – Low Level Input Voltage

Vinput ≤ VIL to be recognized as a “0”

TTL Ex:

ECE 3450

VIL = 0.8V, thus at the input

a “0” is between 0V and 0.8V

M. A. Jupina, VU, 2014

Voltage Level Definitions

VOL – Low Level Output Voltage

TTL Ex:

ECE 3450

VOL = 0.4V, thus at the output

a “0” is between 0V and 0.4V

M. A. Jupina, VU, 2014

Logic Level Matching

Levels at output of one gate must be sufficient

to drive next gate.

VOH > VIH

VOL < VIL

ECE 3450

M. A. Jupina, VU, 2014

Voltage Level Definitions

VLS – logic swing at the output

VLS = VOH - VOL

Ideally, should be as large as possible. Higher VLS reduces

ambiguity in the output logic state and increases noise

immunity.

VLS defines the range of output voltages that define the

unknown state, “X” state.

ECE 3450

M. A. Jupina, VU, 2014

Voltage Level Definitions

VTW – transition width at the input

VTW = VIH - VIL

Ideally, should be as small as possible. Lower VTW

reduces ambiguity in the input logic state and increases

noise immunity.

VTW defines the range of input voltages that define the

unknown state, “X” state.

ECE 3450

M. A. Jupina, VU, 2014

Voltage Levels Summary

“1”

“X”

“0”

ECE 3450

“1”

“X”

“0”

M. A. Jupina, VU, 2014

Noise in Digital Circuits

• Noise – unwanted variations of voltages and currents at the

logic nodes

• from two wires placed side by side

– capacitive coupling

• voltage change on one wire can

influence signal on the neighboring wire

• cross talk

– inductive coupling

• current change on one wire can

influence signal on the neighboring wire

v(t)

i(t)

• from noise on the power and ground supply rails

– can influence signal levels in the gate

ECE 3450

VDD

M. A. Jupina, VU, 2014

Noise Margin Definitions

NM’s define the amount of noise immunity in the

high or low level logic state.

NMH - High Level Noise Margin

NMH = VOH - VIH

NML - Low Level Noise Margin

NML = VIL - VOL

Ideally, the NM’s should be as large and as equal

as possible.

NM of a technology = min{NMH , NML}

TTL Ex: NMH = 2.4V - 2V = 0.4V

NML = 0.8V – 0.4V = 0.4V

ECE 3450

M. A. Jupina, VU, 2014

Noise Superimposed on TTL Signals

OR

ECE 3450

M. A. Jupina, VU, 2014

Noise Margin Question

A certain logic family has the following voltage parameters:

VIH = 1.18 V, VOH = 4 V, VIL = 0.7 V, VOL = 0.15 V

What is the largest positive-going noise spike that can be

tolerated?

NML = VIL – VOL = 0.55V

What is the largest negative-going noise spike that can be

tolerated?

NMH = VOH – VIH = 2.82V

ECE 3450

M. A. Jupina, VU, 2014

PSPICE Noise Simulation Demonstrating the

Concept of Noise Margin (LS7404)

ECE 3450

M. A. Jupina, VU, 2014

PSPICE Noise Simulation

V(IN) = Source + Noise

VOH

VOL

ECE 3450

Vpeak-to-peak

M. A. Jupina, VU, 2014

PSPICE Noise Simulation

V(OUT) for Vpeak= 0, 0.5, 1, 3.1V

Vpeak=0V

Vpeak=1V

ECE 3450

Vpeak=0.5V

Vpeak=3.1V

M. A. Jupina, VU, 2014

The Ideal Inverter

The ideal gate should have

–

–

–

–

–

infinite slope (gain) in the transition region

high and low noise margins equal to half the logic swing

a gate threshold located in the middle of the logic swing

input and output impedances of infinity and zero, respectively

infinite output drive capability (infinite output current or fanout)

VOUT

VOH = VCC

Ideal VTC

VCC = VSUPPLY

VTW=0 (Impossible to be in X state)

NMH = NML = VCC/2

dVo

VLS=VCC

dVi

Ri =

Ro = 0

Fanout =

VOL = 0V

ECE 3450

VIL=VIH= VCC/2

VIN

M. A. Jupina, VU, 2014

Current Level Conventions

Current out of a terminal is given as a negative value in Data Sheets.

Current into a terminal is given as positive value in Data Sheets.

ECE 3450

M. A. Jupina, VU, 2014

Table of Current Levels for

TTL Families

ECE 3450

M. A. Jupina, VU, 2014

Current Sourcing Versus Current Sinking

ECE 3450

M. A. Jupina, VU, 2014

Current Level Definitions

IOL – Low Level Output Current

“0”

IOUT

Maximum current that an output terminal

of a gate can sink when the output is “0”.

If |IOUT| > |IOL|, then eventually

VOUT > VOL

TTL Ex: IOL = +16mA, VOUT ≤ 0.4V

ECE 3450

M. A. Jupina, VU, 2014

Current Level Definitions

IIL – Low Level Input Current

“0”

IIN

Maximum current that an input terminal of a

gate can source when the input is “0”.

TTL Ex: IIL = -1.6mA, VIN ≤ 0.8V

ECE 3450

M. A. Jupina, VU, 2014

Current Level Definitions

IOH – High Level Output Current

“1”

IOUT

Maximum current that an output terminal of

a gate can source when the output is “1”.

If |IOUT| > |IOH|, then eventually

VOUT < VOH

TTL Ex: IOH = -400mA, VOUT ≥ 2.4V

ECE 3450

M. A. Jupina, VU, 2014

Current Level Definitions

IIH – High Level Input Current

“1”

IIN

Maximum current that an input terminal

of a gate can sink when the input is “1”.

TTL Ex: IIH = +40mA, VIN ≥ 2.0V

ECE 3450

M. A. Jupina, VU, 2014

TTL Example – LED Load

Which circuit would you use to drive an LED?

(Assume that VLED = ~1.7 V.)

I

+

1.7 V

I

-

+

1.7 V

ECE 3450

M. A. Jupina, VU, 2014

TTL Example – LED Load

Analysis of the first circuit:

I

+

1.7 V

For this circuit, Vout ≥2.4V and thus I ≥ 2mA > IOH ! (IOH = -0.4mA)

This TTL logic device can’t supply this amount of current since the

output voltage will decrease as the output current exceeds IOH.

Thereby, a “1” state at the output is no longer guaranteed.

ECE 3450

M. A. Jupina, VU, 2014

TTL Example – LED Load

Analysis of the second circuit:

I

-

+

1.7 V

If Vout = 0.4V, then I = 9 mA < IOL. ( IOL = 16 mA )

If Vout = 0V, then I = 10 mA < IOL.

The necessary output current can be supplied.

For TTL, the magnitude of IOL > the magnitude of IOH

ECE 3450

M. A. Jupina, VU, 2014

Fan-Out and Fan-In

Fan-out – number of load gates

connected to the output of the

driving gate

gates with large fan-out are slower

N

Fan-in – the number of inputs to

the gate

ECE 3450

M

gates with large fan-in are bigger

and slower

M. A. Jupina, VU, 2014

Static or DC Fan-Out

Fan-Out (N) is defined as the number of

loads (gate inputs) that can be driven by a

single gate output at DC or low frequencies.

Low Level Fan-out

NL =

I OL of the driving gate

I IL of the load gate

NH =

I OH of the driving gate

I IH of the load gate

High Level Fan-out

N = min{NL,NH}

Ex: For most TTL families, N = NL.

ECE 3450

M. A. Jupina, VU, 2014

TTL Static Fan-Out Example

NL

16mA

10

1.6mA

NH

400m A

10

40m A

N 10

ECE 3450

M. A. Jupina, VU, 2014

Dynamic Fan-Out

Additional current

due to the capacitive

load.

The impedance of a capacitor, (wC)-1, decreases as the frequency

increases. Therefore, the load current increases as the frequency

increases. This additional load current must be taken into account

when determining fan-out at high frequency.

Dynamic Fan-Out << Static Fan-Out

ECE 3450

M. A. Jupina, VU, 2014

Power Dissipation Definitions

Instantaneous power:

p(t) = v(t)i(t) = Vsupplyi(t)

Peak power:

Ppeak = Vsupplyipeak

Average power:

Vsupply

1 t T

Pav p(t )dt

T t

T

ECE 3450

t T

t

isupply ( t ) dt

M. A. Jupina, VU, 2014

Power Dissipation

Power consumption: how much energy is consumed

per operation and how much heat the circuit

dissipates

power supply sizing (determined by peak power)

Ppeak = Vsupplyipeak

– battery lifetime (determined by average power dissipation)

p(t) = v(t)i(t) = Vsupplyi(t)

Pavg= 1/T p(t) dt = Vsupply/T isupply(t) dt

– packaging and cooling requirements

Two important components:

static (DC) and dynamic

CMOS Example: PAV = VDD Ileakage + CL VDD2 f

ECE 3450

M. A. Jupina, VU, 2014

TTL Supply Currents

• The power supply current

is dependent on the

output state.

• ICCL > ICCH since

IOL > IOH

IIL > IIH

Note: these values are for a 7400 NAND Gate chip (total current for 4

NAND gates)

Power Dissipation of a TTL Gate

PAV PCCAV PEEAV

PAV

I CCH ( gate ) I CCL ( gate )

2

VCC

I EEH ( gate ) I EEL ( gate)

2

VEE

For VEE 0

PAV

ECE 3450

I CCH ( gate ) I CCL ( gate )

2

VCC

M. A. Jupina, VU, 2014

Power Dissipation of a TTL Gate

Example

What is the power dissipation of a single TTL NAND

gate (7400)?

8mA

I CCH ( gate)

2mA

4

22mA

I CCL ( gate)

5.5mA

4

2mA 5.5mA

PAV

(5V ) 18.75mW

2

ECE 3450

M. A. Jupina, VU, 2014

Power Supply Currents Versus

Frequency

10 KHz

ECE 3450

100 KHz

1 MHz

10 MHz

100 MHz

M. A. Jupina, VU, 2014

Propagation Delay Time

Vin

Vout

A measure of how

long it takes for a

gate to change state.

Ideally, should be as

short as possible.

tPHL - the time it takes

the output to go from

a high to a low

Average Propagation Delay Time

tp =

ECE 3450

t pHL t pLH

2

tPLH - the time it takes

the output to go from

a low to a high

M. A. Jupina, VU, 2014

Modeling Propagation Delay

Model circuit as a first-order RC network

R

vout

C

vin

I R IC

V Vout (t )

dVout (t )

C

R

dt

V

Vout (t) = (1 – e–t/)V ,where = RC

Time to reach 50% point is t = ln(2) = 0.69

0

t

ECE 3450

M. A. Jupina, VU, 2014

Modeling Propagation Delay

Driver Gate and Load Gate are modeled as a first-order

RC network

vout

R

vin

vS

C

+

-

Driver

ECE 3450

Load

M. A. Jupina, VU, 2014

CMOS Inverter as an Example

VDD

+

pullup

network

in

out

out

in

Drain

pulldown

network

VSS

ECE 3450

M. A. Jupina, VU, 2014

Switch Models of a CMOS Inverter

VDD

VDD

Rp

Vout = 0

Vout = VDD

Rn

Vin = V DD

ECE 3450

Vin = 0

M. A. Jupina, VU, 2014

CMOS Inverter: Transient Response

V DD

V DD

Rp

Capacitor Charging

Capacitor Discharging

V out

V out

CL

CL

Rn

V in

0

(a) Low-to-high output

ECE 3450

V in

V DD

(b) High-to-low output

M. A. Jupina, VU, 2014

CMOS Inverter Propagation Delay

• Propagation delay is proportional to the time-constant

of the network formed by the pull-down resistor or

pull-up resistor and the load capacitance.

tpHL = ln(2) Rn CL = 0.69 Rn CL

tpLH = ln(2) Rp CL = 0.69 Rp CL

tp = (tpHL + tpLH)/2 = 0.69 CL(Rn + Rp)/2

• To equalize propagation delay times make the onresistance of the NMOS and PMOS approximately

equal.

ECE 3450

M. A. Jupina, VU, 2014

PSPICE Simulation of Delay with RC Models (Switch)

ECE 3450

M. A. Jupina, VU, 2014

The Effect of Fan-Out on Propagation Delay

x

f

V out

To inputs of

x

n other inverters

To inputs of

n other inverters

Cn

(a) Inverter that drives n other inverters

(b) Equivalent circuit for timing purposes

V out for n =1

VDD

V out for n = 4

Gnd

0

Time

(c) Propagation times for different values of n

ECE 3450

M. A. Jupina, VU, 2014

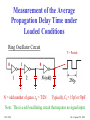

Measurement of the Average

Propagation Delay Time under

Loaded Conditions

Ring Oscillator Circuit

T = Period

10

10

01

N = odd number of gates, tp = T/2N

Typically, CL= 15pf or 50pF

Note: This is a self-oscillating circuit that requires no signal input.

ECE 3450

M. A. Jupina, VU, 2014

Maximum Frequency of Operation

FMAX

1

2 max(tPLH , tPHL )

TTL Ex: tPLH = 22ns, tPHL = 15ns

Fmax = 22 MHz

ECE 3450

M. A. Jupina, VU, 2014

Propagation Delay and Power

Dissipation (for a single gate)

TTL

{

CMOS {

TTL

Comparison

ECE 3450

M. A. Jupina, VU, 2014

Propagation Delay Versus Power

Dissipation (for a single gate)

Ideal

ECE 3450

M. A. Jupina, VU, 2014

Power Dissipation and Propagation Delay

• Propagation delay and the power consumption of a gate are

related

• Propagation delay is (mostly) determined by the speed at

which a given amount of energy can be stored on the gate

– the faster the energy transfer (higher power dissipation) the faster the

gate

• For a given technology, the product of the power consumption

and the propagation delay is a constant and is used as a benchmark to compare digital technologies.

– Power-Delay Product (PDP) specifies the energy consumed by the gate

per switching event

• An ideal gate is one that is fast and consumes little energy and

therefore the PDP should be as small as possible.

ECE 3450

M. A. Jupina, VU, 2014

Power-Delay Product Calculation

The average power dissipation (mW) by a single gate

is multiplied by the average propagation delay time

(ns) of a single gate to get the total energy (pJ)

dissipated by a gate for a given technology.

Compare the PDP of 4000 CMOS, ALS TTL, and ECL

CMOS:

PDP = (1mW) (100ns) = 100pJ

ALS TTL: PDP = (1.5mW)( 4ns) = 6pJ

ECL:

PDP = (40mW) ( 1ns) = 40pJ

ECE 3450

M. A. Jupina, VU, 2014

Common IC Packages

ECE 3450

M. A. Jupina, VU, 2014

Comparison of Microprocessors in 2001

ECE 3450

M. A. Jupina, VU, 2014

How much space does a single MOS

transistor occupy on a silicon chip?

Example: 100 million transistors on a 1cm x 1cm Si die.

108 transistors N N

1 transistor 1 transistor

or

2

2

-8

2

1cm

1cm

10 cm

1m m2

OR

1 cm

N

N

1 cm

104 transistors

N

cm

Source

or

1 transistor 1 transistor

-4

10 cm

1m m

L<0.1 mm

Gate

Drain

~1 mm

~1 mm

ECE 3450

M. A. Jupina, VU, 2014

Moore’s Law in Microprocessors

Transistors on lead microprocessors double every 2 years

1000

2X growth in 1.96 years!

Transistors (MT)

100

Pentium® IV

10

486

1

386

286

0.1

0.01

8086

8080

8008

4004

8085

0.001

1970

ECE 3450

Pentium® proc

1980

1990

Year

Courtesy, Intel

2000

2010

M. A. Jupina, VU, 2014

Intel 4004 Microprocessor

1971

2300 transistors

1 MHz clock

ECE 3450

M. A. Jupina, VU, 2014

Intel Pentium (IV) Microprocessor

2001

42 million transistors

2 GHz clock

ECE 3450

M. A. Jupina, VU, 2014

Evolution in DRAM Chip Capacity

human memory

human DNA

100000000

10000000

64,000,000

4X growth every 3 years!

16,000,000

Kbit capacity/chip

4,000,000

1000000

1,000,000

book

100000

256,000

64,000

16,000

10000

4,000

1000

1,000

256

100

64

10

1980

0.07 mm

0.1 mm

0.13 mm

0.18-0.25 mm

0.35-0.4 mm

0.5-0.6 mm

0.7-0.8 mm

1.0-1.2 mm

encyclopedia

2 hrs CD audio

30 sec HDTV

1.6-2.4 mm

page

1983

1986

1989

1992

1995

Year

1998

2001

2004

2007

2010

Clock Frequency

Lead microprocessors frequency doubles every 2 years

10000

2X every 2 years

Frequency (Mhz)

1000

100

Pentium® proc

486

10

8085

1

0.1

1970

ECE 3450

Pentium® IV

8086 286

386

8080

8008

4004

1980

1990

Year

Courtesy, Intel

2000

2010

M. A. Jupina, VU, 2014

Power Dissipation

Lead Microprocessors power continues to increase

100

Pentium® IV

Power (Watts)

Pentium® proc

10

8086 286

1

8008

4004

486

386

8085

8080

0.1

1971

1974

1978

1985

1992

2000

Year

Power delivery and dissipation will be prohibitive

ECE 3450

Courtesy, Intel

M. A. Jupina, VU, 2014

Power Density

Power Density (W/cm2)

10000

Rocket

Nozzle

1000

Nuclear

Reactor

100

8086

Pentium® IV

10 4004

Hot Plate

8008 8085

Pentium® proc

386

286

486

8080

1

1970

1980

1990

Year

2000

2010

Power density too high to keep junctions at low temp

ECE 3450

Courtesy, Intel

M. A. Jupina, VU, 2014

Power Dissipation (Battery Lifetime) is

an issue in all types of handhelds

ECE 3450

M. A. Jupina, VU, 2014

What is the Current Power Dissipation in

Processors?

• For a group exercise in class, select a processor manufactured

during the last three years and provide information on its power

dissipation by specifying the thermal design power (TDP).

• TDP is the maximum amount of heat generated by the

processor which the cooling system is required to dissipate.

• Look at processors manufactured by Intel, AMD, or Freescale

and use the manufacturers’ web sites to obtain the information.

Provide the website where you found your information.

Specify the properties of the processors such as clock

frequency, die size, number of transistors, and the number of

cores (if applicable).

• Use the excel spreadsheet form at the course website to report

your findings and email this file to your instructor when

completed.

ECE 3450

M. A. Jupina, VU, 2014