* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Hybrid Front-end board

Control theory wikipedia , lookup

Printed circuit board wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Rectiverter wikipedia , lookup

Control system wikipedia , lookup

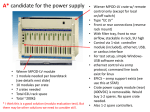

Status of LAV FEE electronics G. Corradi, C. Paglia, D. Tagnani & M. Raggi, T. Spadaro, P. Valente Front-end board (scheme) Supply control ± 6V ± 12 V CPU Power supply CAN-Open DAC ADC Trigger in Test pulse Threshold control • 32 FEE channels • Fits on mechanics VME 9U • Include services: Analog in Final board • Analog sums • Remote threshold • Individual channel threshold control • Pulsing system LVDS out LVDS driver LVDS out Pre-amplifier stage Dual thr. Discriminator & shaper Analog sum Analog sum out Hybrid Front-end board Prototype board This is the prototype used in the beam test. The design of this board is based: • 4 “ToT Mezzanine” with 2 channels each • This is the final card. •2 Manual threshold control • thr low • thr high • 2 Analog output SUM • 16 LVDS output (8CHx2thr) • Fits on mechanics VME6U. ToT Mezzanine This is the Time Over Threshold Mezzanine card. It has the section of: • Clamping • Amplification and Splitter • 2 channels of Discrimination. BOTTOM VIEW TOP VIEW Analog sum output • The Front End board is equipped with 32 analog channels • One board is used for 1 LAYER. • All outputs can not be housed in the board (there isn’t space on the front panel) Is possible carry out: 4Ch 4Ch • 1 SUM with 4 analog signals (One for each “BANANA”) • 1 SUM with 4 BANANAs (One for each half Layer) 4Ch 4Ch sum 4 sum 4 •The final motherboard will contains: • 8 SUM output with 4 channels. • 2 SUM output with 16 channels. sum 4 16Ch sum 16 Su • All SUMs must be clamped, because the sum of analog signal must not saturate the amplifier. • All SUMs must be buffered and matched 50Ω. Something like this… • This is a shot of what we are willing to have for the final version. • The small cards at the bottom are “ToT Mezzanine”. • The small cards at the top are “SUM Mezzanine”. • On the front panel fitted: • LVDS output for TDC • SUM output • Slow control connection. • On the rear panel fitted: • Analog input • Power connector. Threshold circuit • The threshold will be read and programmed remotely. (CANOpen) • With a dynamic range 0-500 mV • With a resolution 12 bits • With stability 2 LSB • Will be implemented the automatic threshold scan via slow control. Front-end diagnostics • For test the Front-end system, the board implements a TEST PULSE, which may be: • free-running (controlled by local CPU) • or on external trigger • The pulse can be: • equal for all channels • or a programmable pattern • The pulse can be programmed in level and in width: • 10-500 mV programmable amplitude • 10-50 ns programmable width • Stability level 1%. DCS requirements FEE boards • The structure of our slow control system consists of 4 CAN line : • 1 for Crate VME9U • 1 for Tell62 • 1 for HV system • 1 for 8 Front End board 9 DCS requirements FEE boards 1) VME 9U crate Monitoring Items Reading cycle per Status ON/OFF/Error 30 sec or even more Voltages/currents 30 sec or even more Crate temperature 30 sec or even more Fan Speed 30 sec or even more Actions: ON/OFF/Rest communication 2) TELL1 Monitoring (Ask Marco Sozzi) 3) HV Monitoring (to be defined) 4) FEE Monitoring dedicated CAN-Open line (8 boards) Monitoring Items: Reading cycle per Status ON/OFF/Error 30 sec or even more Voltages 30 sec or even more Boards temperature 30 sec or even more Thresholds (2x32 ch L/H) 30 sec or even more Actions: N channels Set threshold value (2x32 ch L/H) Set test pulse signal 10 CRATE LAV In order to start the production of the final project some information are still missing. We are trying to understand the right information of: • the power supply of the crates • the voltages supply (analog and digital) for slot • the maximum current for slot • the backplane connector schema Until we obtain these info we can not finalize the design. 11 Wiener 6020 LHC crate This is an example of a crate that has been taken into account, but it has a deficit in current on the 12V; Wiener 6021 LHCb TELL1 crate 10A 5V ±5V 5A 5A NO 0.5A This is another example of a crate, but it has not 12V; • Both crates are not suitable for our purposes! 12 CRATE LAV (survey questions) • This table shows the voltage and current that we estimate for the LAV station: • Volt 1 Tell62 1 FEE +3.3V 1 LED +5V +5Vstd +12V -12V + 48V PW 0.5A 2A 2A 50W/slot 0.5A 2A 2A 0.2A 60W/slot We don’t know the final consumption of TELL62 (Marco Sozzi will tell us the truth) • For each LAV’s Crate we need 1 TELL62 slot (mechanical 2 slots) and 19 VME 9U slots with only upper power connector. • We request only mechanical slot 9U, and 3U for backplane and power supply. • We don’t need the transition modules. Only J1 connector 9U x 240mm 3U Module 13 Conclusion • Beginning of final project waits results from the test beam – Time resolution – Charge resolution – Interaction with TELL1 and final TDC • Design of components for the final board done – Mother board design after definition of power supply (crate) – Need final output connection to TDC to be defined • DCS requires 4 lines per stations – Crate VME, TELL62, FEE board, HV NOTA A CRATE LAV 15