* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Topic 4 – Switching Circuits

Survey

Document related concepts

Transcript

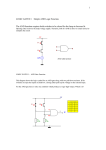

Topic 4 – Switching Circuits Serial vs. Parallel Transmission Circuit elements can be connected in either a serial or parallel manner. Serial implies a “one path through” approach, where a signal would pass through one element, then the next, then the next, and so forth. Serial vs. Parallel Transmission Parallel implies a “multiple elements at once approach,” where a signal passes through multiple elements simultaneously. Switching Circuits Switching circuits (digital logic circuits) are composed of combinations (serial or parallel) of elements known as gates. A gate is a high-speed electronic switching element which is capable of turning on or off within a few nanoseconds. In such a system, switching variables are associated with the input signals to the gates and switching functions are associated with the output signals…the switching function describes the input/output relationship. Electronic Circuits and Logic Values Truth tables that describe the operation of gates are presents in terms of high (H) or low (L) voltage (physical) values. The designed may choose to use these values to represent the logic values 0 and 1 in different ways. Positive logic uses voltage high (H) to represent 1 and voltage low (L) to represent 0. Negative logic uses voltage high (H) to represent 0 and voltage low (L) to represent 1. Mixed logic uses a combination of both. Electronic Circuits and Logic Values Mixed logic uses positive logic for some signals and negative logic for others…never different conventions for the same signals. A signal that is set to logic 1 is said to be asserted, active, or true. An active-high signal is asserted when it is high (H) and an active-low signal is asserted when it is low (L). If not asserted (set to logic 0), the signal is said to be deasserted, negative, or false. Logic Gates Now, let’s look at the seven types of digital logic gates. The roles of these gates are true and valid for active-high logic. For example, an AND gate will produce the logic AND of its two active-high inputs as an active-high output. Later, we will see what happens with active-low logic. The AND Gate A B Y This is an AND gate. Its truth table straightforward… So, if the two inputs signals A are asserted (high) the 0 output will also be asserted. 0 Otherwise, the output will 1 be deasserted (low). 1 is B 0 1 0 1 Y 0 0 0 1 The OR Gate A B Y This is an OR gate. Its truth table is also straightforward… So, if either of the two A B input signals are 0 0 asserted, or both of 0 1 them are, the output 1 0 will be asserted. 1 1 Y 0 1 1 1 The NOT Gate (Inverter) A Y This is a NOT gate or an inverter. It has only one input and is used to implement the A Y complement concept of switching algebra. 0 1 A bubble (seen here) at the output of any logic gate indicates that an internal logic 1 1 0 produces an external logic 0 and vice versa. Since the inverter has a bubble and does not implement any additional logic function, the output is simply the complement of the input. The NOT Gate (Inverter) The inverter can be seen as changing the polarity of a signal from active-high to active-low. As such, the bubble can be drawn at either the input or the output. By convention, the bubble is always drawn with the active-low signal. If the input is active-high, and the inverter is changing it to active-low, the bubble is drawn on the output. If the input is active-low and the inverted is changing to to active-high, the bubble is drawn on the input. The NAND Gate A B Y This is a NAND gate. It is a combination of an AND gate followed by an inverter. It’s truth table shows this… A B NAND gates have several interesting 0 0 properties… NAND(a,a)=(aa)’ = a’ = NOT(a) 0 1 NAND’(a,b)=(ab)’’ = ab = AND(a,b) 1 0 NAND(a’,b’)=(a’b’)’ = a+b = OR(a,b) 1 1 Y 1 1 1 0 The NAND Gate These three properties show that a NAND gate with both of its inputs driven by the same signal is equivalent to a NOT gate, a NAND gate whose output is complemented is equivalent to an AND gate, and a NAND gate with complemented inputs acts as an OR gate. Therefore, we can use a NAND gate to implement all three of the elementary operators (AND,OR,NOT). Therefore, ANY switching function can be constructed using only NAND gates. Such a gate is said to be primitive or functionally complete. NAND Gates into Other Gates (what are these circuits?) A Y NOT Gate A B Y AND Gate A Y B OR Gate The NOR Gate A B Y This is a NOR gate. It is a combination of an OR gate followed by an inverter. It’s truth table shows this… A B NOR gates also have several 0 0 interesting properties… 0 1 NOR(a,a)=(a+a)’ = a’ = NOT(a) NOR’(a,b)=(a+b)’’ = a+b = OR(a,b) 1 0 NOR(a’,b’)=(a’+b’)’ = ab = AND(a,b) 1 1 Y 1 0 0 0 Functionally Complete Gates Just like the NAND gate, the NOR gate is functionally complete…any logic function can be implemented using just NOR gates. Therefore, both NAND and NOR gates are very valuable as any design can be realized using either one. It is easier to build an IC chip using all NAND or NOR gates than to combine AND,OR, and NOT gates. Additionally, NAND/NOR gates are typically faster at switching and cheaper to produce. NOR Gates into Other Gates (what are these circuits?) A Y NOT Gate A B Y OR Gate A Y B AND Gate The XOR Gate (Exclusive-OR) A B This is a XOR gate. XOR gates assert their output when exactly one of the inputs is asserted, hence the name. The switching algebra symbol for this operation is , i.e. 1 1 = 0 and 1 0 = 1. Y A 0 0 1 1 B 0 1 0 1 Y 0 1 1 0 The XNOR Gate A B This is a XNOR gate. This functions as an exclusive-NOR gate, or simply the complement of the XOR gate. The switching algebra symbol for this operation is , i.e. 1 1 = 1 and 1 0 = 0. Y A 0 0 1 1 B 0 1 0 1 Y 1 0 0 1 Combinatorial Circuits Now that we know of all the logic gates, let’s look at circuits composed of a combination of these gates. We will do two things with these circuits… Analysis – Here, we will look at a circuit and derive an expression which summarizes its operation. This can be used to verify a circuit does what we want it to and/or to allow us to convert the circuit to a different form, either in fewer gates, or a different type of gates. Combinatorial Circuits Design and Synthesis – Here, we will begin with an expression or description and then design and then implement a circuit to fulfill that function. This circuit can be designed with gates, programmable logic devices (more about them later) or other logic elements. Now, let’s look at analysis of combinatorial circuits. Analysis: Algebraic Method Any given switching network can be completely represented by a switching expression. Remember, any switching expression may be written with AND, OR, and NOT gates. This also means any circuit can be completely represented with NAND gates or with NOR gates. As an example, let’s analyze a simple combinatorial circuit. Example #1 - Analysis Example #1 on the board. This is a combinatorial circuit. To analyze this circuit using algebraic analysis, we will derive switching expressions at each point propagating to the output of the circuit. Then, we will simplify the resulting expression and implement the resulting simplified expression in logic gates. Analysis: Timing Diagrams Another method of analyzing combinatorial circuits is through the use of timing diagrams. A timing diagram is a graphical representation of input and output signal relationships in a switching network. Often, intermediate signals are also represented. From this, if all possible input combinations and all outputs are shown, a switching expression for the circuit can be determined. Example #2 – Timing Diagrams Example #2 on the board. This is a combinatorial circuit and a corresponding timing diagram. We can examine this diagram to find all possible input combinations, and then learn the resulting output signal(s) at that point in time. In this example, let’s determine the truth table for the circuit and the minterms for the two outputs. Propagation Delay Ideally logic gates would function immediately. As soon as one of their input changed, the output would immediately change. In physical devices, the delay between an input change and the corresponding output delay is nonzero and is referred to as the propagation delay. This value is dependent on many issues such as the type of gate, logic family, temperature, and many other factors. Propagation Delay Many gates have different propagation delays for going high-to-low than for going low-tohigh. In a datasheet (the manufacture's specifications for their product), the low-tohigh delay is normally specified as tPLH and the high-to-low delay to normally specified as tPHL. When precise timing is not necessary, the average propagation delay is used for each gate. Synthesis of Combinatorial Logic Circuits Now, let’s turn to designing and implementing combinatorial logic circuits. AND-OR Networks As you’ll remember, AND gates implement product terms and OR gates implement sum terms. If a switching expression is expressed in the sum-of-products (SOP) form, it can be implemented easily using AND-OR networks. Each product term is implemented using an AND gate in the input stage of the network. Then, each product term is ORed together to implement the sum term. This will result in the desired output. Example #3 – AND-OR Networks Example #3 on the board. Here, we will implement the switching function f(p,q,r,s) = pr’ + qrs + p’s Each product term is implemented using an AND gate and then the sum term is implemented using an OR gate. Therefore, this expression is directly implemented in AND-OR logic. NAND Networks Any switching function can be implemented using just NAND gates. If we take the SOP function, complement it twice and apply DeMorgan’s Theorem, we will arrive at the NAND form of the expression… f(p,q,r,s) = (pr’ + qrs + p’s)’’ = ((pr’)’ (qrs)’ (p’s)’)’ = ((pr’)(qrs)(p’s))’ = NAND((pr’),(qrs),(p’s)) Thus, we can implement this directly in NAND logic. OR-AND Networks If a switching expression is expressed in the product-of-sums (POS) form, it can be implemented easily using OR-AND networks. Each sum term is implemented using an OR gate in the input stage of the network. Then, each product term is ANDed together to implement the product term. This will result in the desired output. Example #4 – AND-OR Networks Example #4 on the board. Here, we will implement the switching function f(a,b,c,d) = (a’+b+c)(b+c+d)(a’+d) Each sum term is implemented using an OR gate and then the product term is implemented using an AND gate. Therefore, this expression is directly implemented in OR-AND logic. NOR Networks Any switching function can be implemented using just NOR gates. If we take the SOP function, complement it twice and apply DeMorgan’s Theorem, we will arrive at the NAND form of the expression… f(a,b,c,d) = ((a’+b+c)(b+c+d)(a’+d))’’ = ((a’+b+c)’+(b+c+d)’+(a’+d)’)’ = NOR((a’+b+c)’, (b+c+d)’,(a’+d)’) Thus, we can implement this directly in NOR logic. Two-Stage Networks Networks like the AND-OR and OR-AND networks we have just seen are referred to as two-level networks. Inputs pass through two levels of gates before reaching the output. The first level is defined as the level that contains the gate that produces the output. The gates that receive the circuit inputs are on the second level. In general, a network has n levels if at least one input signal must pass through n gates to arrive at the output. Three-Stage Networks Switching functions in the POS or SOP form can be implemented directly in two-level networks when the inputs are available in both complemented and uncomplemented forms. A three-level network is required when only one form of the inputs is available. In this case, only NOT gates are needed on level 3 of the network. Two and Three Stage Networks Two-Stage Network p Three-Stage Network p U1A U1A U4A r r’ U2A U3A U1B Level 2 U2A U4B Level 1 U3A U1B Level 2 Level 3 Level 1 NAND Gate Networks At this point, you now have all of the tools necessary to take a switching function in minterm form and implement it in NAND logic. The implementation procedure is easy… (1) Express the function in minterm list form. (2) Write out the minterms in algebraic form. NAND Gate Networks (3) Simplify the function in SOP form using switching algebra. (4) Use switching algebra theorems to transform the expression into NAND formulation. (5) Draw the NAND logic diagram. As an example, let’s implement f(X,Y,Z) = Σ m(0,3,4,5,7) in NAND logic (Example on the board). Factoring In some cases, gates with a number of inputs required may not be available (i.e. we need a 5-input NAND gate and only have 3-input NAND gates). In such cases, factoring can be used to reduce the number of literals in large product or sum terms to values less than or equal to the number of available gate inputs. Factoring normally involves using the distributed law. There is no step-by-step way to perform it…it’s more of an art. Factoring Example #1 Given the expression f(A,B,C,D) = AB’ + AD’ + AC’ we can factor it… f(A,B,C,D) = A(B’ + D’ + C’) = A(BCD)’ Therefore, we can now implement this with one 3-input NAND gate and one 2input AND gate, instead of three 2-input NAND gates and one 3-input NOR gate. Factoring Example #2 The function f(a,b,c,d) = Σ m(8,13) needs to be implemented using only 2input AND and OR gates.