* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download - Muhazam

Integrating ADC wikipedia , lookup

Electrical engineering wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Electronic engineering wikipedia , lookup

Schmitt trigger wikipedia , lookup

Power electronics wikipedia , lookup

Surge protector wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Operational amplifier wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Current source wikipedia , lookup

Wilson current mirror wikipedia , lookup

Rectiverter wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Current mirror wikipedia , lookup

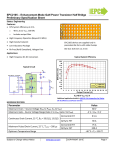

EEE1012 Introduction to Electrical & Electronics Engineering Chapter 7: Field Effect Transistor by Muhazam Mustapha, October 2010 Learning Outcome By the end of this chapter students are expected to: • Be able to explain some basic physical theory and operation of FET • Be able to do calculation on DC and AC analysis on FET circuit Chapter Content • • • • Theory of FET FET Operation DC Analysis AC Analysis Field Effect Transistor Field Effect Transistor • FET is a piece of electronic device that conducts electricity by the control of a gate • It can be considered as a voltage controlled resistor or voltage controlled current source • Current flows through the center body of channel from terminals called drain to source • Gate is a plate not touching the substrate Drain Gate Channel Source FET Types • There are many types of FET – MOSFET – Metal Oxide Semiconductor FET – JFET – Junction FET – NMOS – n-channel MOSFET – PMOS – p-channel MOSFET • We will cover mostly NMOS Channel Types • FET is also characterized by its channel • n-channel – The majority carrier in the channel is electron • p-channel – The majority carrier in the channel is hole Modes • Enhancement mode – FET is normally NOT conducting current even when given voltage at drain and source – Gate is to increase the current • Depletion mode – FET is normally conducting current when given voltage at drain and source – Gate is to decrease the current Depletion Mode • p-channel Drain +ve – Current flow is reduced by putting a positive voltage at gate to repel holes flow and finally block the current – The more positive the gate, the less current flow Gate Hole Flow +ve Gate’s electric field repelling holes p-channel −ve Source Depletion Mode • n-channel – Current flow is reduced by putting a negative voltage at gate to repel electrons flow and finally block the current – The more negative the gate, the less current flow Drain +ve Gate Electron Flow −ve n-channel Gate’s electric field repelling electrons −ve Source Enhancement Mode (PMOS) n-substrate • p-channel – When negative voltage is put to drain that is made of highly p dopant (p+), reverse bias junction is formed at drain – hence no current flows – Negative voltage is put to gate to attract holes and effectively compensate the reverse biases – until current can flow p-channel formation Drain −ve p+ Gate −ve Hole Flow p+ Gate’s electric field attracting holes +ve Source Enhancement Mode (NMOS) p-substrate • n-channel – When positive voltage is put to drain that is made of highly n dopant (n+), reverse bias junction is formed at drain – hence no current flows – Positive voltage is put to gate to attract electrons and effectively compensate the reverse biases – until current can flow n-channel formation Drain +ve n+ Gate +ve Electron Flow n+ Gate’s electric field attracting electrons −ve Source Circuit Symbol and Notations Depletion p-channel n-channel Enhancement JFET Operation Region I-V Characteristic ID, mA VGS = 5.0V Ohmic Region 15 VGS = 4.5V Saturation Region 10 VGS = 4.0V VGS = 3.5V 5 VGS = 3.0V VGS = 2.5V 0 0 1 2 3 4 5 Cutoff Region 6 7 8 9 VDS, V Operation Region • Cutoff – VGS < VT and VGD < VT – No current flow • Ohmic / Triode – VGS > VT and VGD > VT – Linear I-V characteristic Operation Region • Saturation – VGS > VT and VGD < VT – ID is controlled by VGS (Saturation Region Formula): I D K (VGS VT ) Conductance parameter 2 Threshold voltage – minimum voltage to form a conducting channel FET In Digital Circuit NAND, NOR and NOT Gates DC Biasing FET Biasing Refer to Giorgio Rizzoni’s Fundamentals of Electrical Engineering: Chapter 11.3, Example 11.4 • Biasing an FET means putting its VDS and ID into a desired position in the ID-VDS graph • This is done normally if we want the FET to operate in saturation region • The biasing process is a little tricky since ID is controlled by VG – not directly by VDS FET Biasing Refer to Giorgio Rizzoni’s Fundamentals of Electrical Engineering: Chapter 11.3, Example 11.4 • The biasing formula will also be a little different from BJT since in FET saturation region we have formula: ID = K(VGS-VT)2 • Another difference is that IG is zero (whereas IB is not zero in BJT) since the gate is not in contact with the channel FET Biasing Refer to Giorgio Rizzoni’s Fundamentals of Electrical Engineering: Chapter 11.3, Example 11.4 • The position of the biased FET’s VDS and ID is called Q point • The value of VGS is also required for the biasing • There are a few biasing configuration exist, but for the purpose of non-EE class, we will only study the most popular configuration called selfbias common source configuration – Refer to Giorgio Rizzoni’s Fundamentals of Electrical Engineering Figure 11.8(a) FET Biasing Refer to Giorgio Rizzoni’s Fundamentals of Electrical Engineering: Chapter 11.3, Example 11.4 RG = R1 || R2 R1 IG RG + VDS + VGS R2 − RS − ID RD ID RD + IG VDS VDD VGG VGG = (VDD)(R2)/(R1+R2) + VGS − − RS Thevenin’s Equivalent VDD FET Biasing Refer to Giorgio Rizzoni’s Fundamentals of Electrical Engineering: Chapter 11.3, Example 11.4 • The target of biasing process is to find the value of the resistors so that Q point is position at around VDD/2 in the ID-VDS characteristic graph • R1 and R2 will determine VGS • VGS will determine ID • ID = K(VGS−VT)2 • Then from KVL, VDS = VDD−ID(RD+RS) – This equation is what called load-line equation FET Biasing Refer to Giorgio Rizzoni’s Fundamentals of Electrical Engineering: Chapter 11.3, Example 11.4 Steps: • R1 and R2 will be combined using Thevenin’s theorem to form RG • Use KVL on GS loop to get VGS from RS and ID • Use saturation region formula to get a quadratic equation on VGS or ID, then solve the other one • Use KVL on DS loop (load-line equation) with the required VDS for the Q point to get RD FET Biasing • Class discussion: Giorgio Rizzoni’s Fundamentals of Electrical Engineering: pages 500 – 501, Example 11.4 AC Analysis AC Analysis • AC analysis is done to determine the performance of FET amplifier circuit • There are a few parameters of interest, like input and output resistance, but for the purpose of non-EE class, we will do only voltage gain (no current gain, why?) • AC analysis is done after biasing is completed and assuming there is some AC signal being introduced into the circuit as superimpose on top of the DC values (biasing) AC Analysis • The oscillation of the input and output signals will be denoted by Δ (delta) • For this class we will consider the I-V characteristic of the sinusoidal input and output signals will be the same as the DC relationship – next slide AC Analysis R1 RD ΔVO ΔVG VDD R2 RS AC Analysis I DMax K (VGSMax VT ) 2 I DMin K (VGSMin VT ) 2 I D I DMax I DMin VO VDS RD I D Voltage Gain VO VG AC Analysis In the formula for ΔVO, it only depends on ΔID even though from the KVL at the output it should also depends on ΔIS. The reason for this is in real circuit we put a capacitor across RS which effectively SHORTS circuit RS when AC current flows – means we can disregard RS in AC analysis formula. R1 RD ΔVO ΔVG VDD R2 RS AC Analysis • Self exercise: Based on Giorgio Rizzoni’s Fundamentals of Electrical Engineering Example 11.4, get the Vp-p of output if the Vp-p of input is 5mV