* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Clocking-Strategies - KIT

Transmission line loudspeaker wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Rectiverter wikipedia , lookup

Atomic clock wikipedia , lookup

Control system wikipedia , lookup

Curry–Howard correspondence wikipedia , lookup

Digital electronics wikipedia , lookup

Phase-locked loop wikipedia , lookup

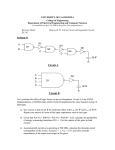

(Neil west -p:-317-357) Finite-state machine (FSM) which is composed of a set of logic input feeding a block of combinational logic resulting in a set of logic output. Operation: determining the “next state” as a function of the “current state” and the external inputs. Output Input Current state bits Combinational Logic Next state bits Q D Clock Single-phase clock The time before the clock edge that the D input has to be stable is called the Setup time (Ts) The time after the clock edge that the D input has to remain stable is called the Hold time (Th) The delay from the positive clock input to the new value of the Q output is called the clocked-to-Q delay(Tq) Clock time or Cycle time (Tc) Cycle Time (Tc) Clock Setup Time (Ts) Data Hold Time (Th) Q Clock-to-Q delay(Tq) In positive level-sensitive latch because the D input is passed to the output when the clock is high. The D input must be stable for a short time before and after the negative clock transition By combining two level-sensitive latches, one positivesensitive and one negative-sensitive can construct edgetriggered register. Cycle time: Tc = Tq+Td+Ts Td is the delay through combinational logic Logic delay of block must satisfy Tda<Tc1-Tqa-Tsb Tdb<Tc2-Tqb-Tsb Latch A C Tq Combinational Logic Tda Latch Ts B Combinational Logic Tdb C Clock Tc=Tda+Tdb+[2(Tq+Ts)] Latch C C In synchronous system, if the data input to a register dose not obey the setup and hold-time constraints, then potential clock race problems may occur. Hold time violation : Tc2>(Tc1+Tq1) Setup time violation : (Tc1+Tq1) - Tc2 is larger than the cycle time, Tc then the data will arrive late at M2 Reg D q Tq Combinational Logic Tda Reg D Ts C C M1 Clock Delay Tc1 q M2 Delay Tc2 PLL is used to generate internal clocks on chip for two main reasons 1) To synchronization the internal clock of a chip with an external clock. 2) If it is desired to operate the internal clock of a chip at a higher rate that the external clock input. Chip that receives an external clock that is internally buffered The delay time is clock-buffer delay + the RC delay to the register + clock to Q delay of the register and the output buffer delay PLL senses the internal clock at the input of the register, it also receives the input clock. PLL generate a clock that is in phase with the input clock. By including divider in the PLL loop the on chip frequency may be increased by the divider ratio. /n Phase Detector Reference Clock U D Charge Pump Filter VCO n*fin The phase detector detects the difference between the reference clock and VCO clock and applies charge-up or charge-down pulses to the charge pump. The loop filter filters these pulses and applies the resulting control voltage to the VCO. The VCO changes oscillation frequency depending on the control voltage. Thus the total system forms a feedback system where the VCO is locked to the reference clock. Metastable state: The output is in an indeterminate state between 0 and 1. From the probability theory, the mean time between the failure of the output to be resolved with in some time(tf)(MTBU) is given by tf=The time after the change in clock by which the latch output must be resolved. fc=the frequency of the clock fd=the frequency of data T0=Flip flop propagation delay τr=Time constant of resolution of the latch Independently clocked systems Synchronizers are used at the interface between independently clocked systems. Asynchronous data in Reg D q C Clock Reg D q C synchronous data out Phi1(t) . phi2(t) =0 for all t. During Phi1=1: charges the gate capacitance of the inverter and the out put capacitance of the transmission gate(c1). During phi2=1 the stage-1 transmission gate opens and the inverse of the stored value on C1 is placed on C2. phi1 phi2 Phases must not overlap: non-overlap region clk signal may be passed through a transmission gate to equalize delay with respect to - clk Dynamic single clock latches Dynamic latches storing data on gate capacitance of inverter (or logic gate) Can be clocked at high frequency since very little delay in latch elements Examples: (a) or (b) show simple transmission gate latch concept and (c ) tri-state inverter dynamic latch holds data on gate when clk is high, (d) and (e) dynamic D register Operation of the un buffered L1 latch: Assume D and clock was high, then X is initially low and Q is high. With the clock low ,high to low transition on D causes X to go high, which turns P2 off, holding the value at the Q output. If D was low when the clock is high, then X is high and Q is low, if D is high when clock is low, P1 is turned off , holding X high, then Q is holding low P3 feedback transistor is added to counteract noise sources and leakage at X. Combines NP Domino logic sections with C2MOS latch n-logic block can drive p-logic block or another n-logic block with a static inverter similarly for a p-logic block Must end in a C2MOS latch clk logic: (a) prechrg on clk=0, eval clk=1 -clk logic: (b) pre on clk=1, eval on clk=0 clk logic can feed –clk logic & vice-versa can mix static logic with NP domino logic Rules to avoid race conditions: During precharge, logic blocks are OFF During eval, internal inputs make only one transition Pipeline design: Even number of inversions between C2MOS R. W. Knepper SC571, page 5-72 Compact implementation of of two phase dynamic registers shown at left using a tri-state buffer form. Transmission gate and inverter integrated into one circuit Two phase dynamic registers and logic is often preferred over single phase because Due to finite rise and fall times, the CLK and CLK’ are not truly nonoverlapping Clock skew often is a problem due to the fact that CLK’ is usually generated from CLK using an inverter circuit and also due to the practical problem of distributing clock lines without any skew n- transistor can replace the transmission gate p feed-back transistor to provide fully logic levels Single clock version using p and n transistor Clock qualification technique Top figure shows n type logic stages with two phase non-overlapping clocks phi1 high: precharge phi1 logic, evaluate phi2 logic phi2 high: precharge phi2 logic, evaluate phi1 logic Bottom figure shows use of Domino logic having both phi1 and phi2 logic stages Each block is separated from other by a clocked pass gate register/latch to store the logic result Note that inverters must be used between successive stages of the same clock logic Simple four-phase structure operation: during clk1=0 node n1 precharges When clk2=1 and ck1=1, node n1 conditionally discharges. When clk2 falls to 0, this value is held on the node n1 regardless of the state of the input D. During clk3=0 ,Q is precharge , During clk4=1, clk3=1, Q node is conditionally discharged according to the state of node n1 Due to charge sharing during the clk2 phase, clk2 is sometimes replaced by clk12 (and clk4 is replaced by clk34) by keeping clk12 high during both clk1 and clk2 phases. Four phase logic structure shown using transmission gate to isolate data on z during hold time Operation: during clk1 time, -clk12 is down causing Pz to be precharged to Vdd during clk2 time, -clk12 is still down keeping precharge active, but clk23 goes high thus precharging node z during clk3 time, precharge of node Pz ends and evaluation begins with Xgates still closed during clk4 time, the transmission gate opens and the correct data is isolated on node z Using four different type logic gates as shown in previous chart (where Type refers to the evaluation phase time), four phase logic can be used in pipelined logic structures where each type must be used per the allowable interconnection diagram at the left a Type 1 gate can feed Type 2 or Type 3 gates a Type 2 gate can feed Types 3 and 4 a Type 3 gate can feed Types 4 and 1 a type 4 gate can feed Types 1 and 2 Single phase clocking scheme is preferable Two phase clocking scheme is used in RAMs, ROMs, and PLAs Single-phase clocking for complex, high speed CMOS circuits. Special clocks are normally generated using self timed logic circuits. Alternative clocking scheme may be of used in special situations 1) 2) Two main technologies: A single large buffer A distributed clock tree approach