* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download PI4MSD5V9545A/B/C Product Databrief NEW PRODUCT

Variable-frequency drive wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Alternating current wikipedia , lookup

Stray voltage wikipedia , lookup

Power electronics wikipedia , lookup

Voltage regulator wikipedia , lookup

Electrical substation wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage optimisation wikipedia , lookup

Control system wikipedia , lookup

Crossbar switch wikipedia , lookup

Mains electricity wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

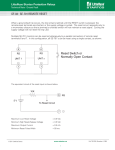

NEW PRODUCT BRIEF Product Databrief PI4MSD5V9545A/B/C SWITCHING SOLUTIONS 4 Channel I2C/SMBus Switch with Interrupt Logic and Reset The PI4MSD5V9545A is a quad 1-of-4 bidirectional translating switch, controlled via the I 2 C /SMBus. The SCL/SDA upstream pair fans out to four SCx/SDx downstream pairs, or channels. Any individual SCx/SDx channel or combination of channels can be selected, determined by the contents of the programmable control register. Four interrupt inputs, INT0 to INT3, one for each of the downstream pairs, are provided. One interrupt output, INT, acts as an AND of the four interrupt inputs. An active LOW reset input allows the PI4MSD5V9545A/45B/45C to recover from a situation where one of the downstream buses is stuck in a LOW state. Pulling the RESET pin LOW resets the I2C/SMBus state machine and causes all the channels to be deselected as does the internal power-on reset function. The pass gates of the switches are constructed such that the VCC pin can be used to limit the maximum high voltage which will be passed by the PI4MSD5V9545A/45B/45C. This allows the use of different bus voltages on each pair, so that 1.2V, 1.8V or 2.5V or 3.3V parts can communicate with 5V parts without any additional protection. External pull-up resistors pull the bus up to the desired voltage level for each channel. All I/O pins are 5V tolerant. T h e P I 4 M S D 5 V 95 4 5 A , P I 4 M S D 5 V 95 4 5 B a n d PI4MSD5V9545C are identical except for the fixed portion of the slave address. Block Diagram Features ÎÎ1-of-4 bidirectional translating multiplexer 2 ÎÎI C-bus interface logic; compatible with SMBus standards ÎÎOperating to 5.5V power supply voltage range of 1.65V ÎÎAllows voltage level translation between 1.2V, 1.8V, 2.5V, 3.3V and 5V buses ÎÎLow standby current ÎÎLow Ron switches ÎÎChannel selection via I2C-bus ÎÎPower-up ÎÎNo glitch on power-up ÎÎSupports ÎÎ5V ÎÎ0 with all multiplexer channels deselected hot insertion tolerant inputs Hz to 400 kHz clock frequency ÎÎESD protection exceeds 2000V HBM per JESD22-A114, and 1000V CDM per JESD22-C101 ÎÎLatch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA ÎÎPackages offered: SOIC (S20), TSSOP (L20) PI4MSD5V9545A/45B/45C SC0 SC1 SC2 SC3 SD0 SD1 SD2 SD3 GND VCC RESET SCL SDA INT[3:0] Switch Logic Logic Power-on Reset Input Filter I2C Bus Control A0 A1 A2 Interrupt Logic INT www.pericom.com | 1-408-232-9100