* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Sample-and-Hold Design Eric Sorensen March 16, 2012

Distributed element filter wikipedia , lookup

Cellular repeater wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Phase-locked loop wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Power dividers and directional couplers wikipedia , lookup

Index of electronics articles wikipedia , lookup

Regenerative circuit wikipedia , lookup

Surge protector wikipedia , lookup

Integrating ADC wikipedia , lookup

Current source wikipedia , lookup

Voltage regulator wikipedia , lookup

Integrated circuit wikipedia , lookup

Power MOSFET wikipedia , lookup

Schmitt trigger wikipedia , lookup

Oscilloscope history wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Radio transmitter design wikipedia , lookup

Power electronics wikipedia , lookup

Wilson current mirror wikipedia , lookup

Two-port network wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Operational amplifier wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Current mirror wikipedia , lookup

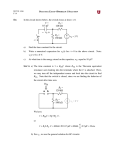

Sample-and-Hold Design Eric Sorensen March 16, 2012 Abstract This report describes the design of a fully-differential precision sample-and-hold amplifier, providing high accuracy, low droop, and fast acquisition time. Contents 1 Introduction 1.1 Design Requirements . . . . . . . . . . . . . . . . . . . . . . . 1.2 C-Pi Library . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 3 4 2 Functional Blocks of a Differential SHA 2.1 Topology . . . . . . . . . . . . . . . . . 2.2 Input Buffer . . . . . . . . . . . . . . . . 2.3 Switch . . . . . . . . . . . . . . . . . . . 2.4 Output Buffer . . . . . . . . . . . . . . . . . . . 5 5 6 7 7 3 Design Details 3.1 Current Mirror . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2 Feedthrough Capacitance . . . . . . . . . . . . . . . . . . . . 3.3 Hold Capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . 8 8 9 10 4 Results 4.1 Acquisition Time . . . . . . . . 4.2 Aperture Time . . . . . . . . . 4.3 Power Supply Rejection Ratio . 4.4 Output Impedance . . . . . . . 4.5 Power Consumption . . . . . . 4.6 Slew Rate . . . . . . . . . . . . 4.7 Feedthrough Attenuation Ratio 4.8 Sample/Hold Current ratio . . 4.9 Full Power Bandwidth . . . . . 4.10 Accuracy . . . . . . . . . . . . 4.11 Hold Mode Settling Time . . . 4.12 Droop Rate . . . . . . . . . . . 4.13 Step Hold . . . . . . . . . . . . 11 11 11 13 13 14 15 16 16 17 17 18 18 18 5 Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Bibliography 20 1 A Final Schematic 21 B Device Plots 23 B.1 Gummel Plots . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 B.2 Early Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 2 Chapter 1 Introduction This paper discusses the design of a fully-differential precision sample-andhold amplifier (SHA). SHA’s are a critical component in digitizing analog signals. They are usually found at the input of analog-to-digital converters (ADC). During the acquisition phase of the ADC, the SHA holds the output voltage at a constant level. This allows accurate sampling of high-frequency signals. 1.1 Design Requirements Acquisition time: 100 ns (5 V step to 0.1%) Aperture time: 5 ns V Slew rate: 0.2 ns Feedthrough attenuation ratio: 80 dB Droop Rate: 10.0 mV ms Signal transfer nonlinearity: 0.1% Hold mode settling time: 50.0 ns Power dissipation: 750mW Sample/Hold Current Ratio: 103 Output Impedance: 20Ω HOLD step: 0.1mV with C = 1.0 pF Hold capacitor charging current: 5 mA Supply voltage rejection ratio: 80 dB Full Power Bandwidth: 100kHz Input Impedance: 100kΩ Power Supply: 5V Signal range: 2.5V 3 1.2 C-Pi Library The design is implemented using the provided C-Pi library. This library includes 3 NPN transistors, 3 PNP transistors, and two resistors. Although it is not currently in use, the library has historically been used for integrated circuit designs and is characteristic of transistors in real-world usage. As such, the use of the library imposes some design constraints. The first step in the design process is to characterize the devices in the C-Pi library. Gummel plots were generated for each of the NPN devices to determine the ideal operating points. The PNP transistors are assumed to function similarly to their NPN counterparts for biasing. The early voltage of the transistors is calculated by plotting the saturation current against both the base-emitter voltage and the collector-emitter voltage. The saturation current is extrapolated back to find the x-intercept. The early voltage of the wn2, wn8, wn32 transistors was found to be 22.0, 21.1, and 16.0 respectively. All the plots which were used to characterize the devices can be found in Appendix B. The final schematic can be found in Appendix A. 4 Chapter 2 Functional Blocks of a Differential SHA Amplifier Figure 2.1: Functional Diagram of an SHA. Figure from [Vorenkamp] The basic building blocks of an SHA are shown in Fig. 2.1. During the tracking phase, the switches are closed and the buffered input is allowed to charge the capacitors. In the hold phase, the switches are opened and the output is maintained by the slow discharging of the capacitors. 2.1 Topology Using a differential design is critical when designing an SHA using bipolar technology because many of the errors inherent in SHA’s can be rejected as common-mode signals. For instance, the droop across a single capacitor is a significant design constraint when dealing with finite base currents in BJT technology. However, in a differential design the two hold capacitors each have a similar droop which cancels out as a common-mode signal. After doing a thorough literature search, a differential SHA topology was 5 Figure 2.2: Differential SHA Topology found as a reference design [Vorenkamp]. This topology can be seen in Fig. 2.2. 2.2 Input Buffer Transistors Q1-Q4 and resistors R1-R4 form a unity-gain input buffer (provided R1 = R2 = R3 = R4). Using diodes in the load of the differential pair adds a 1/gm series resistance to the load and improves the unity-gain accuracy by about 10%. The following transfer function was found for the input buffer using halfcircuit analysis: Vo = −gm(R1 + 1+ R2 Rπ 1 gm ) + gmR2 Vin (2.1) Using typical values of Ic = 1mA, β = 100, and R1−4 = 500 this reduces to: Vo = 0.9906Vin (2.2) Slightly increasing the values of the top resistors (R1) brings it to a gain of exactly one. The input resistance is found using the same small-signal model: Zin = (Rπ + R2 + gmR2 Rπ) (2.3) This shows that the most efficient way to increase the input resistance is to increase the Resistor values. 6 2.3 Switch The switch is made up of transistors Q5, Q6, and Q7. When the SAMP signal is high in reference to the HOLD signal Q6 is turned off, and Q5 acts like as emitter-follower. This low-impedance node can quickly charge the hold capacitor. During the HOLD phase, Q5 is turned off, and Q6 sources all of the current for I2 (which must be drawn from the load of the buffer). This shields the holding capacitor from the input signal. The voltage levels for the SAMP and HOLD signals must be chosen carefully so that VBC of Q5, Q6, and Q7 remain reversed biased throughout the entire operating range of the amplifier. 2.4 Output Buffer Q8, Q9, and Q10 form an emitter-follower unity-gain output buffer. The current gain of this buffer must be high enough that a very small current is drawn from the holding capacitor during the hold phase. In the final design, transistor Q10 is replaced with a Darlington pair to further decrease the loading on the capacitor. 7 Chapter 3 Design Details 3.1 Current Mirror A supply-independent Widler source with helping transistors is used to provide a reference for the current mirrors in the circuit. Initially a simpler current mirror was used, but the PSRR was limited to 70dB which did not meet the specifications. Figure 3.1: Current Mirror Although the SHA seems to startup and run correctly without it, this current source needs a startup circuit to ensure it reaches the correct operating point. This can be seen in Fig. 3.2. Although this startup circuit was not included when most of the results were calculated (it was added after the graphs were generated) it has a negligible effect on the circuit once it is in operation. The startup circuit is used in the Power Consumption results graph where it has a meaningful impact. The sink currents were initially chosen to be reasonable values for the 8 Figure 3.2: Startup Circuit devices used (according to the gummel plots). The switching current limits the speed at which the capacitor can be charged, so it was set at 2.5mA. The output buffer was initially set at 2.5mA, but the output impedance of the circuit was too low so it was increased to 5mA. The input buffer operates with collector currents of 2.5mA. 3.2 Feedthrough Capacitance Figure 3.3: Feedthrough Capacitors One of the interesting aspects of this design is the method in which the capacitance across the base-emitter junction of Q5 is handled. Without 9 compensating for this, a large portion of the input signal will couple into the output during the hold phase. This is called feedthrough. During the hold phase, a very small amount of current is being drawn from the holding capacitor (on the order of a few nA). Even a small amount of feedthrough has a significant impact on the output. In my first few SHA designs I tried to come up with a filter which could selectively filter out the input signal at the hold capacitor node [Razavi]. This filter inevitably loaded down the node too much and caused problems with droop. In this topology an equal-and-opposite signal is injected into the node in order to counteract the feedthrough. This opposing signal is taken from the opposite side of the input buffer. Fig. 3.3 shows the placement of capacitors needed to achieve this. In order for the amplitude of the correction signal to be correct, the CFF capacitor should be equal to CBE of Q5. The paper [Vorenkamp] suggests using a series-parallel arrangement of the transistor to accomplish this. Better results were achieved using ideal capacitors. Figure 3.4 shows an example where the two signals sum to nearly zero. Figure 3.4: Feedthrough Example 3.3 Hold Capacitor 40pF was used as the holding capacitor size because it seemed to be a sweetspot between the droop and acquisition time. 10 Chapter 4 Results 4.1 Acquisition Time Figure 4.1: Acquisition Time for a 5V step is 87.5nS 4.2 Aperture Time 11 Figure 4.2: Zoomed out view of a signal hold Figure 4.3: Zoomed in showing an aperture time well within 5ns 12 4.3 Power Supply Rejection Ratio To calculate the PSRR the positive and negative rails were each increased by 0.5V with a constant DC input of 2v and the change in output was observed. P SRR = −1 ∗ 20 log( 4.4 2.00077 − 2.00069 ) = 81.93dB 1V Output Impedance Figure 4.4: Differential output impedance is less than 20Ω 13 (4.1) 4.5 Power Consumption Figure 4.5: Power consumption is less than 300mW 14 4.6 Slew Rate Figure 4.6: SHA with a 33MHz 1V signal on the output (31MHz is the maximum achievable with a 0.2V/ns slew rate) Figure 4.7: Slew rate = 2V/9ns 15 4.7 Feedthrough Attenuation Ratio attenuation ratio.png Figure 4.8: Feedthrough for a 5V pk-pk sine wave. Feedthrough attenuation = −20 log( 611µV 5V ) = 78.25dB. 4.8 Sample/Hold Current ratio Figure 4.9: Sample/hold current ratio = 3522. The capacitor current is well within 5mA. 16 4.9 Full Power Bandwidth Figure 4.10: The full power bandwidth is more than 100KHz. This is a 2.5V signal (maximum power) at 100KHz with no attenuation. 4.10 Accuracy Figure 4.11: Accuracy is within 0.1%(0.04%) 17 4.11 Hold Mode Settling Time The hold-mode settling time can be seen to be less than 50nA in Fig. 4.3. 4.12 Droop Rate Figure 4.12: While occasionally the droop is slightly larger than 10mV/ms at the beginning of the hold period, for the vast majority of the time the droop is within spec. 4.13 Step Hold Regretfully, step-hold is a spec I was not able to meet. My step-hold with a 1pF load is consistently 1mV (an order of magnitude too large). I choose to spend my time optimizing the other specifications because I consider the step-hold of lower importance than the others in a full ADC system. A large step-hold value will simply introduce a DC offset into the sampled signal. If I was very concerned, I could even add a dc-offset to the output so that the system is accurate during holds and inaccurate during tracking. 18 Chapter 5 Conclusion This project presented a comprehensive look at the material covered in ECE422. I sometimes use ADC’s at work, and it was helpful to see how such a critical component of an ADC operates. In particular, the benefits of using a fully differential system are very clear to me. In the future, I am interested in doing a similar design using CMOS technology to see how the two circuits compare. 19 Bibliography [Gray] Gray,Hurst,Lewis, and Meyer Analysis and Design of Analog Integrated Circuits, Fifth Edition [Jaeger] Jaeger and Blalock Microelectronic Circuit Design, Third Edition [Smith] Sedra and Smith Microelectronic Circuits, Fifth Edition [LTC] LTSpice Users Manual [Kester] Walt Kester Data Conversion Handbook, Analog Devices, Section 7.4: Sample-And-Hold Circuits [Moreland] Carl Moreland A 14-bit 100-Msample/s Subranging ADC, IEEE Journal of Solid-State Circuits, VOL. 35, NO. 12, December 2000 [Vorenkamp] Pieter Vorenkamp and Johan P. M. Verdaasdonk Fully Bipolar, 120-Msample/s 10-b Track-and-Hold Circuit, IEEE Journal of Solid-State Circuits, VOL. 27, NO. 7, July 1992 [Razavi] Behzad Razavi Design of a 100-MHz 10-mW 3-V Sample-and-Hold Amplifier in Digital Bipolar Technology, IEEE Journal of Solid-State Circuits, VOL. 30, NO. 7, July 1995 20 Appendix A Final Schematic Figure A.1: The primary circuit schematic. 21 Figure A.2: Schematic including parameters, supplies, and adjustment resistors. 22 Appendix B Device Plots Plots used to characterize the C-Pi library. B.1 Gummel Plots Figure B.1: Gummel plot for wn2 device showing a maximum gain with a collector current of approx. 200µA 23 Figure B.2: Gummel plot for wn8 device showing a maximum gain with a collector current of approx. 1mA Figure B.3: Gummel plot for wn32 device showing a maximum gain with a collector current of approx. 3mA 24 B.2 Early Voltage Figure B.4: Plot used to determine the early voltage of the wn2 device. Figure B.5: Plot used to determine the early voltage of the wn8 device. 25 Figure B.6: Plot used to determine the early voltage of the wn32 device. 26