* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download CSSP-81031 Final Version - Spectrum

Pulse-width modulation wikipedia , lookup

Electrical ballast wikipedia , lookup

Signal-flow graph wikipedia , lookup

History of electric power transmission wikipedia , lookup

Voltage optimisation wikipedia , lookup

Electrical substation wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Ground loop (electricity) wikipedia , lookup

Stray voltage wikipedia , lookup

Power MOSFET wikipedia , lookup

Mains electricity wikipedia , lookup

Regenerative circuit wikipedia , lookup

Surge protector wikipedia , lookup

Schmitt trigger wikipedia , lookup

Two-port network wikipedia , lookup

Power electronics wikipedia , lookup

Dynamic range compression wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Current source wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Alternating current wikipedia , lookup

Buck converter wikipedia , lookup

Wilson current mirror wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

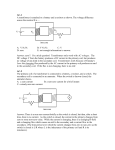

CSSP-81031 Final Version Title: Wide-Dynamic-Range and High-Sensitivity Current-to-Voltage Converters Author: Chunyan Wang Affiliation: Department of Electrical and Computer Engineering Concordia University, Montreal Canada Address: EV5.227, 1455 de Maisonneuve Blvd. West Montreal Quebec Canada H3G 1M8 Tel: 514 - 848 2424 ext. 3120 Fax: 514 - 848 2802 Email: [email protected] Key words: Analog VLSI, current-to-voltage conversion, adaptive circuits, current filter Wide-Dynamic-Range and High-Sensitivity Current-to-Voltage Converters Chunyan Wang A wide dynamic range and a high sensitivity are often incompatible with each other in analog circuits, such as signal converters or amplifiers. In this paper, we present a method of developing current-to-voltage converters featuring both. It comprises two current-to-voltage conversions. One is to convert the DC component, i.e. the average level of the current input, into a voltage with a nonlinear compression. The other is to apply a “linear” conversion to the signal component of the input current. This conversion is considered to be “linear” as the gain is made to be almost constant if the varying signal is rippling at a given current level, and to increase if the level is changed to be lower. Hence, the gain is adaptive to the input current, i.e. getting stronger if the current signal is weaker and vice versa. This adaptability is implemented by (a) an adaptive bias by means of the voltage converted from the DC component of the input current, and (b) the current-dependent finite drain-source resistances of MOS transistors. A low-pass current filter is used, in the proposed conversion operation, to separate the DC component of the input current from the signal one. We propose, in this paper, a basic structure of the filter and techniques to improve the filtering quality over a wide current range, also an approach to an effective reduction of the effect of the device mismatch as well. A design example of the proposed conversion is presented in this paper. The simulation results have shown its dynamic range of 5-decades and its sensitivity high enough to detect sub-nA current variations. Key words: Analog VLSI, dynamic range and sensitivity, current-to-voltage conversion, adaptive circuits, current filter, current compensation for device mismatch I. Introduction In many analog circuits, the dynamic range and sensitivity seem to conflict with each other. However, the need for both becomes more and more evident for analog processing circuits to get more applications. Current-to-voltage converters are often used in current-mode circuits and optical sensors. The variation of a current signal can be over a wide range as it is not directly limited by the supply voltage VDD. If a current-to-voltage converter is involved in a current-mode circuit, the dynamic range of the converter determines that of the circuit. In case of an optical sensor, the photocurrent is usually proportional to the flow of incident photons that can vary over a range of 5 decades or more. It is also often the case that the sensor can not operate over the entire range of the optical signal due to the limited dynamic range of the current-to-voltage converter employed in it. A converter of linear transconductance may provide a good conversion gain but usually not able to cover a wide range of signal variation. A converter of logarithmic current-to-voltage characteristic [1] [4] may have a wide coverage as the input current is logarithmically compressed, but the same compression results in a low sensitivity to the signal variation. Thus, it is challenging to design a circuit that features a wide dynamic range and a high sensitivity at any given level within the range. Making the circuit characteristics adaptive to the input current level is an effective approach to the combination of wide dynamic range and high sensitivity. A circuit can be made very sensitive to a weak signal at a given DC level by preset the operating point at this particular level. However, the sensitivity will be significantly lowered if the DC level of the input current is slightly shifted, i.e. the input range for this high sensitivity being very narrow. If the circuit is able to shift its operating point automatically according to the change of the input level, the circuit may still be able to respond very sensitively to the input variation even though it has gone out of its initial range. This shiftable “narrow range of high sensitivity” makes it possible for a circuit with a single input channel to be able to provide a high sensitivity to the signal variation over a wide range. Delbruck’s adaptive sensor may be the first currentto-voltage conversion circuit of this kind. It has a feedback loop for the bias set-up and the feedback factor is made “frequency-dependent” in order to have a low overall gain for the DC component and a higher one for signal variations [2 - 3]. The stability of the loop is secured by an appropriate set of the bias and the device parameters. Another adaptive sensor circuit has been reported in [5]. It makes good use of a current memory for the automatic tuning of the bias level and the dependency of the MOS drain-source resistance on the current level for the gain adaptive to the input. As the circuit involves an analog switch, making the switching noise low is a critical issue to secure a good operation. In this paper, a method of developing wide dynamic range and high sensitivity current-to-voltage converters is presented. It is based on the same principle of the shiftable “narrow range of high sensitivity” described above. This method is two-fold. The first is to separate the DC component of the input current from the signal one by a low-pass current filter. The DC current is used, after a compression, to set up the device bias. The second is to convert the input current signal component, not the DC one, into a voltage signal with an adaptive gain. A design example using this method and the simulation results are also presented. The basic scheme of the work in its early stage has been briefly reported in [6]. The present paper aims at providing the readers with a comprehensive grasp of the method and its fundamentals, and that of the practical designs with details. II. Description of the proposed method 2-1 Principle and the basic scheme The input current of a current-to-voltage converter can be expressed as iIN = IIN + iin, the sum of its DC component and signal variation. The response to the input is the output voltage vOUT = VOUT + vout. It is usually the case that (a) iin << IIN and (b) iin with a higher IIN is statistically greater than iin with a lower IIN. The components of the input current are to be converted differently so that each of them can be used for different purposes. The “main” conversion is that of the small signal component and a high gain is needed for a high sensitivity. The DC one of the input current is to be converted into a DC voltage for the circuit biasing to be adaptive to the input level, and a compression is evidently needed if the current varies over a wide range, e.g. from 1 nA to 100 µA, while the bias voltage should be confined within a window of less than 1 V. The separation of the DC component IIN from the signal component iin can be done by means of a low-pass current filter. This filter is used to extract IIN and a current copier is used to produce a copy of iIN. Then, as illustrated in Fig. 1, iin = iIN - IIN can be obtained at the node vOUT and converted to the voltage signal vout by using the output resistance at the node. The components of the output voltage should be produced in such way that VOUT = FCM (IIN) vout = rm(IIN) iin (EQ 1) where FCM (IIN) is a compression function of IIN and rm(IIN) is a resistive coefficient, both being dependent on IIN. The compression function FCM (IIN) needs to be nonlinear, e.g. logarithmic, so that a larger IIN is compressed with a strong compression rate, which results in VOUT that is able to vary with IIN without going beyond the boundaries of the voltage range. Both IIN and VOUT are then used to bias the devices connected to the output terminal where iin is converted into vout. Thus, the biasing point is made input-current-dependent, i.e. shiftable according to the input current level. Also, this shiftable biasing can also make rm(IIN) adaptive to the input current, if ro1 and ro2 are determined by the current. k1iIN iIN = IIN + iin ro1 vOUT ri k2IIN ro2 Fig. 1 Diagram illustrating the principle of the proposed method for the design of wide dynamic range current-to-voltage converters. Such a converter consists of three parts. The left part is the input stage, the upper-right one is a current copier, and the lower-right one a low-pass current filter that extracts IIN from iIN. If k1 = k2 = k, the voltage variation vout will be determined by r o1 ⋅ r o2 k ------------------- (i - I ) = rmiin. The conversion can be made linear if the resistances ro1 and ro2 are r o1 + r o2 IN IN voltage-independent. A low-pass filter can be built based on a current mirror, as shown in Fig. 2 [6], in which the time constant τ = C/gm1,with gm1 being the transconductance of N1, is greater than 1/fmin, where fmin is the lowest frequency component of the signal iin. This circuit can also provide a logarithmic compression of IIN at the node Vgn, if the current of N1 is weak enough to drive the device in the weak inversion region. If the transistors are matched, the drain voltage of N2, the NMOS in the right side, should be equal to Vgn. iIN = IIN + iin gm1 IIN Vgn IIN’ N1 C N2 Fig. 2 Current-mirror-based low-pass current filter. If the time constant τ = C/gm1 is large enough, the common gate voltage Vgn will be able to respond only to slow-changing component IIN, and thus only IIN is mirrored to the right side of the circuit. Using the current-mirror-based low-pass current filter, we propose a basic circuit structure, as shown in Fig. 3 [6], for a wide dynamic range and high sensitivity current-to-voltage conversion. In this circuit, two copies of the input current iIN are made by means of the PMOS transistors P1 and P2. From the first copy iP1, the DC component IN1 is obtained in the NMOS N1, and then IIN’ is generated in N2. The second copy iIN’ is combined with IIN’ at the node vOUT to extract the small current signal iin. The output voltage signal vout is converted from iin, by means of rdsP2 combined with rdsN2, the finite drainsource resistance of P2 and that of N2 [5]. The gain for the signal variation, rm(IIN) = vout/iin, is r dsP2 ⋅ r dsN 2 evaluated by ------------------------------. Please note that rdsP2 and rdsN2 are almost constant if P2 and N2 are in the r dsP2 + r dsN 2 saturation mode and their gate voltages are fixed, which makes a “linear” conversion from iin to vout. However, if the current level IIN’ changes, the voltages will be modified, making the resistances change. A lower IIN’ results in higher rdsP2 and rdsN2, which makes a strong rm(IIN) to a weaker input current. Thus, the conversion gain is adaptive to the signal. P0 Vgp P2 P1 iP1 iP0 vOUT = VOUT + vout Vgn iIN = IIN + iin IN1 N1 iIN’ C N2 IIN’ Fig. 3 Basic structure of the proposed current-to-voltage converter. The current filter shown in Fig. 2 is incorporated to make IIN’, a copy of the DC component of the input current iIN. The output r dsP2 ⋅ r dsN 2 voltage vOUT is modulated by vout = rm(IIN) iin, where rm(IIN) ≈ ------------------------------. Its DC r dsP2 + r dsN 2 component VOUT is expected to be approximately at the same level as Vgn. Consisting of only five transistors, the circuit shown in Fig. 3 can be expected to perform a low-pass current filtering, a logarithmic compression of the DC component and a current-to-voltage conversion with a variable gain. In the next sub-section, an analysis of its performance is presented and the design of a complete circuit for a wide dynamic range and high sensitivity conversion proposed. 2-2 Design example and analysis The basic scheme shown in Fig. 3 illustrates how the proposed method can be applied in CMOS circuit design. For a given dynamic range, one needs to take the following issues into consideration. • The condition for the low-pass filtering, τ = C/gm1 > 1/fmin. It should be noted that gm1is determined by the size of the transistor N1 and the current flowing in it. If the current gets very strong, 1/gm1 may become too small for the condition to be satisfied, making the upper limit of the current range. • The minimum current in each of the transistors. It determines the lower end of the current range. • The voltage limit for Vgp and Vgn. All the transistors in Fig. 3 need to operate in the saturation region, which may not be the case if (VDD - Vgp) or Vgn gets too large. • The speed concern of the circuit. The time constant τ needs to be large for a good low-pass filtering. However, if τ is too large, the circuit may not able to adjust its biasing point quickly to respond to a fast change of the input DC level, in particular, when the current is at the lower end of its range. The most critical issue is to make τ = C/gm1 > 1/fmin in the current filter, as it concerns the quality of the separation of the DC current from the signal current. One can look into the two elements, C and gm1, and their dependencies on the input current. The capacitance C could be voltage dependent, but as Vgs, the voltage across C, is not going to change in a large scale when the current changes, C is relatively stable and not sensitive to the current variation. The transconductance gm1, however, depends very much on IN1 that is, in its turn, dependent on iIN. The dependency of IN1 on iIN needs to be reduced in order that gm1 will be made less iIN-dependent. As IN1 is the DC component of iP1, if iP1 is made to vary in a smaller scale than iIN, the variation of IN1 will be down-scaled, making gm1 less sensitive to iIN. Let us define the scaling factor k = iP1/iIN, i.e. k = IN1/IIN if the low-pass filter functions correctly, and make k < 1 in a linear or nonlinear manner described as follows. 1. A linear down-scaling can be done by setting the size ratios of PMOS transistors P1 and P0 as (W/ L)P1 = k (W/L)P0 to make iP1 = k iIN. The dependency of gm1 on iIN is then down-scaled by a factor of k. A smaller value of k makes a stronger down-scaling and more extension of the upper end of the input current range. However, one should also take the lower end of the current range into consideration while selecting the value of k. If the minimum input current is, for instance, 0.1 nA and k = 0.1, the currents in the transistors P1, P2, N1 and N2 will be in the level of tens of pico-Amperes that may be too low to drive the MOS device properly and result in a poor signal-to-noise ratio. Also, the operation speed would suffer in this case. 2. A desirable down-scaling is nonlinear with k variable according to the level of the input current iIN. As gm1 increases with the current, the concern of the filtering condition τ = C/gm1 > 1/fmin arises when the input current iIN is in the upper part of its current range. If iIN is in the lower part of the range, the critical issue is to make the circuit sensitive enough to respond to the weak signal current iin, instead of τ > 1/fmin. Therefore, one would wish the down-scaling factor to be dependent on IIN and it should be effective only when iIN is above a certain level. A nonlinear down-scaling can be implemented by adding a current bypass branch controlled by the level of the input current. In the example shown in Fig. 4, the branch is in parallel with the PMOS transistor P0 to make iP0 = iIN - iBP, iBP denoting the bypass current. If iBP ≠ 0, only a portion of iIN will be mirrored to produce IN1 in the NMOS transistor N1. Thus, if the DC component of iIN increases, the change of IN1 is down-scaled. The bypass current iBP is controlled by Vgn in context of a negative feedback loop with the closed-loop gain smaller than unity. The down-scaling may not be effective if the loop is open, i.e. the NMOS transistor N3 is not conducting and iBP = 0 when iIN is weak. The linear and nonlinear scaling methods can be applied in the same circuit. In the circuit shown in 1 Fig. 4, the open-loop gain A is the linear scaling factor and the feedback gain ---------------1 + fA the nonlinear down-scaling one. A linear up-scaling, i.e. A > 1, can help to extend the lower end of the input current range, as it provides a current amplification when iIN is very weak while the feedback loop is open. If A the loop is closed because iIN gets stronger, the overall gain of ---------------1 + fA can be made to be smaller than unity for a nonlinear down-scaling in order to extend the upper end of the current range. iBP P3 P0 P1 Vgp P2 iP1 iP0 VN3 N3 iIN’ vOUT iIN + iIN Vgn IN1 N1 N2 IIN’ iP0 A iP1 iBP f C (a) (b) Fig. 4 Current-to-voltage converter with an input current bypass branch added to make iP0 = iIN - iBP in order to scale IN1 down in case that iIN is high. The current iP0 is mirrored to determine iP1, IN1 and Vgn. The same Vgn is then used, via a voltage shifter shown as a triangle symbol, to control iBP. This is a negative feedback loop and its block diagram is shown in (b). The closei A P1 loop gain -----= ----------------- < 1 , where A = iP1/iP0 is related to the ratio of (W/L)P1 to (W/L)P0, and i IN 1 + fA f is determined by the transconductances of N1, N3, and P3, and the input iIN as well. The loop may not be effective, i.e. iBP = 0 and iP0 = iIN, if iIN is too weak to make Vgn high enough to turn N3 on. Besides the dynamic range, the operation speed is another important issue. One wishes that the circuit should be able to adjust its biasing point quickly if the level of the input current changes. However, if the input current is very weak, this adjustment may be very slow, in particular when the capacitance at the common gate of N1 and N2 is large to have the time constant large enough for a decent low-pass filtering. One of the solutions to this kind of problem is to add a charging current when IIN’ is lower than the average of iIN’. It can be implemented by means of a transistor, such as the NMOS transistor N4 shown in Fig. 5. This transistor provides a “transient current” to accelerate the charging process at Vgn. When Vgn becomes high enough to make IIN’ equal to the average level of iP1, VOUT will be lowered to a level similar to that of Vgn and N4 will be turned off. Vgp P2 P1 iIN’ iP1 N4 IN1 N1 vOUT Vgn C IIN’ N2 Fig. 5 Additional charging current by the NMOS transistor N4 to accelerate the rise of Vgn. This current is effective when VOUT reaches a level high enough to turn N4 on. Such a high level VOUT occurs when IIN’ is smaller than the DC component of iIN’. The diagram shown in Fig. 6 is a current-to-voltage conversion circuit designed with the proposed method. It has a negative feedback loop for the nonlinear down-scaling. The difference between this loop and that in Fig. 4 is that its feedback signal iBP is able to vary more widely, by means of a masterslave structure, to match a wider range of the input iIN. Also, the circuit involves the additional charging current path, the same as that in Fig. 5, to accelerate the charging process at the node Vgn in case of weak iP1, to improve the operation speed and to maintain VOUT at approximately the same level as Vgn. This design shows that the proposed method can be easily implemented in a CMOS circuit with the measures for the signal range and processing speed incorporated. Its performance evaluation by electrical simulation is presented in the next section. iM iS P0 P3 P4 N3 iP0 P1 Vgp P5 Vbias P2 iP1 iBP iIN Input stage with down-scaling vOUT N4 VN3 Vgn IN1 P6 N1 iIN’ IIN’ C N2 Voltage shifter Low-Pass current filter & output stage Fig. 6 Complete circuit of a wide dynamic range and high sensitivity current-to-voltage converter. The bypass current iBP is given by iM + iS, the sum of the master and slave currents. The slave current iS is effectively added to iBP if the drain voltage of P3 is lowered enough to drive P4 on, which can happen when iM is reaching its full scale. Thus, the range of the feedback signal iBP is made larger to extend the upper limit of the dynamic range of iIN. The NMOS transistor N4 provides an extra charging current to accelerate Vgn rising when IIN‘ < iIN‘ is detected. III. Simulation results The circuit shown in Fig. 6 has been simulated using Hspice with the transistor models of a 0.18 µm CMOS technology. The supply voltage VDD is 1.8 V and the voltage Vbias is 0V. The input current iIN is a DC current IIN modulated by a sinusoidal signal iin. The range of IIN is from 4 nA to 411 µA. For a given IIN, the modulation depth h, i.e. the ratio of the amplitude of iin to IIN, is from 5% to 20% in the simulations. In the circuit shown in Fig. 6, the DC currents in the transistors P0, P1, and P2 are determined by IIN, the DC level of the input signal iIN, and the aspect ratio of the transistors that are listed in Table 1. The ratio of (W/L)P1 over (W/L)P0 is equal to 0.1, which gives a linear down-scaling, making IN1 and IIN’ be approximately one tenth of IIN. The capacitance C at the common gate of N1 and N2 is made large by placing a drain-source grounded NMOS of 400 µm2 in order to secure the low-pass filtering condition C/gm1 > 1/fmin when IIN reaches 411 µA. TABLE 1. Wm: minimum gate width Lm: minimum gate length P0 Wm/Lm P1 Wm/10Lm N1 Wm/1.2Lm P2 Wm/10Lm N2 Wm/1.2Lm P3 4.5Wm/Lm N3 3Wm/1.2Lm P4 9Wm/Lm N4 Wm/Lm P5 Wm/2.8Lm P6 Wm/Lm The simulation waveforms of the circuit shown in Fig. 6 are illustrated in Fig. 7. They demonstrate that the circuit is able to respond to the variation of the input current over the entire range. The DC level of the input signal iIN changes over the range of 5-decades, and the DC level of the output voltage vOUT is “confined” within a small voltage window of less than 350 mV, which permits the MOS transistors to operate within the region of the current-source mode where the drain-source resistance is high. The output voltage signal vout is measured under different conditions of iIN, and the results are shown in Fig. 8. It illustrates the shiftable “narrow range of high sensitivity” characteristics described in Section I. Using these results, the conversion gain, defined as the ratio of the amplitude of vout to that of iin, are presented in Table 2. It has been observed that, at a given level of IIN, iin is converted into vout with an almost constant gain. However, this gain depends on IIN in a nonlinear manner, because of the nonlinear characteristics of MOS transconductance and the nonlinear down-scaling. This dependency make the gain adapt to the input current, i.e. a higher gain for a lower level current. It has been measured that, at IIN = 4 nA, the conversion gain is about 80 mV/nA, which makes the circuit to be able to produce a detectable voltage signal when iin is in a sub-nA range. This gain is reduced about 47000 times, when IIN is about 105 times stronger to reach 411 µA, in order that the transistors still operate in the saturation region. It should be noted that, at this IIN level, the conversion gain is still much higher than that a logarithmic converter can provide, as the logarithmic compression is not applied to iin. Hence, a wide dynamic range and high sensitivity conversion have been made compatible with each other in this circuit. Fig. 7 Simulation waveforms of the circuit shown in Fig. 6. The waveforms are obtained when the frequency of the sinusoidal iin is 1 MHz and the ratio of the amplitude of iin to IIN is 10%. The first waveform, i.e. that on the top, is the input current iIN, displayed in a logarithmic scale. The second and third waveforms illustrate that Vgp responds to the current ripple of the input but Vgn follows only the change of the average current level, filtering out the signal variation. The DC component VOUT of the output voltage vOUT is ranged from 250 mV to 590 mV, corresponding to the range of IIN from 4 nA to 411 µA. The voltage signal vout. varies in the same way as the the input current signal iin, over the entire range of 5 decades. 400 IIN = 4 nA 10 nA 110 nA 1.11 uA 11.11 uA 111.11 uA 411.11 uA vout_p-p (mV) 300 200 100 0 −11 10 −10 10 −9 10 −8 10 −7 10 −6 10 −5 10 −4 10 −3 10 iin (A) Fig. 8 Characteristics of the peak-peak amplitude of the output voltage variation vout versus the amplitude of the sinusoidal current signal iin rippling over the DC component IIN. Please note that the x-axis is logarithmically scaled. Each curve is obtained with a given IIN and four different iin, i.e. the modulation depth h = 5%, 10%, 15% and 20%. If IIN is set at a higher level, the characteristic curve will be shifted rightwards and its slope will be reduced. The ratio of the amplitude of vout to that of iin for each set of (IIN, h) is calculated and presented in Table 2. The dashed line indicates a characteristic curve that a logarithmic current-to-voltage converter could have. TABLE 2. Conversion Gain of the Circuit Shown in Fig. 6 IIN 4 nA 10 nA 110 nA 1.11 µA Conv. Gain (mV/nA) IIN Conv. Gain (mV/µA) h = 0.05 81.25 h = 0.05 70.27 h = 0.10 80.88 h = 0.10 69.85 h = 0.15 77.58 h = 0.15 69.64 h = 0.20 81,00 h = 0.20 69.12 11.11 µA h = 0.05 41.69 h = 0.05 6.229 h = 0.10 53.40 h = 0.10 6.20 h = 0.15 54.80 h = 0.15 6.085 h = 0.20 50.75 h = 0.20 6.238 111.1 µA h = 0.05 8.27 h = 0.05 1.744 h = 0.10 7.409 h = 0.10 1.707 h = 0.15 7.694 h = 0.15 1.696 h = 0.20 7.64 h = 0.20 1.676 h = 0.05 .844 h = 0.10 .822 The conversion gain is the ratio of the amplitude of vout to that of iin. h = 0.15 .846 h = 0.20 .843 411.1 µA The modulation depth h is the ratio of the amplitude of iin to IIN. The above simulation results are obtained without considering the effect of device mismatch. The circuit illustrated in Fig. 6 involves two pairs of MOS transistors, namely (P1, P2) and (N1, N2), in its low-pass current filtering block. If N1 and N2 match, or mismatch, each other in the same way as P1 and P2, the DC component of the current in P2 and the current in N2 will be equal to cancel each other, resulting in VOUT = Vgn. Otherwise, the difference of the two currents will be iin’ + ∆ IIN’, instead of iin’, with ∆ IIN’ resulting from the device mismatch. This ∆ IIN’ is then converted into a DC component ∆VOUT = rm(IIN) ∆ IIN’, making VOUT = Vgn + ∆VOUT, instead of Vgn, which we call the DC mismatch. The deviation of VOUT from Vgn could make P2 or N2 out of the normal operation in the saturation region, in case of a strong vout, and thus causes a signal distortion. This DC mismatch, however, can be corrected by injecting a DC current into, or removing it from, the drain of N1 to compensate IN1 in such a way that IIN’, the mirrored copy of IN1, is equal to the DC component of the current in P2. Evidently, when the correction is done, i.e.VOUT being brought back to the level of Vgn, the compensated IN1 needs to be maintained. The transistor N4 shown in Fig. 5 is not able to provide a DC current for the compensation while VOUT ≈ Vgn. One can use the voltage difference (VOUT - Vgn) to generate a current compensating for the mismatch. Fig. 9 illustrates the low-pass current filter with such a compensation current provided by the two transistors N5 and N7 combined. Replacing the low-pass current filter in the current-to-voltage converter shown in Fig. 6 by that illustrated in Fig. 9, we make the converter have the DC mismatch compensation and it has then been simulated with Hspice. The simulation waveforms, illustrated in Fig. 10, demonstrated that this circuit is able to make the DC level of the output voltage uniformed at the level approximately equal to Vgn despite the device mismatch. The current compensation is, therefore, an effective solution to the problem of the DC mismatch. Low-Pass current filter & output stage Vgp P1 N7 IN7 P2 iIN’ iP1 vOUT C’ IN5 N5 Vgn IN1 N1 C N2 + - VO IIN’ N6 + - VgN5 VgN7 Fig. 9 Low-pass current filter with a DC current compensation for device mismatch. The average level of vOUT, denoted as VO, is compared with Vgn to produce two voltages VgN7 and VgN5 that are used to control the currents of N7 and N5, respectively. The current difference (IN7 - IN5) compensates for the device mismatch to make IIN’ equal to the DC component of iIN’. In this case, the transistor N4 shown in Fig. 6 is removed as N7 can provide the gate capacitance C with an additional current. The devices drawn in dashed lines are used to have a fast pull-down of VO, when IIN’ >> iIN’ due to sudden change of the input level IIN, by the “normally-off” NMOS transistor N6 in order to reduce IIN’ quickly. The voltage follower used in this circuit consists of 2 transistors, namely P5 and P6 shown in Fig. 6. Each of the voltage comparators is a singlestage differential amplifier consisting of five transistors. Fig. 10 Simulation waveforms of the three current-to-voltage converters of which the structures are identical and involve the same current compensation shown in Fig. 9, but device mismatch is different. The input signal is identical to that producing the waveforms shown in Fig. 7. The first waveform vOUT1 is the output voltage of the converter without device mismatch. The second one, vOUT2, is produced by the circuit in which gmN1, the transconductance of N1, is 36% smaller than gmN2, and vOUT3 by the one with gmN1 being 36% larger than gmN2. The three waveforms have the almost identical DC level VOUT by means of the compensation. It should be noted that the low-pass current filter involves the capacitance C made of a large drainsource grounded NMOS transistor in order to operate at an input current level of 411 µA. Such a large device makes the circuit too bulky to be placed in a pixel of an image sensor. However, in a CMOS image sensor, the current delivered by a tiny photodiode could hardly reach any micro-Ampere level and the input range is shifted toward a much lower end. If the proposed current-to-voltage converter is used in such a sensor, the capacitance can be made much smaller. Another issue to be noticed is the nonlinear nature of the conversion. This conversion is globally nonlinear and locally “linear”. The compression of the DC component, by means of the device nonlinearity, permits the wide input range. The “linear” high gain conversion, is based on the linearity of MOSFET drain-source resistances in the saturation mode when the DC component of the input current is fixed. However, like all the other cases of using nonlinear devices for “linear” operations, this linearity is limited. Moreover, the drain-source resistances of the transistors of the same design but placed in different places can not be exactly identical. If the circuit is used in a CMOS image sensor, the converters in different locations will have non-uniform outputs while the input is uniform. A compensation for this mismatch requires more research efforts. IV. Conclusion The work presented in this paper aims at solving the problem caused by the conflict of dynamic range and sensitivity in current-to-voltage conversion circuits. The proposed solution is to employ a low-pass current filter to separate the DC component from the signal one of the input current, to use the DC one, after a compression, for an input-dependent biasing, and to convert the signal one with an adaptive gain. This solution can be easily implemented in a CMOS circuit. A current mirror consisting of a transistor pair can be used as such a filter if its time constant is made to satisfy the low-pass filtering condition. This time constant is current-dependent. But the dependency can be reduced by applying the current down-scaling proposed in this paper. The compression function is based on nonlinear currentdependent characteristics of MOS transconductance. The voltage resulting from this compression is biasing the MOS transistors that determine the conversion gain applied to the signal component, which makes the gain adaptive to the input current. A design example of the proposed current-to-voltage conversion has been provided and its performance evaluated by the simulation with CMOS 0.18 µm models. The results have shown that the circuit is able to operate with an input current varying over a range of 5 decades. It is sensitive enough to respond to a current signal of a fraction of a nano-Ampere. A conversion gain is almost constant if the DC level of the input stays the same, and decrements if the level increments, which allows the circuit to detect the signal current when it is in the higher end of the 5-decade range without saturation. Besides the dynamic range and sensitivity, the converters designed with the proposed method feature low power dissipation. The biasing currents are the DC component of the input current and its copies, if the current in the voltage shifter in Fig. 6 can be ignored. It should also be mentioned that, unlike many current-mode circuits, these converters do not need clock and switches, and the conversion is performed on a continuous time basis. Thus the problems such as switching noise and preparation phases do not arise. Moreover, sparing from clocks makes the circuits to spare from many clock-related problems and facilitate their applications. Furthermore, to reduce the effect of device mismatch, a DC current compensation method has been presented in this paper and its effectiveness verified by the simulation results. References [1] S. G. Chamberlain and J. P. Y. Lee, A novel dynamic range silicon photodetector and linear Imaging array, IEEE J. Solid-State Circuits, vol.Sc-19, no.1, p. 41-48, 1984. [2] T. Delbrük and C. Mead. Phototransduction by Continuous-Time, Adaptive Logarithmic Photoreceptor Circuits. Tech. Rep., California Institute of Technology, Computation and Neural Systems Program, CNS Memorandum 30, Pasadena, CA 91125, 1994. [3] T. Delbrück and D. Oberhoff, Self-biasing low power adaptive photoreceptor, In: Proc. IEEE International Symposium on Circuits and Systems, pp. IV844-847, May 2004. [4] A. Hamasaki, M. Terauchi, and K. Horii, A wide-dynamic-range photodiode-type active pixel sensor cell with seamlessly combined logarithmic-linear-logarithmic response, Japanese journal of Applied Physics, vol. 46, no. 7A, p. 4050, 2007. [5] C. Wang and F. Devos, An Adaptive optical sensor, In: Proc. IEEE International Symposium on Circuits and Systems, pp. IV333-336, Geneva, Switzerland, May 2000. [6] C. Wang, Wide dynamic range current-to-voltage converters, In: Proc. 3rd International Design and Test Workshop, pp. 354 - 357, Monastir, Tunisia, Dec. 2008.