* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Effects of Bonding and Packaging on Circuit Operation Speed

Resistive opto-isolator wikipedia , lookup

Current source wikipedia , lookup

Printed circuit board wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Buck converter wikipedia , lookup

Power electronics wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Flexible electronics wikipedia , lookup

Power MOSFET wikipedia , lookup

Surface-mount technology wikipedia , lookup

Opto-isolator wikipedia , lookup

Electrical wiring in the United Kingdom wikipedia , lookup

Regenerative circuit wikipedia , lookup

Power inverter wikipedia , lookup

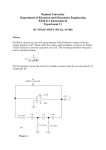

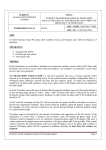

Effects of Bonding and Packaging on Circuit Operation Speed In the current technology, the prevalent method to provide connection of an integrated circuit built on a silicon die is to use an electrical connection path consisting of on-chip bonding pads, a bondwire, package internal connections, package pins, and printed circuit board (PCB) traces. All of these components possess some capacitance and inductance and act as a frequency-dependent load for the last stage of the circuit. To investigate this loading effect quantitatively, we built two on-chip ring oscillators using 0.6 micron technology (the AMI-C5N process) through the MOSIS fabrication service. The first ring oscillator was an external ring oscillator in which the communication through the stages, which were minimum-size inverters, were provided through the bonding pad-bonding wire-pin-PCB-pin-wire-pad path described above. The following picture shows the layout of two stages of this oscillator. Left: “External” ring oscillator, 11 stages (two stages are shown). Connection between stages require going out to the board through bonding pads, wires and pins. The second oscillator was an internal ring oscillator in which the inverter stages were directly connected to each other on-chip. The layout is given below. We tested the performance of these circuits on a breadboard. The results are summarized in the table below. Internal Osc. External Osc. 112 MHz (31-stage) (equivalent to 1.16 GHz for 3 stages) 398 KHz (11-stage) (equivalent to 1.46 MHz for 3 stages) There is almost an 800-fold drop in speed from the internal oscillator, where each inverter is loaded only by another inverter, to the external oscillator, where each inverter is loaded by the whole intra-chip communication path. Considering these inverters as the output stages of circuits trying to communicate with another circuit, the performance hit such a system takes in the presence of intra-chip communication paths is clear. Current layout philosophy provides for this need by adding specially-designed buffer circuits between the last stage of the logic circuit and the on-chip bonding pads. However, these buffers, comprised of inverters whose size increases geometrically, take up valuable chip real estate. We expect the performance loss will be more substantial as chip feature sizes decrease with progressing technology. The factors, which affect operation speed, that decrease as the minimum feature size decreases are as follows: Supply voltage, minimum transistor size, gate oxide thickness and channel mobility. For a back-of-the-envelope calculation of the driving speed capability of a circuit, the changes in these factors interact to cause increasing output resistance but decreasing input capacitance for CMOS logic gates. For instance, the theoretical high-to-low transition delay time ratios of a 0.6 micron technology to that of a 1.8 micron technology is almost 2.5. This delay time calculation depends on the input capacitance of the load being driven by the gate. It should be noted that the intra-chip communication path capacitance does not scale very much with decreasing feature size. Thus the output-stage load of both the 0.6 micron and 0.18 micron technologies will be comparable. But if anything, the 0.18 micron technology will take a harder hit in speed performance, both because it is capable of driving less current on the same load, and because it would have been intrinsically faster if it did not have to drive off-chip structures but just the input stage of another gate in the same technology.