* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download unit 5 class1 (1)

Negative resistance wikipedia , lookup

Regenerative circuit wikipedia , lookup

Integrated circuit wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Thermal runaway wikipedia , lookup

Radio transmitter design wikipedia , lookup

Schmitt trigger wikipedia , lookup

Galvanometer wikipedia , lookup

Surge protector wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Power electronics wikipedia , lookup

Two-port network wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Power MOSFET wikipedia , lookup

Current source wikipedia , lookup

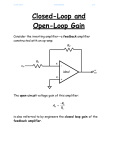

Operational amplifier wikipedia , lookup

Wilson current mirror wikipedia , lookup

Opto-isolator wikipedia , lookup

UNIT -V IC MOSFET Amplifiers Outline • • • • • • IC Amplifiers IC Biasing –current steering circuit MOSFET current sources Amplifiers with active load CMOS common source and source follower CMOS Differential amplifier Introduction • Integrated-circuit fabrication technology imposes constraints – large capacitors are not available – very small capacitors are easy to fabricate • One objective is to realize as many functions as possible using MOS transistors only. • Reduction of device size is of great concern. Why current source needed for IC biasing? • Resistors take too much space on the chip. Source degeneration with resistor is not implemented in ICs. • The goal of a good bias is to ensure drain current (ID) and Drain source voltageVDS would not change (e.g., due to temperature variation). One can force ID to be constant using a current source. IC Biasing Biasing in IC design is based on the use of constantcurrent sources. A constant dc current (called a reference I) is generated at one location and is then replicated at various other locations for biasing the various stages through a process known as current steering. Biasing Mechanism for ICs • MOSFET Circuits The basic MOSFET current source MOS current-steering circuits The bias currents of the various stages track each other in case of changes in power-supply voltage or in temperature Current source • Two types of basic gain cells exist: – Common-source (CS) – Common-emitter (CE) • Both are loaded with constant-current source. – This is done because of difficulties associated with fabrication of exact resistances. – It also facilitates increased gain. • These circuits are referred to as current-source loaded / active loaded. current source - contd… • NMOS current source sinks current to ground • PMOS current source sources current from positive supply Basic current mirror • Simple current-source loads reduce the gain realized in the basic gain cell because of their finite resistance (usually comparable to the value of ro of the amplifying transistor). nMOSFET current source Two matching MOSFET transistors connected backto-back, such that both have the same Gate-to-Source voltage Io I REF (W L ) 2 (W L )1 nMOSFET current source - contd… • Need: Using the transistors geometries (W/L)1and (W/L)2as design parameters create a DC current Io, as long as transistor Q2 is in Saturation Mode PMOS Current source PMOS CURRENT SOURCE - contd… Basic current mirror - contd… Vo VGS (W L) 2 Io I REF (1 ) (W L)1 VA2 14 Basic current mirror - contd… • Assume Q2 to be operating in saturation mode • To ensure that Q2 is saturated, the circuit to which the drain of Q2 is to be connected must establish a drain voltage Vo that satisfies the relationship Basic current mirror - contd… • Identical devices Q1 and Q2. The drain current of Q2, IO, will equal the current in Q1, IREF, at the value of V0 that causes the two devices to have the same VDS, that is, at V0 = VGS. • As V0 is increased above this value, I0 will increase according to the incremental output resistance ro2 of Q2. Basic current mirror - contd… VA is proportional to the transistor channel length; thus, to obtain high output-resistance values, current sources are usually designed using transistors with relatively long channels. Output characteristics VA 2 Ro ro 2 Io Current mirror circuits - contd… Two performance parameters need to be improved: • The accuracy of the current transfer ratio of the mirror. • The output resistance of the current source. MOS Cascode current source Q1 is CS configuration and Q2 is CG configuration. Current source biasing. 20 MOS Cascode current source - contd… Small signal of cascode current mirror Performance of MOS Cascode • Open-circuit voltage gain Avo ( g m ro ) 2 The cascoding increases the magnitude of the open-circuit voltage gain from Ao to Ao2 • Output resistance Rout A0 ro1 23 Performance of MOS Cascode • If ro2 is infinite, then Rin2 reduces to 1/gm2. • If ro2 cannot be neglected, as is always the case in IC amplifiers, the input resistance depends on the value of RL in an interesting fashion. – The load resistance (RL) is divided by the factor (gm2ro2). Cascode MOS current mirror Ro ro3 1 ( g m3 g mb3 )ro3 ro 2 g m3ro3ro 2 MOS cascode current mirror requires large load to increase the gain Cascode MOS current mirror - contd… • Q1 and Q3 are always in saturation. • Q2 and Q4 both have to be in saturation for current mirror to work. • Condition for saturation – VDS2 > VGS – Vt – VDS4 > VGS – Vt PMOS CASCODE CURRENT MIRROR Working of PMOS cascode is same as NMOS cascode. Cascoding • To raise the output resistance of the CS or CE transistor, we stack a CG or CB transistor on top. This is cascoding. • The CG or CB transistor in the cascode passes the current gm1vi provided by the CS or CE transistor. Cascoding-contd… • A MOS cascode amplifier operating with an ideal current source load achieves a gain of (gmro)2 = A02. • To realize the full advantage of cascoding, the load current-source must also be cascoded, in which case a gain as high as 1/2A02 can be obtained. Cascode amplifier with cascode current mirror Cascode amplifier with cascode current mirror - contd… • Advantage – Much better high-frequency response (high gainbandwidth). – Simpler biasing. Double Cascoding • If still a higher output resistance and correspondingly higher gain are required, it is still possible to add another level of cascoding • Observe that Q3 is the second cascode transistor, and it raises the output resistance by (gm3ro3). Double Cascoding - contd… The Folded Cascode To avoid the problem of stacking a large number of transistors across a low-voltage power supply, one may use a PMOS transistor . Folded Cascode-contd… • Double cascoding is possible in the MOS case only. However, the large number of transistors in the stack between the power-supply rails results in the disadvantages of a severely limited output-signal swing. The foldedcascode configuration helps to resolve this issue. WILSON CURRENT Mirror • A Wilson current mirror is a three-terminal circuit. • It accepts an input current at the input terminal and provides a "mirrored" current source or sink output at the output terminal. • The mirrored current is a precise copy of the input current. • It may be used as a Wilson current source by applying a constant bias current to the input branch . • The circuit is named after George R. Wilson, an integrated circuit design engineer . MOS Wilson Current Source Ro g m3ro3ro 2 The drain current of Q2 to equal the input current and the output configuration assures that the output current equals the drain current of Q1. 37 MOS Wilson Current Source - contd… • An improved current source which has higher output resistance than the simple current mirror. • The output current is related to the reference current by the equation (assuming the transistors operating in saturation region): IO W2 / L2 I1 W1 / L1 MOS Wilson Current Source - contd… • The reference current I1 may be approximated by VDD 2Vto I1 R Small signal-MOS Wilson Current source •The transistor pairs M1-M2 and M3-M4 are exactly matched and the input and output potentials are approximately equal, then in principle there is no static error. •The input and output currents are equal because there is no low frequency or DC current into the gate of a MOSFET. MOS Wilson Current Source • The threshold voltage of MOS devices is usually between 0.4 and 1.0 volts with no body effect depending on the manufacturing technology. • vgs must exceed the threshold voltage by a few tenths of a volt to have satisfactory input-output current match, the total input to ground potential is comparable to 2.0 volts. • This difference is increased when the transistors share a common body terminal and the body effect in M4 raises its threshold voltage. Limitation of Wilson current mirror • The principal limitation on the use of the Wilson current mirror in MOS circuits is the high minimum voltages between the ground connection. • The input and output nodes that are required for proper operation of all transistors in saturation. • The voltage difference between the input node and ground is vgs1+vgs4 . MOS Widlar current source Summary • Biasing in integrated circuits utilizes current sources. As well, current sources are used as load devices. • The MOS current mirror has a current transfer ratio of (W/L)2/(W/L)1. For a bipolar mirror, the ratio is IS2/IS1. Mos steering circuits I 2 I REF (W L) 2 (W L)1 I 3 I REF (W L)3 (W L)1 I5 I 4 (W L)5 (W L) 4 45 MOS steering circuits - contd… • Once a constant current is generated, it can be replicated to provide DC bias currents for the various amplifier stages in the IC. • Current mirrors can obviously be used to implement this current – steering function • The use of a negative DC supply –VSSdoes not change the fact that, by-structure, both transistors, in every mirror pair, have the same VGS voltage. Mos steering circuits - contd… • Here Q1 together with R determine the reference current IREF. Transistors Q1, Q2, and Q3 form a twooutput current mirror, Mos steering circuits - contd… • To ensure operation in the saturation region, the voltages at the drains of Q2 and Q3 are • constrained as follows: • VD2,VD3≥ -VSS +VGS1-Vtn • VD2,VD3≥ -VSS +Vov1 Summary • Accurate and stable reference current is generated and then replicated to provide bias current for the various amplifier stages on the chip. • The heart of the current-steering circuitry utilized to perform this function is the current mirror. CS Amplifier with active load a. Current source acts as an active load. b. Source lead is signal grounded. c. Active load replaces the passive load. CS Amplifier with active load - contd… Small-signal analysis of the amplifier performed both directly on the circuit diagram and using the smallsignal model explicitly. The intrinsic gain Avo g m ro CS Amplifier with active load - contd… RL Av Avo RL Ro ro 2 ( g m1ro1 ) ro 2 ro1 g m1 (ro1 // ro 2 ) ro 2 VA2 I REF CG AMPLIFIER AND CD AMPLIFIER CS Amplifier with source degeneration A CS amplifier with a sourcedegeneration resistance Rs CS Amplifier with source degeneration • A source-degeneration resistance is called so because of its action is reducing the effective transconductance of the CS stage to gm/(1+gmRs). • The output resistance expression of the cascode can be used to find the output resistance of a sourcedegenerated common-source amplifier. • A useful interpretation of the result is that Rs increases the output resistance by the factor (1 + gmRs). CS Amplifier with source degeneration contd… Circuit for small-signal analysis. Circuit with the output open to determine Avo. 56 CS Amplifier with source degeneration contd… • Input resistance • Output resistance Rin Rout ro [1 ( g m g mb ) Rs ] • Intrinsic voltage gain Avo g m ro The resistance Rs has no effect on Avo • Short-circuit transconductance gm Gm 1 ( g m g mb ) Rs 57 Summary • A CS amplifier with a resistance Rs in its source lead has an output resistance Ro = (1+gmRS)ro. The corresponding formula for the BJT case is Ro = [1+gm(Re||rp)]ro. NMOS amplifier with enhancement load device Driver transistor characteristics and enhancement load curve with transition point NMOS amplifier with enhancement load device • Dissipation is high since current flows when Vin = 1. • Vout can never reach Vdd (effect of channel). • Vgg can be derived from a switching source (i.e. one phase of a clock, so that dissipation can be significantly reduced . • If Vgg is higher than Vdd, an extra supply rail is required. Voltage transfer characteristics of NMOS amplifier with enhancement load device NMOS with Depletion load NMOS with Depletion load - contd… • Pull-Up is always on – Vgs = 0; depletion • Pull-Down turns on when Vin > Vt • With no current drawn from outputs, Ids for both transistors is equal NMOS with Depletion load - contd… • Dissipation is high since rail to rail current flows when Vin = Logical 1 • Switching of Output from 1 to 0 begins when Vin exceeds Vt of pull down device • When switching the output from 1 to 0, the pull up device is non-saturated initially and this presents a lower resistance through which to charge capacitors (Vds < Vgs – Vt) Voltage Transfer Characteristics NMOS Inverter ID VGS = 3 V X Linear ID vs VDS given by surrounding circuit X VGS = 1 V VDS CMOS Inverter CMOS Inverter VOUT vs. VIN VOUT both sat. VDD curve very steep here; only in “C” for small interval of VIN NMOS: cutoff PMOS: triode NMOS: saturation NMOS: triode NMOS: triode PMOS: saturation PMOS: cutoff PMOS: triode A B C D E VIN VDD CMOS Inverter ID ID A B C D E VIN VDD Important Points • No ID current flow in Regions A and E if nothing attached to output; current flows only during logic transition • If another inverter (or other CMOS logic) attached to output, transistor gate terminals of attached stage do not permit current: current still flows only during logic transition VDD VDD S D VIN S VOUT1 D D D S S VOUT2 CMOS Inverter Transfer characteristics • Drain current of NMOS In n 2 Vin Vtn Drain current of PMOS p 2 I p Vin VDD Vtp 2 2 CMOS Inverter Transfer characteristics At logic threshold, In = Ip n 2 n 2 Vin Vtn Vin 2 Vtn p 2 Vin VDD Vtp 2 p 2 Vin VDD Vtp n Vin Vtn Vin VDD Vtp p Vin 1 n p n Vtn VDD Vtp p CMOS Inverter Transfer characteristics VDD Vtp Vtn Vin 1 n p • If n = p and Vtp = –Vtn • V Vin DD 2 n p Common source Amplifier PMOS active load I-V Characteristics CMOS common source Amplifier Driver Transfer Voltage Transfer Pseudo NMOS Inverter Pseudo NMOS Inverter The CMOS common-source amplifier FIG :Common gate CMOS I-V characteristics Transfer characteristics CMOS Common source Amplifier small signal model CMOS Differential Amplifier • A simple version of a CMOS differential amplifier is shown at the left – The load devices Q3 and Q4 are built with PMOS transistors – Q3 and Q4 operate as a form of current mirror, in that the small signal current in Q4 will be identical to the current in Q3 – Q3 has an effective impedance looking into its drain of – 1/gm || ro3 since its current will be a function of the voltage on node vd1 CMOS Differential Amplifier - contd… • Q4 has an effective impedance looking into its drain of ro4 only, since its current will be constant and not a function of vout • The gain of the right hand (inverting) leg will be higher than the gain of the left side • Since all transistors have grounded source operation, there is no body effect to worry about with this CMOS diff amp circuit CMOS Diff Amp Equivalent Circuit Model CMOS Diff Amp with Current Mirror Sources CMOS Diff Amp with Current Mirror Sources CMOS Diff Amp with Current Mirror Sources CMOS Diff Amp with Current Mirror Sources - contd… • The advantage of this configuration is that the differential output signal is converted to a single ended output signal with no extra components required. In this circuit, the output voltage or current is taken from the drains of M2 and M4. CMOS Diff Amp with Current Mirror Sources - contd… • The operation of this circuit is as follows. If a differential voltage, VID=VG1-VG2, is applied between the gates, then half is applied to the gatesource of M1 and half to the gate-source of M2. The result is to increase ID1 and decrease ID2 by equal increment, ∆I. CMOS Diff Amp with Current Mirror Sources - contd… • The ∆I increase ID1 is mirrored through M3-M4 as an increase in ID4 of ∆I. • As a consequence of the ∆I increase in ID4 and the ∆I decrease in ID2 , the output must sink a current of 2∆I. • The sum of the changes in ID1 and ID2 at the common node VC is zero. Differential mode Equivalent Circuit Differential gain is given by Differential Amplifier • The differential amplifier topology shown at the left contains two inputs, two active devices, and two loads, along with a dc current source • We will define the – differential mode of the input vi,dm = v1 – v2 – common mode of the input as vi,cm= ½ (v1+v2) • Using these definitions, the inputs v1 and v2 can be written as linear combinations of the differential and common modes – v1 = vi,cm + ½ vi,dm – v2 = vi,cm – ½ vi,dm Differential Amplifier - contd… • These definitions can also be applied to the output voltages – Differential mode vo,dm = vo1 – vo2 – Common mode vo,cm = ½ (vo1 + vo2) • Alternately, these can be written as – vo1 = vo,cm + ½ vo,dm – vo2 = vo,cm – ½ vo,dm Summary-contd.. • Integrated-circuit fabrication technology offers the circuit designer many exciting opportunities, the most important of which is the large number of inexpensive small-area MOS transistors. • An overriding concern for IC designers, however, is the minimization of chip area or “silicon real estate.” As a result, large-valued resistors and capacitors are virtually absent. Summary-contd.. • The basic gain cell of IC amplifier is the CS (CE) amplifier with a current-source load. • For an ideal current-source load (i.e. one with infinite output resistance), the transistor operates in an opencircuit fashion and thus provides the maximum gain possible: • Avo = -gmro = -A0. Summary-contd.. • The intrinsic gain A0 is given by A0 = VA / VT for a BJT and A0 = VA/(VOV/2) for a MOSFET. For a BJT, A0 is constant independent of bias current and device dimensions. • For a MOSFET, A0 is inversely proportional to ID1/2.