* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Current Sources and Sinks - UTK-EECS

Electrical substation wikipedia , lookup

History of electric power transmission wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Stepper motor wikipedia , lookup

Electrical ballast wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Thermal runaway wikipedia , lookup

Power inverter wikipedia , lookup

Voltage optimisation wikipedia , lookup

Mains electricity wikipedia , lookup

Stray voltage wikipedia , lookup

Surge protector wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage regulator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power electronics wikipedia , lookup

Two-port network wikipedia , lookup

Alternating current wikipedia , lookup

Buck converter wikipedia , lookup

Current source wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Wilson current mirror wikipedia , lookup

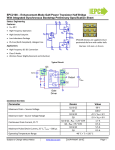

EE 532 − Analog IC Design II Spring 2002 Page 43 Current Sources and Sinks The Current Mirror An ideal current source/sink has infinite output impedance and, subsequently, provides constant current over a wide operating voltage range. The reality, however, is finite output impedance and limited output voltage swing. Also, for current mirrors, minimum input voltage requirements. If M1 and M2 are perfectly matched, then the simple current mirror provides I I D2 β W L = o = 2 = 2 1 I D1 I in β1 W1 L2 (since VGS1=VGS2) if channel length modulation and mobility modulation are neglected, and SI saturation operating is assumed. In addition, if VSS = 0V, then Vout ,min = VGS 2 − VTHN = (VDS ,sat )M2 , Vin ,min = VGS 1 > VTHN , and ro = 1 λI o Normally the values for VGS and L are selected and then W is used as a current scaling factor. Typically VGS is chosen to provide VDS,sat of several hundred millivolts. Often times the chosen L value is 2 to 5 times greater than the minimum Ldra to help minimize the channel length modulation and mobility modulation effects. Spring 2002 EE 532 − Analog IC Design II Page 44 From the figure below, note the output voltage value at which ID1 = ID2 and the effect of finite output resistance. Example 20.2 illustrates how multiple ratioed currents are mirrored. In this example oxide encroachment has been neglected! Layout techniques that compensate for this will be discussed soon. Example of how the basic current mirror can be utilized in biasing schemes: Spring 2002 EE 532 − Analog IC Design II Page 45 Obviously n-channel transistors are used to implement current sinks whereas p-channel transistors are used to implement current sources. The Cascode Current Mirror The cascode configuration is used to increase the output resistance of the current sink/source. Note that the cascode current sink requires more output voltage overhead, i.e., larger Vout,min (say to stay in SI saturation) than the simple (basic) current sink. Spring 2002 EE 532 − Analog IC Design II Page 46 An alternate cascode sink that provides Vout,min = 2∆V is shown below. Note the relationship between the transistors’ aspect ratios. The output resistance of the cascode configuration (Fig. 20.5) can be determined from the small-signal model. Ro = ro 4 (1 + g m 4 ro 2 ) + ro 2 ≈ g m 4 ro2 [ro = ro2 = ro4, SI sat.] Spring 2002 EE 532 − Analog IC Design II Page 47 For the general case (replacing ro2 with an arbitary R): Ro = ro (1 + g m R ) + R ≈ ro (1 + g m R ) This general description of output resistance, Ro = ro (1 + g m R ) + R , can used to quickly estimate the output resistance of other cascode circuits such as the triple cascode (Fig. 20.9 and equation 20.13). Sensitivity of the Basic Current Sink/Source By definition, the sensitivity of the basic current sink’s output current to VDD is given as ∆I o Io VDD ∂I o Io = ⋅ = lim SVDD ∆ VDD I ∂VDD ∆VDD→0 o VDD In this same manner, Io’s sensitivity to other inputs or component values can be (individually) obtained. If ID1 = ID2 (= Io) and VGS changes very little with variations in VDD, then I o SVDD ≈ VDD 1 ⋅ Io R The percentage change in Io is described by ∆I o ∆VDD Io = SVDD ⋅ Io VDD EE 532 − Analog IC Design II Spring 2002 Page 48 For computer simulations of circuit sensitivity (a necessity for large circuits), the excerpt shown below from the HSpice manual regarding sensitivity analysis might be helpful. .SENS Statement − DC Sensitivity General form .SENS ov1 <ov2 ...> ov1 ov2 ... Branch currents or nodal voltage for DC component sensitivity analysis. Example .SENS V(9) V(4,3) V(17) I(VCC) If a .SENS statement is included in the input file, HSPICE determines the DC small-signal sensitivities of each specified output variable relative to every circuit parameter. The sensitivity measurement is the partial derivative of each output variable with respect to the value of a given circuit element, taken at the operating point, and normalized to the total change in output magnitude. (Therefore, the sum of the sensitivities of all elements is 100%). Sensitivities for resistors, voltage sources, current sources, diodes, and BJT’s are calculated. Only one .SENS analysis may be performed per simulation. If more than one .SENS statement is present, only the last will apply. Note: The .SENS statement can generate large amounts of output for large circuits. Temperature Analysis of the Basic Current Sink/Source The simple current mirror/sink’s temperature coefficient is described by TC (I o ) = where Io = 1 ∂I o 1 I o ⋅ = ⋅S I o ∂T T T W2 L1 VDD − VGS − VSS ⋅ W1L2 R Substituting, we obtain TC (I o ) = − Recognize that 1 W2 L1 1 ∂VGS I o ∂R ⋅ ⋅ + ⋅ I o W1 L2 R ∂T R ∂T 1 ∂R ⋅ is the resistor’s temperature coefficient. R ∂T EE 532 − Analog IC Design II Spring 2002 To determine Page 49 ∂VGS , the (temperature dependent) expression for VGS must be ∂T considered: VGS = VTHN + Io β2 2 = VTHN + W2 L1 (VDD − VGS − VSS ) ⋅ W W1 L2 R ⋅ KP (T ) ⋅ 2 2 L2 If VDD − VSS >> VGS, then (after some calculus) ∂VGS ∂VTHN 2 L1 (VDD − VSS ) 1 1 ∂KP(T ) 1 ∂R + = + ⋅ ⋅− ⋅ ∂T ∂T W1 R ⋅ KP(T ) 2 KP(T ) ∂T R ∂T Using ∂VTHN 1 ∂KP(T ) − 1.5 = VTHN ⋅ TCVTHN ≈ −2.4mV/°C and = ⋅ , KP (T ) ∂T T ∂T TC(Io) becomes TC (I o ) = − 1 W2 L2 VTHN ⋅ TCVTHN 1 L1 VDD − VSS 1 ∂R 1.5 1 ∂R ⋅ − − − I o W1 L1 R R W1 2 ⋅ R ⋅ KP(T ) R ∂T T R ∂T This expression is used in Example 20.6. Note that the calculated value of TC(Io) changes with temperature. Also note that the TC(Io) expression can be set equal to zero to determine the value of Io and R needed for the basic current sink to have a temperature coefficient of zero (see equ. 20.27). EE 532 − Analog IC Design II Spring 2002 Page 50 Transient Response of the Simple Current Mirror The transient behavior of the simple current mirror is a critical measure of it’s performance. Consider the scenario shown below where a voltage step is applied at the output. How is Io affected? VGS? For a fast-edge voltage step applied at the output, ∆VGS = Vstep, peak ⋅ C gd 2 C gs1 + C gs 2 + C gd 2 and the change in output current is ∆I o = β2 2 (∆VGS β β 2 + VGS − VTHN )2 − 2 (VGS − VTHN )2 = 2 ∆VGS + g m 2 ∆VGS 2 2 The VGS exhibits a time constant (τ) behavior while returning to its DC value. R determines the resistive component of this time constant after a negative-going pulse has been applied at the output. Hence, the charging time constant is given by τ = R ⋅ (C gs1 + C gs 2 + C gd 2 ) Following a positive-going pulse, 1/gm1 is the effective resistance for the discharge time constant. Therefore the discharge time constant is given by τ= ( 1 ⋅ C gs1 + C gs 2 + C gd 2 gm ) The output current decays back to its DC value at an estimated rate of τo≈2τ. Example 20.7 helps illustrate the severity of transient response. EE 532 − Analog IC Design II Spring 2002 Page 51 Layout of the Simple Current Mirror In above figure (Fig. 20.13), L − DL L1 = 1drawn = 1 , but in the top figure (Fig. L2 L2drawn − DL 20.13(a)), W2 W2drawn − DW = W1 W1drawn − DW does not equal an integer. The bottom figure (Fig. 20.13(b)), however, provides W − DW W2 = X ⋅ 1drawn W1 W1drawn − DW where X is an integer. The netlist for Fig. 20.13(b) could have this form: M1 M2 1100 2100 CMOSNB CMOSNB L=5u W=5u L=5u W=5u M=4 Spring 2002 EE 532 − Analog IC Design II Page 52 Matching Errors in MOSFET Current Mirrors Good layout design is essential for circuits needing matched devices. Layout techniques are effectively used to minimize first-order mismatch errors due to variations in these process parameters: gate-oxide thickness, lateral diffusion, oxide encroachment, and oxide charge density. Considering only the effects of threshold voltage mismatch within the simple current mirror, its current ratio is described by 2 ∆VTHN 1 − Io β (VGS − VTHN − 0.5∆VTHN )2 2(VGS − VTHN ) = = 2 I D1 β (VGS − VTHN + 0.5∆VTHN )2 ∆VTHN 1 + 2(VGS − VTHN ) Io 2∆VTHN ≈ 1− (VGS − VTHN ) I D1 for SI saturation operation if a symmetric distribution in threshold voltage across the circuit is assumed (i.e., VTHN1 = VTHN − 0.5∆VTHN and VTHN2 = VTHN + 0.5∆VTHN). Note the dependence on VGS. A reduction in VGS increases the input/output error in current mirrors induced by threshold voltage mismatch. Considering only transconductance parameter mismatch, Io ∆KPn ≈ 1+ I D1 KPn where the value of KPn is the average transconductance parameter between the two transistors within the simple current mirror. Considering only VDS and λ effects, 1 + (λc + λ m )2 V DS 2 Io = I D1 1 + (λc + λ m )1V DS1 [SI sat.] Spring 2002 EE 532 − Analog IC Design II Page 53 These, too, can be a significant source of error (e.g., 11%! if VDS1 = 2V, VDS2 = 4V, (λc + λm)1 = 0.04V-1, and (λc + λm)1 = 0.05V-1). Good layout practices for analog circuits include the following: 1) Use gate lengths several times larger than the technology’s minimum gate length if all possible. This helps reduces λ effects while improving matching. 2) Use multiple source/drain contacts along the width of the transistor to reduce parasitic resistance and provides evenly distributed current through the device. 3) Interdigitize large aspect ratio devices to reduce source/drain depletion capacitance. Using an even number (n) of gate fingers can reduce Cdb, Csb by one-half or (n + 2)/2n depending on source/drain designation. Typically it is preferred to reduce drain capacitance more so than source capacitance. Also use dummy poly strips to minimize mismatch induced by etch undercutting during fab. Spring 2002 EE 532 − Analog IC Design II Page 54 4) Matched devices should have identical orientation. An example of what not to do is shown below. 5) Interdigitization can be used in a multiple transistor circuit layout to distribute process gradients across the circuit. This improves matching. 6) Use common-centroid structures.