* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec - CEA-Irfu

Transistor–transistor logic wikipedia , lookup

Crystal radio wikipedia , lookup

Schmitt trigger wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Analog television wikipedia , lookup

Oscilloscope wikipedia , lookup

Oscilloscope types wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Radio transmitter design wikipedia , lookup

Cellular repeater wikipedia , lookup

Phase-locked loop wikipedia , lookup

Dynamic range compression wikipedia , lookup

Mixing console wikipedia , lookup

Rectiverter wikipedia , lookup

Index of electronics articles wikipedia , lookup

Oscilloscope history wikipedia , lookup

Operational amplifier wikipedia , lookup

Regenerative circuit wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Tektronix analog oscilloscopes wikipedia , lookup

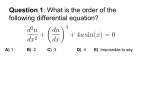

Ultra-fast differential front-end electronics • • • • Detectors as signal generators ~ Overview Low Z vs High Z Front-End Electronics (FEE), Differential vs. single ended FEE, Preliminary design & measurements G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 Front-end electronics – overview Detector as a fast signal generator electron-hole pairs collection only electrons (or particles) • • • • Front-end Electronics preamplifier preamplifiers & shapers & comparators test system cooling and grounding Main requirements: • • • • • • gain (sensibility), dynamic range (directly and/or ToT), S/N, rise/fall time and/or counting rates, crosstalk, EMI, EMC, power consumption etc. G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 Detector Signal Collection Circuit High Z Low Z + Rp Voltage source Zo Z - • Impedance adaptation • Amplitude resolution • Time resolution • Noise cut Low Z T Francis ANGHINOLFI ELEC-2005 Electronics in High Energy Physics Winter Term: Introduction to electronics in HEP Quo vadis ? Low Z output voltage source circuit can drive any load Output signal shape adapted to subsequent stage (ADC) Signal shaping is used to reduce noise (unwanted fluctuations) vs. signal Front-end electronics – overview Detector as fast signal generator electron-hole pairs collection only electrons (or particles) if Z is high charge is kept on capacitor nodes and voltage builds up (until capacitor is discharged) + Rp • Z - excellent E resolution - friendly pulse shape analysis • Detector FEE (Input stage) Advantages: Disadvantages: - channel-to-channel crosstalk - pile up above 40 k c.p.s. - sensitivity to e.m.c. G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 Front-end electronics – overview Detector as fast signal generator electron-hole pairs collection only electrons (or particles) if Z is low charge flows as a current through the impedance in a short time. + Rp • Z - limited signal pile up - limited channel-to-channel crosstalk - low sensitivity to parasitic signals - good timing resolution - • Detector FEE (Input stage) Advantages: Disadvantages: - pour signal/noise ratio G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 MRCP detectors for LHC Front-end electronics – overview Detector as fast signal generator electron-hole pairs collection only electrons (or particles) if Z is low charge flows as a current through the impedance in a short time. • Advantages: - limited signal pile up - limited channel-to-channel crosstalk - low sensitivity to parasitic signals - good timing resolution Single ended structure • Disadvantages: - pour signal/noise ratio Front-end electronics – overview Specifications: - Fully differential transimpedance - 0.18µm standard CMOS techn. - 10 GHz bandwidth - dynamic range 25 µA -2.5 mA - power consumption 88mW (2V) - Charge Sensitive Preamplifier Active Integrator (“Charge Sensitive (Pre)Amplifier”) • • • • • Input impedance very high ( i.e. NO signal current flows into amplifier), Cf (Rf) feedback capacitor (resistor) between output and input, very large equivalent dynamic capacitance, sensitivity A(q) ~ q / Cf, large open loop gain Ao ~ 10,000 - 150,000 Ci ~ “dynamic” input capacitance Rf G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 Standard Charge Sensitive preamplifiers developed at IKP Cologne et al. Main achievements: • • • • • • • • low noise, fast preamplifiers (segmented HP-GE & DSSSD) clean transfer function pulse shape …(no over/under-shoots) differential outputs for HP-Ge detectors & DSSSD-Si high dynamic range highly accurate spectroscopic TOT method (up to ~200MeV) incorporated programmable pulser (50 ppm long term) cryostat wiring (cold part), crosstalk less then 10 -3 miniature, SMD technology Who are our main users? - large arrays of segmented HP-Ge detectors : Miniball (CERN), Rising (GSI), SeGa (MSU), Tigress (Triumf), AGATA (EU) - DSSD Si detectors: LuSia (Lund,GSI), Miniball@IKP, LYCCA (GSI)… G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 Miniball HeKo basic structure Advantages: - discrete electronic components (e.g. HEMT, GaAs, SiGe) - can be easily integrated, - flexible open loop gain, - frequency compensation vs. detector unfriendly wiring Disadvantages: - to low open-loop gain - larger size G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 LYCCA CSPs Charge Sensitive Loop - basic structure Advantages: - the use of advanced current feedback operational amplifier, - very fast, - compact, small size, low PS Disadvantages: - to large open-loop gain, - limited frequency compensation vs. detector unfriendly wiring G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 GALI -S66 (GSI) G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 internal network compensation Miller 2x D N reworked frequency compensations G AGATA Single & Dual Gain Core Z Lead comp. (1. OpAmp) L D N L C - minimum Miller effect (min.) - lead compensation (min.) external network compensation C C C Detector AGATA C C central electrode F C R, G F i R C Pole j-FET L R Dominant C D N G Lead-lag 0 Cryostat wiring as part of the front-end electronics - lead-lag compensation (adj.) segment L R, L R, L R, L R, wiring + capsule detector AGATA L L - 1 Segment preamplifiers - R, D N G - 2..35 Segment R, to 36 Segment D N G - dominant pole compensation (adj.) LYCCA CSPs (32- channels) block diagram - basic structure Input: 68x high density flat band cable (SE*GND) Output: 32x Differential 100 Ohm*, 68x high density flat band cable x 32 channels G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 LYCCA - CSPs Transfer Function a) energy channel (differential out.) tr ~ 18 ns (Gain x1; Cd~10pF) tr ~ 29 ns (Gain x3; Cd~10pF) b) up-graded time channels (also with differential outputs) tr ~ 200 pS (tentative) LYCCA CSPs 200 MeV & 4 GeV 32 channels only with energy diff. outputs or 16 channels with both, energy and ultra fast diff. outputs mean min max Sub - nanosecond CSP • GaAs – HEMT (Q1, Q2) • ultra-fast, narrow time output (note: measured with existing scopes: tr ~ 500 ps, expected tr ~ 200ps !) • energy output tf~10 µs (no P/Z cancellation) • high counting rates timing > ~1 Mcps • • dominant pole compensation included low power, only +/- 6V E +/- 3V T) G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 LYCCA CSP modified for fast timing outputs: jFET: Bf861; BF862, FET: BF988 HEMT: ATF-55143 Id ~ from 2mA – 10 mA tr ~ 720 ps jFET, FET, HEMT selection a) jFET, FET - BF861 (1,B,C); BF862; BF 889 b) GaAs-FETs (E-pHEMT) - ATF-35143; ATF-55143; ATF-38143 c) Idrain, Vdrain to optimize the noise & bandwidth characteristics (10-15 mA, 2-2.7 V, 20-30mW) tr ~ 930 ps Pulse generator: Tektronix PG502 modified (less than 700ps rise/fall time) Scope: Tektronix TDS 3032 (300 MHz, 2.5 GHz sampling) jFET, FET, HEMT selection tr ~ 505 ps a) jFET, FET - BF861 (1,B,C); BF862; BF 889 b) GaAs-FETs (E-pHEMT) - ATF-35143; ATF-55143; ATF-38143 c) Idrain, Vdrain to optimize the noise & bandwidth characteristics (10-15 mA, 2-2.7 V, 20-30mW) Pulse generator: tr ~ 499 ps Tektronix PG502 modified (less than 700ps rise/fall time) Scope: LeCroy 44Xs (400 Mhz, 2.5 GHz sampling) jFET, FET, HEMT selection tf ~ 498 ps a) jFET, FET - BF861 (1,B,C); BF862; BF 889 b) GaAs-FETs (E-pHEMT) - ATF-35143; ATF-55143; ATF-38143 c) Idrain, Vdrain to optimize the noise & bandwidth characteristics (10-15 mA, 2-2.7 V, 20-30mW) Pulse generator: tf ~ 498 ps Tektronix PG502 modified (less than 700ps rise/fall time) Scope: LeCroy 44Xs (400 Mhz, 2.5 GHz sampling) G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 • Read-out from a MCP + dual delay line based position sensitive detector • Two mutually perpendicular delay lines * - Sobottka & Williams, IEEE Trans. NS (1988),35, p348 - Kozulin, Kondratiev et al.,Nucl.Exp.Tech., 2008 No 58, p.44-58 Preliminary design - test measurements Read-out from a MCP-based position sensitive detector LT6411 • 3300V/µs • 650 MHz • 50-100 mW / ch. G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 LYCCA CSPs (32- channels) block diagram - basic structure Input: 68x high density flat band cable (SE*GND) Outputs: 32x E - differential 100 Ohm*, 68x high density flat band cable x 32 channels G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 LYCCA like CSPs with implemented ultra-fast differential time outputs – 16x channels Input: 68x high density Outputs: 16x [E] ch. - differential 100 Ohm*, flat band cable (SE*GND) 32E out of 68 x high density flat band cable (10µs) (a) Diff. Comp. CML, LV-PECL, LVDS (b) tf ~10ns* (opt. ~ 100ns) x 16 channels Outputs: 16x [T] ch. - differential 100 Ohm*, 32T out of 68x high density flat band cable G. Pascovici, IKP-Cologne, FEE Meeting, Saclay, 04 Dec. 2008 To be decided: - with TOT ? - with spectroscopic TOT ? - differential signals standard: PECL, NECL, CML ? To be decided: - with TOT ? And where ? On [E] or on [T] channel ? - with spectroscopic TOT ? Or quasi spectroscopic? - differential signals standard: PECL, NECL, CML ? TOT circuitry? - requirements has to be decided ? -E or/and T ch.? GaAs(HEMT) +Transimpedance preamplifier-amplifier ~450 mW/ch + jFET 1 or 2 stages GaAs(HEMT) +Si-Ge amplifier+ Si-Ge ultrafast comparator ~60 mW/ch + jFET Potential solution with “motherboard” LYCCA architecture (8 -16 channels) Potential solution without “motherboard” Input Output architecture (2 - 4 channels) Ch1- timing Ch. 1 input Ch. 2 input Ch2- timing Advantages: • very fast • compact, small size • low PS (450mW/ch) • cooling in vacuum (~ 2D structure) • no motherboard architecture • impedance matching for UHF Ch. 1 output Ch. 2 output Disadvantages: w. motherboard no motherboard - power consumption in vacuum ? - motherboard architecture - impedance matching for UHF ? • solution only for small number of channels, • distribution of infrastructure signals (PS, adj.) • Sensitivity: A(t) ~100 mV/10 fC slope: Timing jitter [ walk ] dynamic range, even for constant rise/fall times Intrinsic jitter Ratio: amplifier rise time/ collection time M. Ciobanu et al, A FEE card comprising a high-gain amplifier and a fast discriminator for TOF measurements • CFD, ELD (extrapolated leading edge), ARC • correlated 2. channel • • • • [ jitter ] intrinsic noise, intrinsic jitter • noise distribution • bandwidth intrinsic jitter BW[Hz] bandwidth, Nd ~spectral density noise dispersion intrinsic time resolution IE1I+IE2I Electronic Design, Vol.46, No.25,1988 LVDS, CML differential interfaces common-mode range compared to single-ended noise margin. The effective noise margin is 2 to 4 times better using LVDS, CML…