* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Summary

Survey

Document related concepts

Transcript

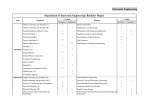

Summary Electronics II Lecture 5(b): Metal-Oxide Si FET MOSFET A/Lectr. Khalid Shakir Dept. Of Electrical Engineering College of Engineering Maysan University Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 1-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Summary The MOSFET The metal oxide semiconductor FET uses an insulated gate to isolate the gate from the channel. Two types are the enhancement mode (E-MOSFET) and the depletion mode (D-MOSFET). E-MOSFET An E-MOSFET has no channel until it is induced by a voltage applied to the gate, so it operates only in enhancement mode. An nchannel type is illustrated here; a positive gate voltage induces the channel. Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University RD Drain ID Induced SiO n 2 Gate p substrate n n channel + + – + + – – + – + – VDD n VGG – Source Page 2-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Summary The MOSFET The D-MOSFET has a channel that can is controlled by the gate voltage. For an n-channel type, a negative voltage depletes the channel; and a positive voltage enhances the channel. D-MOSFET RD A D-MOSFET can operate in either mode, depending on the gate voltage. RD n – – – – – – + + + + + + p n + – + + + + + + V DD – VGG + p + – V DD + n operating in D-mode Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University – – – – – – Page 3-21 VGG – n operating in E-mode st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Summary The MOSFET MOSFET symbols are shown. Notice the broken line representing the E-MOSFET that has an induced channel. The n channel has an inward pointing arrow. E-MOSFETs D D G G G S n channel D-MOSFETs D D S S p channel Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University G n channel Page 4-21 S p channel st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Summary The MOSFET The transfer curve for a MOSFET is has the same parabolic shape as the JFET but the position is shifted along the x-axis. The transfer curve for an n-channel E-MOSFET is entirely in the first quadrant as shown. I D The curve starts at VGS(th), which is a nonzero voltage that is required to have channel conduction. The equation for the drain current is ID K VGS VGS(th) 0 Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 5-21 VGS(th) +VGS st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Summary The MOSFET Recall that the D-MOSFET can be operated in either mode. For the n-channel device illustrated, operation to the left of the y-axis means it is in depletion mode; operation to the right means is in enhancement mode. I D As with the JFET, ID is zero at VGS(off). When VGS is 0, the drain current is IDSS, which for this device is not the maximum current. The equation for drain current is ID I DSS VGS(off) Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University I DSS –VGS VGS(off) Page 6-21 0 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Summary MOSFET Biasing E-MOSFETs can be biased using bias methods like the BJT methods studied earlier. Voltage-divider bias and drainfeedback bias are illustrated for n-channel devices. +VDD +VDD RD R1 R RD G R2 Voltage-divider bias Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 7-21 Drain-feedback bias st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Summary MOSFET Biasing The simplest way to bias a D-MOSFET is with zero bias. This works because the device can operate in either depletion or enhancement mode, so the gate can go above or below 0 V. +VDD +V DD RD VG = 0 V VGS = 0 RD IDSS ac C input RG RG Zero bias, which can only be used for the D-MOSFET Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 8-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Selected Key Terms JFET Junction field-effect transistor; one of two major types of field-effect transistors. Drain One of three terminals of a FET analogous to the collector of a BJT. Source One of three terminals of a FET analogous to the emitter of a BJT. Gate One of three terminals of a FET analogous to the base of a BJT. Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 9-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Selected Key Terms Transconductance The ratio of a change in drain current to a (gm ) change in gate-to-source voltage in a FET. MOSFET Metal oxide semiconductor field effect transistor; one of two major types of FETs; sometimes called IGFET. Depeletion In a MOSFET, the process of removing or depleting the channel of charge carriers and thus decreasing the channel conductivity. Enhancement In a MOSFET, the process of creating a channel or increasing the conductivity of the channel by the addition of charge carriers. Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 10-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 1. If an n-channel JFET has a positive drain voltage and the gate-source voltage is zero, the drain current will be a. zero b. IDSS c. IGSS d. none of the above Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 11-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 2. For a JFET, two voltages with the same magnitude but opposite signs are a. VD and Vp b. VD and VS c. VGS(th) and Vcutoff d. Vp and VGS(off) Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 12-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 3. A set of characteristic curves for a JFET are shown. The blue lines represent different values of a. VDS ID b. VGS c. VS d. Vth VDS Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 13-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 4. Transconductance can be expressed as a. gm g b. m g c. VDS I D m g d. ID VGS IG m VIDS G GS V Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 14-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 5. JFETs cannot be biased using a. self bias b. voltage-divider bias c. zero bias d. current-source bias Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 15-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 6. The JFET operating point in the circuit shown is a. at the origin b. at Isat VCC +15 V c. at VCC C1 d. undefined Page 16-21 R 3.9C k Vout Q1 2N3904 C2 1.0 µF Vs = 400 mV pp 1.0 kHz Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University R1 56 k R2 39 k 10 µF R E 6.2 k Q2 2N5458 R3 100 k ff VGG st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 7. The JFET in this circuit acts like a(n) a. voltage source b. amplifier VCC +15 V c. capacitor C1 d. resistor Page 17-21 RC 3.9 k Vout Q1 2N3904 C2 1.0 µF Vs = 400 mV pp 1.0 kHz Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University R1 56 k R2 39 k 10 µF RE 6.2 k Q2 2N5458 R3 100 k ff VGG st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 8. The symbol for a p-channel E-MOSFET is D G D D G G D G S S S S a. b. c. d. Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 18-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 9. The transfer curve shown is for an n-channel a. E-MOSFET ID b. D-MOSFET c. JFET d. all of the above 0 Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 19-21 VGS(th) +VGS st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz 10. A type of FET that can use the same bias method as a BJT is a(n) a. E-MOSFET b. D-MOSFET c. JFET d. all of the above Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University Page 20-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved Quiz Answers: Copyright @2013 by Dept. of Electrical Engineering, College of Engineering, Maysan University 1. b 6. a 2. d 7. d 3. b 8. b 4. a 9. a 5. c 10. a Page 21-21 st Semester 2008 Pearson Education, Inc. Electronics II- Lecture 5(b)/1© 013/014 All rights reserved