* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Class D amplifier

Chirp compression wikipedia , lookup

Spectrum analyzer wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Dynamic range compression wikipedia , lookup

Oscilloscope wikipedia , lookup

Chirp spectrum wikipedia , lookup

Regenerative circuit wikipedia , lookup

Oscilloscope types wikipedia , lookup

Spectral density wikipedia , lookup

Pulse-width modulation wikipedia , lookup

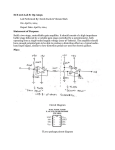

EXPERIMENT NO.II.11 CLASS D AMPLIFIER I. OBJECTIVES a) Understanding the operating principle of class D amplifier. b) The knowledge of a pulse-width-modulation method. c) The knowledge of a method to drive a push-pull stage with MOSFET with avoidance of the “shoot through” phenomenon. d) The knowledge of a method to reconstruct the amplified signal from the pulsewidth modulated signal II. COMPONENTS AND INSTRUMENTATION We use the experimental circuit presented in Fig.II.11.1. The input sinusoidal voltage will be supplied by a signal generator. The signals from the circuit will be measured using a dual-channel oscilloscope. The circuit is powered from a dual dc regulated power supply adjusted at ± 9V. III. PREPARATION A class D amplifier is one in which the output transistors are operated as switches. When a transistor is off, the current through it is zero. When it is on (extreme conduction), the voltage across it is small, ideally zero. In each case the power dissipation is very low. This increase the efficiency, thus requiring less power from the power supply and smaller heat sinks for the amplifier. These are important advantages in portable battery powered equipment. First, the input signal vs is converted into a pulse-width-modulated (PWM) signal. In order to achieve this, the input signal is compared with an (almost) triangular waveform vt with a much higher frequency than that of the input signal. The resulting PWM signal is amplified in the current (power) by means of the final stage with two complementary MOS transistors. The amplified signal is reconstructed to its initial shape using a low pass filter (usually LC), that remove the switching frequency. As one can see in Fig. II.11.1, the block diagram of the amplifier contains the following blocks: 95 Triangular waveform generator: 555 timer, D1, D2, R1, R2, C1, C2; Pulse-width-modulator: LF412 op-amps used as simple comparators OAp şi OAn, C5, C6, D3, D4, R3 – R8; Final stage: Tp, Tn R9, R10; Filter: L1,C7, L2, C8. P1. Triangular waveform generator The astable multivibrator circuit composed by the 555 IC and afferent passive components generates an almost triangular waveform in the point T by charging up (through R1 and D1 from +VPS) and discharging (through R2 and D2 to the ground) the C1capacitor. Even the risings up and falling down portions of the signal are no linear ones (in fact they are exponential), we will call further this signal triangular waveform. Prove that the triangular waveform varies between 3V and 6 V with the frequency ft (the voltage across the diode in conduction is neglected): 1 f t R R C ln 2 1 2 1 What is the value of the frequency? What are the amplitude and dc component of the triangular waveform in point T? What does the signal in point T look like considering 26,7KHz frequency and 4.5V dc component? P2. Pulse-width-modulator In the Pulse-width –modulator block the input signal applied in the S point should be compared with a triangular waveform with 0V dc level. The resulting rectangle (width-modulated) signal is to be applied into the gates of the MOSFETs from the final stage. In this case both transistors are simultaneously driven with the same signal. The “shoot through” phenomenon that can appear leads to a reduction of the efficiency and to a potential failure of the transistors. This occurs during the transition when one device is being switched off and another one is being switched on. During the transition, both devices are on and a large current pulse can flow through the two. The “shoot through” phenomenon can be eliminated by driving the gates of the MOSFETs with asymmetrical square waveforms such that one device is switched off before the other is switched on. One way to accomplish this is by driving the gates of the MOSFETs with asymmetrical square waveforms. We will use two comparators OAp and OAn, one for each MOSFET. A positive dc offset is added to the triangle waveform input to the comparator which drives Tp transistor, while a 96 negative dc offset is added to the triangle waveform input to the comparator which drive Tn transistor. These offset voltages are provided by the R3 – R5, D3 group and respectively, R6 – R8, D4 group. Consider a sine waveform with 1V amplitude and 2 KHz frequency applied to the input in the S point. Plot the signals in the points S, Top and Ton. What does the signals in the points Mp and Mn look like? Are they asynchronous rectangular signals width-modulated (variable duty-cycle)? P3. Final stage Consider in the points Mp and Mn the signals found in the P2 paragraph. What is the role of R9 and R10? You may take into account the parasitic capacities in the gates of the transistors. How does the Tp – Tn work: in active region (permanent conduction) or in switching regime? Determine the waveforms for the currents through the Tn and Tp. Determine the waveforms for the drain to source voltages for Tn and Tp. Estimate the signal in the point U. P4. Filter The reconstruction of the amplified signal from the PWM signal is achieved with two LC low pass cells. What is the resonance frequency for each cell? What is the attenuation outside the bandwidth, for each cell and for the full filtering network? We mention the values for the passive components were chosen so that the cut off frequency at 3dB attenuation is the same with the input signal frequency (2 KHz). In the frequency spectrum of the signal in point U the spectral component with the higher amplitude is the one with the ft=26,7KHz (triangular signal frequency) followed by the one with fs=2 KHz (sinusoidal signal frequency). After the first filtering cell (in the point O1), in the frequency spectrum of the signal the spectral component with the higher amplitude is the one with the fs=2KHz followed by the ones with 2ft-fs and 2ft+fs frequency. To the circuit output (point O) the entire superior spectral component has much less amplitudes than the component with 2 KHz frequency (amplified signal frequency), so the signal is reconstructed. Estimate the signals in the points O1 and O. 97 IV. EXPLORATIONS AND RESULTS E1. Triangular waveform generator Exploration Supply the experimental board with symmetrical differential voltage 9V. Visualize with the oscilloscope and plot the signal in the point T. Measure the dc level, minimum and maximum values and frequency. Results The picture of the whole operation of the class D amplifier can be created by observing the signals in the important points of the circuit. A very good idea is to plot the signals in the points T, Top, Ton, Mp, Mn, U, O1, and O, one below the other, time correlated. So let’s do it! What are the measured values of the frequency, amplitude and dc level of the signal? E2. Pulse-width –modulator Exploration Apply in the point S a sine waveform with 1V amplitude and 2KHz (measure the amplitude on the screen of the scope Visualize with the oscilloscope and plot the signals in the points Top, Ton. Visualize simultaneously with the oscilloscope and plot the signals in the points Top, Mp, respectively Ton, Mn. Visualize simultaneously with the oscilloscope and plot the signals in the points Mp, Mn. Results What are the offsets value of the signals in the points Top and Ton? How can you explain the waveforms in the points Mp and Mn? What is the range of variation for the duty-cycle in each point? Compare the two signals from the point of view of the duration for high level (9V), and respectively for the low level (-9V). What is the reason responsible for the differences between them? E3. Final stage Exploration Visualize simultaneously with the oscilloscope and plot the signals in the points Mp and U and afterwards in the points Mp and U. 98 How can you obtain the waveforms for the currents through R9 and R10? Tip: Visualize simultaneously the potentials to the both ends of one resistor in respect to the ground, than set the oscilloscope so that it shows you the difference between the two signals. So you know now the voltage drop across the resistor and also know the value of the resistor… Results How is the signal in the point U compared with the signal in the point Mp (inverting/non-inverting, greater, less or equal amplitude)? What is the maximum value of the current in the gate of each transistor? What is the reason for the presence of this current? What does the waveforms of the drain to source voltages look like? Do the two transistor work in out of time regime? Can you justify the answer? What is the working frequency of the final stage? How is it by comparison with the frequency of the amplified signal? E4. Filter Exploration Visualize simultaneously with the oscilloscope the signals in the points U and O1 and afterwards in the points U and O. Plot the three signals one below the other. Results How can you explain de waveform in the point O1? What are the spectral components with greatest amplitudes? Who establish the signal amplitude? Compare the waveforms of the input (point S) and output (point O) signals by the points of view of amplitude, phase shifting, frequency spectrum. Can you assert that the output signal was “reconstructed”? 99 +Vps=+9V C4 VCC TRIGGER RESET OUTPUT CONTROL THRESHOLD DISCHARGE GND +Vps=+9V 0 R4 0 3 D3 20k R5 20k C5 U2A 0 3 Top 47n R2 1 2 2.2k 4.7k + OUT - LF412 1 Mp IRF9533 R9 Tp -Vps=-9V 4.7 4 C2 10n D1 +Vps=+9V 8 2 4 5 6 7 R3 1k 47n V+ R1 2.2k 4.7k C3 100u U5 V- 8 555B C6 D2 T vs S 9m 9m R10 1V 2KHz C7 +Vps=+9V U3A 0 3 Ton + 8 10n 3.3n C1 O1 L2 47n 0 OUT R8 R6 - D4 -Vps=-9V D1N4148 0 Fig.II.11.1 Experimental circuit for class 95 100n 220 0 -Vps=-9V O C8 RL1 Mn LF412 1k 20k 1 4 20k 2 100n IRF520 V- 0 R7 Tn 4.7 V+ 0 U L1 RL 220 95