* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Substrate Noise Isolation Characterization in 90 nm CMOS

Survey

Document related concepts

Transcript

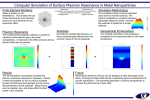

Substrate Noise Isolation Characterization in 90 nm CMOS Technology Sergei Kapora1, Wim Schoenmaker2, Peter Meuris2 1 NXP, Prof. Holstlaan 4, 5656 AA Eindhoven Netherlands, 2 [email protected] MAGWEL, Martelarenplein 13, B-3000 Leuven Belgium, [email protected], [email protected] Presented by Mike Stuber, Magwel DAC Track 2009 1 Substrate Noise Problem Noise coupling is one of the biggest challenges for deep submicron SOC mixed-signal designs today: 2 Goal / Use Model 3D simulation tool for substrate noise propagation analysis is introduced Simulation results are in good agreement with measurements. This enables us to - evaluate different isolation approaches (layout and process) - formulate guidelines for substrate noise isolation - reduce the number of expensive tape-outs of test chips Resulting in more accurate, quicker chip design 3 Problem Complexity The coupling takes place 1) in the back-end metallization, 2) the front-end substrate 3) in the back-end/front-end connection. Different mechanisms occur: - conductive coupling in metal and substrate - capacitive coupling: - between the metal lines - in the substrate (junctions) - between metal and substrate - magnetic coupling between intended and unintended loops 4 Magwel’s solution: Unique and patented technology ¾ Simultaneous 3D simulation of − back-end (Maxwell) − front-end (drift-diffusion) ¾ Frequency domain solver ¾ Depth-dependent doping concentration ¾ Gds2 import feature ¾ Connection of external circuit / package model 5 What Do We Solve ? - Maxwell's equations everywhere - Ohm's equation in metal -Drift-diffusion equations in substrate -When not needed, magnetic solution can be turned off 6 Impact of Coupled Solutions ¾ ¾ Full coupling in the electromagnetic and semiconductor device equations allows analysis of parasitic coupling between the two domains For example − − − − − DC bias of inductor over high-resistivity substrate -> inversion layer (semiconductor effect) Carrier recombination -> inversion charge (semiconductor effect) Inductor RF power -> current in the inversion layer (coupled EM and semiconductor) recombination and surface mobility effects -> current (semiconductor effects) Inversion layer current -> additional magnetic field (EM effect) which feeds back to the inductor (coupled EM and semiconductor) 7 editEM and solvEM Tools ¾ ¾ Two tools work together to arrive at the solution editEM is used to create the structure and define the simulation conditions − − − − ¾ Material coefficients Layer thicknesses GDSII import and drawing tools Doping profiles solvEM contains the engine that performs the numerical solutions 8 Test structure (1) Aggressor Victim metal stack SUB DNW P+ DNW SUB substrate ¾ ¾ Test chip in 90nm CMOS technology 6 different DNW structures (square and rectangular) ¾ Reference and de-embedding structures ¾ Measurements on wafer up to 40 GHz 9 Test structure (2) ¾ Simplifications in gds2 file − Removing tiles − Merging small vias together isolated PW DNW psubstrate Doping profile of isolated PW with DNW ¾ Simplified gds2 file merged with technology file − Doping profiles − Metal stack Full stack, including metal layers 10 S-parameters - Measured vs. Modeled S11 and S21 for DNW structure 20x12 um2 Good agreement between measurements and simulations Special attention to be paid to mesh and solver settings Contribution of metal stack coupling is not negligible (see next page) 11 Separating Contributions ¾ ¾ Simulation without interconnect isolates substrate effects from interconnect effects Different contributions can be separated and quantified – Substrate vs. interconnect – E-field vs. B-field – Multiple aggressors or victims With and without interconnect 12 Results for Varied DNW Size 1 DNW 2 DNW Varied width 3D model, RC components only for explanation of RC behaviour Only substrate (no metal stack) is considered “Ideal” biasing of DNW (0Ω connection to 0V) Noise isolation from substrate (1) to Pwell tap (2), DNW width varied 13 Different Isolation Schemes Simple structures: Draw layout in editEM, simulate. No protection A V P+ ring A V Full DNW A V 14 Additional Insights ¾ Tool is used for development of noise isolation guidelines ¾ Effectiveness of different protection structures (guard rings etc.) ¾ DNW contacting strategy ¾ Influence of PW-DNW diode biasing impedance on isolation levels ¾ Includes all coupling paths (conductive, capacitive, inductive) ¾ Not limited to bulk CMOS processes (SOI, BiCMOS, 3D IC) ¾ Results can be represented as scalar or vector plots of all solved parameters (e.g. voltage and current density) that point to process or layout improvements Top-down views of voltage distribution at silicon surface 15 Tool Capabilities ¾ ¾ ¾ ¾ Complex 3D structures up to hundreds of thousands of mesh nodes can be simulated with full EM and device equation coupling, up to millions of nodes with reduced interactions Doping profile import for process sensitivity studies, process change studies GDSII import for efficient measured vs. modeled comparisons GDSII import for efficient layout sensitivity studies (substrate hidden) RF Noise injection structure 16 Conclusions ¾ Complex substrate noise problems can be directly simulated in 3 dimensions, including − Doping profile import (process change impact) − GDSII layout import (re-use of existing structures) − High aspect ratio grids (deep sub-micron structures separated by hundreds of microns) − Fully coupled electromagnetic and device equations (LRC effects) − Visualization of all solved parameters (potential, current density, magnetic field) for insight 17