* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Current Source Biasing

Pulse-width modulation wikipedia , lookup

Mains electricity wikipedia , lookup

Stray voltage wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Ground loop (electricity) wikipedia , lookup

Earthing system wikipedia , lookup

Integrated circuit wikipedia , lookup

Surge protector wikipedia , lookup

Semiconductor device wikipedia , lookup

Power electronics wikipedia , lookup

Buck converter wikipedia , lookup

Alternating current wikipedia , lookup

Two-port network wikipedia , lookup

Current source wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

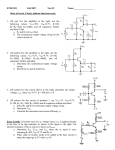

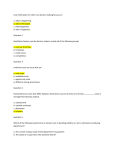

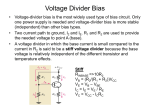

Current Source Biasing • Integrated circuits have transistors which are manufactured simultaneously with the same device parameters (parameters from chip to chip will vary) • As a result, different bias techniques are employed than in discrete designs • One common technique is current source biasing, which allows the designer to take advantage of matched devices • We will begin by looking at some simple current source circuits • A current source is not a “naturally” occurring device. It can be simulated by a network of transistors and circuit elements. The voltage across RE is approximately constant. ∴ IE is held at a constant value IE = −VEE − VBE RE Problem: For the previous circuits find the bias values IC and VCE for each transistor Solution Assume D1 and D2 forward biases (I1 > IB2) VB = VEE + 2VF = − 10 V + 2 ( 0.7 V) = − 8.6 V Using KVL around loop A 2VF = VBE 2 + I E 2 R2 Since VBE 2 ≅ VF V 0.7 V IE2 = F = ≅ 3.7 mA R2 180 Ω Since IC ≅ I E IC1 = IC 2 = 39 . mA Check that D1 and D2 are forward biased for a worst case minimum βF = 20 I B2 = I1 = IC 2 ≅ 019 . mA βF VCC − VB 10 V − ( −8.6 V ) = = 0.37 mA 50 kΩ R1 . mA)(1kΩ ) = 61 .V VC1 = VCC − IC1 RC = 10 V − (39 VE 2 = VB − VBE 2 = − 8.6 V − 0.7 V = − 9.3 V VE1 = VC 2 = 0 V − VBE1 = − 0.7 V . V − ( −0.7 V) = 6.8 V VCE1 = VC1 − VE1 = 61 VCE 2 = VC 2 − VE 2 = − 0.7 V − ( −9.3 V) = 8.6 V Current Mirrors • Current mirrors also take advantage of matched transistors but require a minimal number of resistors. They are also well suited for circuits with more than one stage. Basic BJT Current Mirror IA = VCC − (VCE1 + VEE ) VCC − VBE1 − VEE = RA RA I A = I REF + I B1 + I B 2 IF β F is large I B1 << I REF I B 2 << I REF I REF ≅ I A Problem For the following circuit IC3 = 3 mA and VCE = 5.4 V. Find the quiescent (DC bias) power dissipated in each transistor. IC 3 ≅ Io = I REF ≅ I A IA = 0 V − (VF + VEE ) RA RA = −VF − VEE −0.7 V − ( −10 V) = = 31 . kΩ 3mA I REF VE = − 0.7 V; To achieve VCE = 5.4 V, VC = 4.7 V VCC − VC = 10 V − 4.7 V = 5.3 V RC = 5.3 V = 18 . kΩ 3 mA The DC power in each transistor is given by: PQ = I CVCE + I BVBE ≅ ICVCE PQ1 = (3 mA)( 0.7 V) = 0.2 mW PQ 2 = (3 mA)[−0.7 V − ( −10 V)] ≅ 28 mW PQ3 = (3 mA)(5.4 V) = 16 mW MOSFET Current Mirror Advantage: IREF = IA Gate current is negligible Widlar Current Source • The basic current mirror requires that the bias current and reference current be equal • The wildar current source sets the mirrored current to a value smaller than IREF by using an extra resistor • The widlar current source allows you to establish small bias currents (µA) without using large resistor values I REF ≅ VCC − V EE − V BE1 RA VBE1 = VBE 2 + I E 2 R2 V BE VBE η V η VT T I E = I EO e − 1 ≅ I EO e VBE = ηVT ln IE I EO Assuming matched BJTs ηVT ln I E1 I = ηVT ln E1 + I E 2 R2 I EO I EO I E1 I E 2 R2 = ηVT ln IE2 I E1 ≅ I REF Io = • • I E 2 ≅ Io ηVT I REF ln R2 Io Equation difficult to solve in closed form. Use successive iteration or trial and error When you know the desired Io then IREF can be found directly I R I REF = I o exp o 2 ηVT Problem: Using a widlar current source find the values of RA and RB that will produce Io = 100 µA. Given VCC = 10 V, VEE = -10 V, VF = 0.7 V and η = 1. Solution: Select a value of R2 such that I o R2 ≅ ηVT To keep exponent from becoming too large ηVT = 25 mV Choose I o R2 = 100 mV ∴ R2 = 1 kΩ (100 µA)(1kΩ ) I REF = (100 µA ) exp = 5.46 mA 0.025 V I REF = RA = VCC − VEE − VF RA 10 V − ( −10 V) − 0.7 V = 354 . kΩ 5.46 mA Wilson Current Source • Refined Widlar source that can produce IO > IREF • The balance between VBE1 and VBE2 is set by the ratio of R1 to R2 Assuming IC ≅ I E VBE1 + I REF R1 = VBE 2 + I o R2 ηVT ln I REF I + I REF R1 = ηVT ln o + Io R2 I EO1 I EO 2 Assuming matched devices Io = ηVT I REF R ln + I REF 1 R2 Io R2 Small Signal Modeling of Three Terminal Devices • Incremental signals • Piecewise linear models • Incremental circuit models – BJT – FET • Refinements to incremental model – Output resistance – Input resistance – Alternative BJT representation • Two - port representations Small Signal Modeling of Three Terminal Devices • Related to PWL concept in which the V-I characteristics are modeled by a straight line tangent to the curve at a particular operating point • With three terminal devices the relationship between the output port and input port must be taken into account. This generally leads to a PWL model with a linearly dependent source. • Circuits containing small signal models can be analyzed using linear circuit theory under proper conditions • The terms small-signal and incremental will be used interchangeably Incremental Signals • Any transient, periodic or AC fluctuation in a voltage or current • An incremental signal is small in magnitude compared to the bias voltages or currents in the circuit • Incremental signal carries the signal information processed by the circuit PWL Models of Three Terminal Devices • Formation of small signal model begins with PWL model • PWL model can be applied to three terminal device if the dependency of the output port is considered rBE • • ∂ vbe = ∂ ib VBE , I B ηVT = IB Model valid only in constant current region If the circuit in which the BJT is connected produces a signal as well as a bias component to iB then: ic (t ) = β ο ib (t ) • • where ic and ib are inc remental signals and βο is the incremental current gain • Since βF is fairly constant it is possible to assume βο = βF in many cases • The symbols hFE and hfe are sometimes used instead of βF and βο when using h-parameter analysis Incremental Circuit Model In analyzing the small signal performance of a circuit it is customary to ignore the DC components of the model once the bias conditions have been established. This can be accomplished by the following procedure: 1. Find the DC bias point and determine an appropriate PWL model 2. Set all bias values to zero by setting all DC sources to zero (including those in the PWL model) 3. Solve the desired variables using linear circuit theory 4. Superimpose the signal variables onto the corresponding DC bias voltages and currents to obtain the total voltage and current values IB = VBB − VF 1 V − 0.7 V = = 30 µA RB 10 kΩ IC = β F I B = (100 )(30 µA ) = 3 mA VOUT = VCE = VCC − IC RC = 10 V − (3 mA)(1kΩ ) = 7 V • Transistor operates in constant current therefore we can use PWL model developed earlier rbe = ηVT 1(0.025) = ≅ 833 Ω IB 30 µA ib = vs RB + rbe vo = − β ο RC −100 (1 kΩ ) vs = v s ≅ − 9.2 v s RB + rbe 10 kΩ + 0.833 kΩ − β ο RC RB + rbe vo = − β ο ib RC is the incremental or small - signal voltage gain VOUT = VCE Total = Bias + Incremental Voltage + vo ( t ) Voltage Signal = 7 V − 9.2 v s ( t ) Problem: For the following circuit find the incremental components of vc and ve. Note: vs connection does not represent typical amplifier design. KVL around the input loop for incremental signal R1 vs = ib ( R1 R2 ) + ib rπ + ( β ο + 1) ib RE R1 + R2 R v s 1 ( R + R ) 1 2 ib = ( R1 R2 ) + rπ + ( β ο + 1) RE (β ο + 1) RE R1 ( R v s 1 + R2 ) ve = ( β ο + 1) ib RE = ( R1 R2 ) + rπ + ( β ο + 1) RE R β ο RC 1 ( R + R ) v s 1 2 vc = − ( β ο ib ) RC = − ( R1 R2 ) + rπ + ( β ο + 1) RE In the limit R1 R2 << ( β ο + 1) RE βο +1 ≅ βο rπ << ( β ο + 1) RE ve ≅ R1 vs R1 + R2 vc ≅ − RC R1 vs RE R1 + R2 Incremental Model of MOSFET ∂ iD gm = ∂ v GS VGS , I D ∂ = k (VGS − VTR )2 ∂ vGS [ ] V ,I GS D Assume constant current operation VGS − VTR I = D k 1/ 2 gm = 2 k I D Similar expression can be derived for JFET = 2 k (VGS − VTR ) • An incremental description for a FET can also be defined for triode (resistive) region • It can be shown that the incremental model is as follows rds = 1 2 k (VGS − VTR ) gm = 2 k VDS Problem: (A) Find the small signal componont of VOUT for the 2 following circuitd vs = 0.1 Sin ωt, k = 0.2 mA/V , VTR = -2 V. (B) Find the Thevenin circuit between VOUT and ground .. The bias values can be found to be I D ≅ 0.47 mA VGS = − I D RE = − 0.47 V Applying KVL to output loop VDS = VDD − I D ( RD + RE ) = 10 V − ( 0.47 mA)(3k) = 8.6 V • Since VDS > (VGS −VTR) = 1.53 V the device operates in the constant current region The incremental transconductance gm is given by gm = 2 k (VGS − VTR ) = 2 (0.2 mA / V 2 ) [ −0.47 V − ( −2 V)] ≅ 0.61 mA / V • The signal component of vOUT can be found by substituting the PWL model and setting all DC sources to zero Applying KVL to the output loop v gs = v s − id RE = v s − ( g m v gs ) RE v gs = vs 1 + g m RE ∴ Note feedback limits the fraction of v s that appears as v gs v OUT = − id RD = − g m v gs RD v OUT = aV = − g m RD vs 1 + g m RE v OUT − g m RD − ( 0.61 mA / V)(2 kΩ ) = = = − 0.76 vs 1 + g m RE 1+ (0.61mA / V)(1kΩ ) v OUT = aV v s = ( −0.76 )( 01 . sin ωt) = − 0.076 sin ωt • Since vOUT is computed with no load it represents the incremental open circuit Thevenin voltage • The incremental rth can be found by setting vs to zero and applying vTEST v gs = g m v gs RE itest = rth = v test RD vtest = RD itest can only be satisfied if v gs = 0