* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

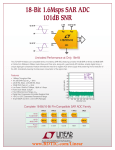

Download AD9221/AD9223/AD9220 Complete 12

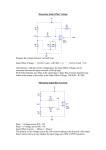

Quantization (signal processing) wikipedia , lookup

Signal-flow graph wikipedia , lookup

Control system wikipedia , lookup

Linear time-invariant theory wikipedia , lookup

Alternating current wikipedia , lookup

Voltage optimisation wikipedia , lookup

Dynamic range compression wikipedia , lookup

Scattering parameters wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Mains electricity wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power electronics wikipedia , lookup

Two-port network wikipedia , lookup

Oscilloscope types wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Oscilloscope wikipedia , lookup

Buck converter wikipedia , lookup

Integrating ADC wikipedia , lookup

Oscilloscope history wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Schmitt trigger wikipedia , lookup

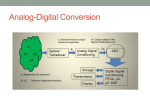

Analog-to-digital converter wikipedia , lookup