* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Chap007-2011

Microprocessor wikipedia , lookup

Flexible electronics wikipedia , lookup

Opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

Electronic engineering wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Rectiverter wikipedia , lookup

Regenerative circuit wikipedia , lookup

Index of electronics articles wikipedia , lookup

RLC circuit wikipedia , lookup

Hardware description language wikipedia , lookup

Digital electronics wikipedia , lookup

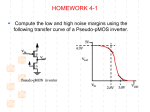

Chapter 7 Complementary MOS (CMOS) Logic Design Microelectronic Circuit Design Richard C. Jaeger Travis N. Blalock Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 1 Chapter Goals • • • • • • • • • • Introduce CMOS logic concepts Explore the voltage transfer characteristics of CMOS inverters Learn to design basic and complex CMOS logic gates Discuss the static and dynamic power in CMOS logic Present expressions for dynamic performance of CMOS logic devices Present noise margins for CMOS logic Introduce dynamic logic and domino CMOS logic techniques Introduce design techniques for “cascade buffers” Explore layout of CMOS logic gates Discuss the concept of “latchup” Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 2 CMOS Inverter Technology • Complementary MOS, or CMOS, needs both PMOS and NMOS devices for the logic gates to be realized • The concept of CMOS was introduced in 1963 by Wanlass and Sah, but it did not become common until the 1980’s as NMOS microprocessors were dissipating as much as 50 W and alternative design technique was needed • CMOS dominates digital IC design today Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 3 CMOS Inverter Technology • The CMOS inverter consists of a PMOS device stacked on top on an NMOS device, but they need to be fabricated on the same wafer • To accomplish this, the technique of “n-well” implantation is needed as shown in this cross-section of a CMOS inverter Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 4 CMOS Inverter (a) Circuit schematic for a CMOS inverter (b) Simplified operation model with a high input applied (c) Simplified operation model with a low input applied Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 5 CMOS Inverter Operation • When vI is pulled high (to VDD), the PMOS transistor is turned off, while the NMOS device is turned on pulling the output down to VSS • When vI is pulled low (to VSS), the NMOS transistor is turned off, while the PMOS device is turned on pulling the output up to VDD Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 6 CMOS Inverter Layout • Two methods of laying out a CMOS inverter are shown • The PMOS transistors lie within the n-well, whereas the NMOS transistors lie in the psubstrate • Polysilicon is used to form common gate connections, and metal is used to tie the two drains together Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 7 Static Characteristics of the CMOS Inverter • The figure shows the two static states of operation with the circuit and simplified models • Notice that VH = 5V and VL = 0V, and that ID = 0A which means that there is no static power dissipation Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 8 CMOS Voltage Transfer Characteristics The VTC shown is for a CMOS inverter that is symmetrical (Kp = Kn). Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 9 CMOS Voltage Transfer Characteristics • The simulation results show the varying VTC of the inverter as VDD is changed • The minimum voltage supply for CMOS technology is VDD = 2VT ln(2) V Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 10 CMOS Voltage Transfer Characteristics • Simulation results show the varying VTC of the inverter as KN/KP = KR is changed • For KR > 1 the NMOS current drive is greater, and it forces transition region vI < VDD/2 • For KR < 1 the PMOS current drive is greater, and it forces transition region vI > VDD/2 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 11 Noise Margins for the CMOS Inverter Noise margins are defined by the points shown in the given figure Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 12 Noise Margins for the CMOS Inverter KR KN KP NML VIL VOL NM H VOH VIH 2K R VDD VTN VTP VDD K RVTN VTP VIH K R 1 K R 1 1 3K R VOL K R 1VIH VDD K RVTN VTP 2K R 2 K R VDD VTN VTP VDD K RVTN VTP VIL K R 1 K R 1 K R 3 VOH K R 1VIL VDD K RVTN VTP 2 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 13 Propagation Delay Estimate • The two modes of capacitive charging/discharging that contribute to propagation delay Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 14 Propagation Delay Estimate PHL RonN p V H VTN 2VTN RonNCln 4 1 V H VL V H VTN 1 K n V H VTN PHL PLH 2 PHL 1.2RonNC • If it is assumed the inverter in “symmetrical” with (W/L)P = 2.5 (W/L)N, then PLH = PHL Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 15 Rise and Fall Times • The rise and fall times are given by the following approximate expressions: t f 3 PHL t r 3 PLH Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 16 Reference Inverter Design Example • Design a reference inverter to achieve a delay of 250ps with a 0.1pF load given the following information: VDD 3.3V C 0.1 pF p 250 ps VTN VTP 0.75V Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 17 Gate Device Geometry Scaling based Upon Reference Circuit Simulation • State-of-the-art short gate length technologies are hard to analyze • Scaling can be used to properly set W/L for a given load capacitance relative to reference gate simulation with a reference load. W / L CL P W / L' CLref Pref or W ' W Pr ef L L P CL CLref Scaling allows us to calculate a new geometry (W/L)' in terms of a target load and delay. Jaeger/Blalock 3/15/10 Microelectronic Circuit Design, 4E McGraw-Hill Chap 67 - 18 Performance Scaling • Consider a reference inverter with a delay of 3.16 ns. • What is the delay if an inverter has a W/L 4x larger than the transistors of the reference inverter and twice the load capacitance. 2 /1 2 pF' P 3.16 ns 1.58 ns 8 /1' 1pF Scaling allows us to calculate a new geometry (W/L)' or delay relative to a reference design. Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 19 Reference Inverter Design Example • Assuming the inverter is symmetrical and using the values given in Table 7.1: K 100 ' n A 2 V A ' K p 40 2 V p PHL PLH 250 ps Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 20 Reference Inverter Design Example • Solving for RonN: RonN PHL VDD VTN 1 Cln 4 1 VDD VL 2 1040 • Then solve for the transistor ratios: W 1 3.77 ' L n K n RonN VDD VTN 1 W K n' W W 9.43 ' 2.5 L p K p L n L n 1 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 21 Delay of Cascaded Inverters • An ideal step was used to derive the previous delay equations, but this is not possible to implement • By using putting the following circuit in SPICE, it is possible to produce more accurate equations Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 22 Delay of Cascaded Inverters • The simulated output of the previous circuit appears below, and it can be seen that the delay for the nonideal step input is approximately twice than the ideal case: PHL 2.4RonNC PLH 2.4RonPC t f 2 PHL t r 2 PLH Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 23 Static Power Dissipation • CMOS logic is considered to have no static power dissipation • This is not completely accurate since MOS transistors have leakage currents associated with the reverse-biased drainto-substrate connections as well as sub-threshold leakage current between the drain and source Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 24 Dynamic Power Dissipation • There are two components that add to dynamic power dissipation: 1) Capacitive load charging at a frequency f given by: PD = CV2DDf 2) The current that occurs during switching which can be seen in the figure Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 25 Power-Delay Product • The power-delay product is given as: PDP Pav P 2 Pav CVDD f 1 f T The figure shows a symmetrical inverter switching waveform 2tr 22 P T t r t a t f tb 5 P 0.8 0.8 2 2 CVDD CVDD PDP P 5 P 5 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 26 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 27 IrDA, Infrared Data Association Audio DAC (Digital to Analog Converter) Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 28 CMOS NOR Gate Basic CMOS logic gate structure CMOS NOR gate implementation Microelectronic Circuit Design, 4E McGraw-Hill Reference Inverter Chap 7 - 29 CMOS NOR Gate Transistor Sizing • When sizing the transistors, we attempt to keep the delay times the same as the reference inverter • To accomplish this, the on-resistance in the PMOS and NMOS branches of the NOR gate must be the same as the reference inverter • For a two-input NOR gate, the (W/L)p must be made twice as large Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 30 CMOS NOR Gate Body Effect • Since the bottom PMOS body contact is not connected to its source, its threshold voltage changes as VSB changes during switching • Once vO = VH is reached, the bottom PMOS is not affected by body effect, thus the total on-resistance of the PMOS branch is the same • However, the rise time is slowed down slightly due to |VTP| being a function of time Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 31 Two-Input NOR Gate Layout Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 32 Three-Input NOR Gate Layout • It is possible to extend this same design technique to create multiple input NOR gates Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 33 Shorthand Notation for NMOS and PMOS Transistors Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 34 CMOS NAND Gates CMOS NAND gate implementation Reference Inverter Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 35 CMOS NAND Gate Transistor Sizing • The same rules apply for sizing the NAND gate devices as for the NOR gate, except now the NMOS transistors are in series • (W/L)N will be twice the size of that of the reference inverter Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 36 Multi-Input CMOS NAND Gates Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 37 Complex CMOS Logic Gate Design Example – Euler path • Design a CMOS logic gate for (W/L)p,ref = 5/1 and for (W/L)n,ref = 2/1 that yields the function: Y = A + BC +BD • By inspection (knowing Y), the NMOS branch of the gate can drawn as the following with the corresponding graph, while considering the longest path for sizing purposes: Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 38 Complex CMOS Logic Gate Design Example • By placing nodes in the interior of each arc, plus two more outside the graph for VDD (3) and the complementary output (2’), the PMOS branch can be realized as shown on the left figure • Connect all of the nodes in the manner shown in the right figure, and the NMOS arc’s that the PMOS arc’s intersect have the same inputs Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 39 Complex CMOS Logic Gate Design Example • From the PMOS graph, the PMOS network can now be drawn for the final CMOS logic gate while once again considering the longest PMOS path for sizing Two equivalent forms of the final circuit Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 40 Complex CMOS Gate with a Bridging Transistor - Design Example • Design a CMOS gate that implements the following logic function using the same reference inverter sizes as the previous example: Y = AB +CE + ADE + CDB • The NMOS branch can be realized in the following manner using bridging NMOS D to implement Y. The corresponding NMOS graph is shown to the right. Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 41 Complex CMOS Gate with a Bridging Transistor - Design Example • By using the same technique as before, the PMOS graph can now be drawn Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 42 Complex CMOS Gate with a Bridging Transistor - Design Example • By using the PMOS graph, the PMOS network can now be realized as shown (considering the longest path for sizing) Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 43 Minimum Size Gate Design and Performance • With CMOS technology, there is an area/delay tradeoff that needs to be considered • If minimum feature sized are used for both devices, then the PLH will be increased compared to the symmetrical reference inverter Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 44 Minimum Size Complex Gate and Layout • The following shows the layout of a complex minimum size logic gate Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 45 Minimum Size Complex Gate and Layout Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 46 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 47 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 48 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 49 Dynamic Domino CMOS Logic • One technique to help decrease power in MOS logic circuits is dynamic logic • Dynamic logic uses different precharge and evaluation phases that are controlled by a system clock to eliminate the dc current path in single channel logic circuits • Early MOS logic required multiphase clocks to accomplish this, but CMOS logic can be operated dynamically with a single clock Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 50 Dynamic Domino CMOS Logic • The figure demonstrates the basic concept of domino CMOS logic operation Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 51 Simple Dynamic Domino Logic Circuit Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 52 Dynamic Domino CMOS Logic • It should be noted that domino CMOS circuits only produce true logic outputs, but this problem can be overcome by using registers that have both true and complemented outputs to complete the function shown by the following Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 53 Cascade Buffers • In some circuits, the logic must be able to drive large capacitances (10 to 50 pF) • By cascading a number of increasingly larger inverters, it is possible to drive the loads Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 54 Cascade Buffers • The taper factor determines the increase of the cascaded inverter’s size in manner shown of the previous image. CL Co N where Co is the unit inverter’s load capacitance • The delay of the cascaded buffer is given by the following: 1/ N CL B N Co o where o is the unit inverter’s propagation delay Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 55 Optimum Design of Cascaded Stages • The following expressions can aid in the design of an optimum cascaded buffer N opt CL ln Co 1 C ln L Co opt CL Co Bopt CL ln o Co Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 56 The CMOS Transmission Gate • The CMOS transmission gate (T-gate) is a useful circuits for both analog and digital applications • It acts as a switch that can operate up to VDD and down to VSS Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 57 The CMOS Transmission Gate • The main consideration that needs to be considered is the equivalent on-resistance which is given by the following expression: REQ Ronp Ronn Ronp Ronn Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 58 CMOS Latchup • There is one major downfall to the CMOS logic gate – Latchup • There are many safeguards that are done during fabrication to suppress this, but it can still occur under certain transient or fault conditions Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 59 CMOS Latchup • Latchup occurs due to parasitic bipolar transistors that exist in the basic inverter as shown below Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 60 CMOS Latchup • The configuration of these bipolar transistors creates a positive feedback loop, and will cause the logic gate to latchup as shown at the left • By using heavily doped material where Rn and Rp exist, their resistance will be lowered, thereby reducing the chance of latchup occurring Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 61 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 62 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 63 End of Chapter 7 Microelectronic Circuit Design, 4E McGraw-Hill Chap 7 - 64