* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Design of Low-Voltage CMOS Pipelined ADC`s using 1 pico

Phase-locked loop wikipedia , lookup

Electronic engineering wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Digital electronics wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Audio power wikipedia , lookup

Index of electronics articles wikipedia , lookup

Surge protector wikipedia , lookup

Schmitt trigger wikipedia , lookup

Television standards conversion wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Power MOSFET wikipedia , lookup

Radio transmitter design wikipedia , lookup

Integrating ADC wikipedia , lookup

Power electronics wikipedia , lookup

Operational amplifier wikipedia , lookup

Opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Valve RF amplifier wikipedia , lookup

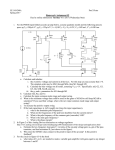

Design of Low-Voltage CMOS Pipelined ADC’s using 1 pico-Joule of Energy per Conversion B. Vaz1,2, N. Paulino1,2, J. Goes1,2, R. Costa1,2, R. Tavares1,2 and A. Steiger-Garção1,2 1 UNINOVA – CRI Campus da Faculdade de Ciências e Tecnologia 2825 – 114 Monte da Caparica – PORTUGAL E-mail: [email protected] Abstract - This paper presents an optimization methodology based on genetic algorithms for designing low-voltage low-power pipelined ADC’s. It is demonstrated that multi-bit rather than minimum resolution-per-stage architectures are better suited for low-voltage operation and also that, either switched-opamp or clock-boosting techniques can produce equivalent realizations in terms of power efficiency. By carefully tailoring the pipelined architecture with the proposed optimization approach it is clearly demonstrated by means of a 1.5V, 10b, 40 MS/s pipeline ADC design example that, reducing the supply voltage does not necessarily increases the used energy per conversion. 1. INTRODUCTION Power dissipation is becoming an increasingly important design issue in A/D interfaces for applications requiring portability. The need for monolithic ADCs in the resolution range of 8-12 bits with sampling rates higher than 20-100 MS/s for many battery-powered applications such as portable video cameras, IF digitization in digital radios and portable imaging devices is constantly increasing. On the other hand, there is a trend for the fast analog integration in deep sub-micron CMOS technologies due to the reduced cost through mixed-signal integration. The technology roadmap predicts a fast scaling-down of the transistor’s minimum channel lengths from 0.18µm in year 2000 up to 0.07µm in year 2010 accomplished with a reduction of the supply voltages from 1.8 to 0.6 Volt [1]. Hence, design cycles get shorter and shorter driven by market needs and by the continuously changing technologies. Thus, efficient optimization methodologies for low-voltage ADCs play an important rule when high-performances and low-power dissipations are simultaneously targeted. Moreover, several existing techniques to overcome the linearity of the switches should be taken into account in order to decide which leads to a minimum of used energy per conversion. The methodology addressed in this paper is quite general, since it is capable of exploring different lowvoltage techniques and different noise distributions while optimizes simultaneously several other design parameters, namely, the power dissipation, the resolution-per-stage and the DNL errors of the ADC. It is demonstrated in this paper that multi-bit rather than minimum resolution-per-stage architectures are better suited for low-voltage operation and also that either the switched-opamp (SO) or the clock-boosting (CB) technique can lead to equivalent realizations in terms of power efficiency. By carefully tailoring the pipelined architecture with the proposed optimization approach it is clearly demonstrated by means of a 1.5V, 10b, 40 MS/s CMOS pipeline ADC design example that, reducing the supply voltage does not necessarily increases the used energy per conversion. 0-7803-7448-7/02/$17.00 ©2002 IEEE I - 921 2 Faculdade de Ciências e Tecnologia Campus da Faculdade de Ciências e Tecnologia 2825 – 114 Caparica – PORTUGAL E-mail: [email protected] 2. ARCHITECTURE CONSIDERATIONS A – Architecture selection and low-voltage design issues A wide variety of pipelined A/D architectures have been described by several authors. Their main differences reside in the adopted quantization and residue characteristics in each stage, in the interstage gain factors and in the way the partial conversion results are combined to form the digital output word. It is out of the scope of this paper to address the tradeoffs of all these types of architectures. Rather, this paper will focus on an architecture used in practical implementations and which is easily amenable for general description. The extension of the design methodology to all the other architectures is straightforward. vin S/H MDAC FLASH N 1 bit Clk MDAC FLASH N i bit MDAC FLASH N NS-1 bit FLASH N NS bit N bit Out Synchronization and Digital Error Correction Logic Fig. 1: Generic N-bit, NS-stage pipeline ADC architecture. In the typical N-bit NS-stages pipelined A/D converter architecture considered here each stage employs a (flash) quantizer and an MDAC that performs also the inter-stage Sample-and-Hold (S/H) function [2], as shown in Fig. 1. Each stage processes the input signal in two phases. In the sampling phase, the MDAC samples the input signal and the quantizer does the A/D conversion. During the second phase, the MDAC generates and amplifies the residue yielding the input signal for the next stage. The successive stages operate, therefore, in opposite phases. In order to simplify the digital correction (by simply performing additions) and reduce the number of comparators both, the quantizer’s and the MDAC’s levels are assumed shifted up by 0.5 LSB of the stage resolution. Pipeline ADC architectures have been the subject of various conceptual studies for optimization of the resolution-per-stage and capacitor scaling, owing it to the large number of possible solutions to reach a specific target. For low resolutions up to 10-bit, it has been demonstrated in [3] that a topology resolving 1.5 bit-per-stage should be adopted to reduce power dissipation. However, multi-bit rather than minimum resolution-per-stage architectures are better suited for high-resolution pipelined ADCs. They result in lower power dissipation and area whilst minimizing stringent requirements of the constituting building blocks at the same time as conceptually pointed-out in [4] and also shown in practical 5 or 3 Volt CMOS realizations [5-7]. The current efficiency for a given performance can be estimated by the energy used per conversion as defined in [8] and given by ( E = P 2 ENOB ⋅ Fs ) (1) B.2) Clock-boost N-bit MDAC where P, Fs and ENOB represent, respectively, the measured values for the power dissipation, for the sampling-rate and for the effective-number-of-bits (related to the measured SNDR). Optimized designs [5-7] use only 1.8 – 4.4 pJ of energy per conversion. However, in low-voltage implementations additional issues have to be taken into account in order to achieve power-optimized designs. First, the loss of dynamic range due to the supply voltage reduction tightens the noise budget. On the other hand, new techniques at circuit level, such as, switched-opamp [9] or clock-boosting [10] have to be employed in order to overcome the linearity of the switches. As a consequence, the extra current consumption associated to the employed technique has to be considered and conclusions should be taken about the best approach to use. On the other hand, none of the previous published works optimizes the distribution of the noise contributions of the several pipelined stages to the total input referred noise. In fact, only capacitance’s scaling-down rules are devised. This is an issue harder to manage by the need of keeping the unit capacitances above a minimum for feasibility and matching (DNL) reasons. The methodology addressed in this paper is quite general, since it is capable of exploring different low-voltage techniques and different noise distributions while optimizes simultaneously several other design parameters, namely, the power dissipation, the stage-resolution and the DNL errors of the ADC. B – Practical realizations of the basic building-blocks B.1) Switched-opamp N-bit MDAC The switched-opamp technique consists on removing all problematic switches and realizing their function by switching-off the opamp. Fig. 2 shows a generic switched-opamp implementation of an N-bit MDAC. During the sampling-phase (φ1) the op-amp’s inputs are set to VSS assuming an op-amp with PMOS input transistors. At the same time, the op-amp’s outputs are in highimpedance (with the output-stage switched-off) and pulled up to VDD. The input differential voltage is sampled to the sampling ( Fig. 3 shows a generic clock-boost implementation of an N-bit MDAC. During the sampling-phase (φ1) both, the sampling capacitors CS(i) and the feedback capacitor CF, sample the differential input voltage. Next, during the residue amplification phase (φ2), CF form the feedback-loop of the op-amp while the bottom-plates of the sampling capacitors are connected either to Vrefn or Vrefp according to the thermometer-code obtained from the coarse quantization performed by the flash quantizer in the previous phase. In order to increase the power efficiency this block, it is assumed that the op-amp is switched-off in phase φ1. Fig. 3 – Clock-boost realization of an N-bit MDAC (half-circuit shown) B.3) Operational Amplifier The op-amp topology used in the pipelined stages is shown in Fig. 4. This two-stage amplifier consists of a folded-cascode first-stage followed by a common-source second-stage [10]. Cascode compensation was used to improve the bandwidth over conventional Miller compensation. This topology maximizes the output signal-swing which is of major importance in power optimized designs. ) capacitors CS and, the feedback capacitors CF and the 2 N − 2 capacitors C(i), are charged to VDD in order to shift the input common-mode voltage to VSS in the next phase. During the second phase (φ2), the residue obtained by subtracting the stored input voltage and the analog voltage returned from the D/A conversion (performed by capacitors C(i)) of the digital thermometer-code generated by the quantizer in the previous phase is amplified and held in the permanently connected feedback capacitors CF. Fig. 4 – Two-stage cascode-compensated op-amp. B.4) N-bit Flash quantizer ( ) The N-bit flash quantizer consists of a bank of 2 N − 2 comparators followed by a bubble suppressor and by a thermometer-to-binary digital encoder. Typically, in low-voltage designs, each comparator comprises an input switched-capacitor (SC) divider network to define the threshold level and to adjust the input common-mode level followed by a pre-amp and then by a dynamic positive-feedback latch. In this optimization methodology, a fully dynamic class-AB comparator as the one proposed in [10] was chosen, in order to reduce the static current consumption. 3. DESIGN METHODOLOGY FOR OPTIMIZATION The architecture of the tool employed for assisting the optimization methodology is presented in Fig. 5. It basically comprises a general-purpose kernel based on genetic algorithms as reported in Fig. 2 – Switched-opamp realization of an N-bit MDAC (half-circuit shown) I - 922 [10-11]. Two text files should be provided to the application: one contains the structure of the chromosome and another the desired parameters that are envisaged. The chromosome, x , consists of one or more genes. Basically, the genes are the variables, xi, that the algorithm will found that best fit the desired goals. One of the most important blocks of this architecture is the Dynamic-Linked amplifier, the feedback factor, the parasitic capacitance at the inputs of the amplifier and its compensation capacitor. The term within {} only exists in the switched-opamp implementation leading to larger unit capacitance values. B – Power dissipation The power estimation of a pipelined ADC can be as Library (DLL) that contains the fitness function, f (x ) . PTOTAL = NS −1 NS i =0 i =1 ∑ PMDAC(i) + ∑ PFLASH (i) + PDCL + (5) PSYNC + PCLOCKGEN + {PCLOCKBS } where PMDAC (i ) , PFLASH (i ) , PDCL , PSYNC , PCLOCKGEN and PCLOCKBS are, respectively, the power of MDAC(i), of flash-quantizer(i), of the digital correction logic, of the sincronization logic, of the clock generator and of the clock-boosters. As obvious, term within {} is only used in the clock-boost implementation. The power dissipated in each MDAC is the sum of a static power dissipated by the opamp with a dynamic contribution corresponding to switching of the capacitors at the sampling frequency FS, according to PMDAC (i ) ≈ K OTA ⋅ I bias ⋅ V DD + Fig. 5 – Optimizer’s architecture. This file has all the mathematical functions that model the circuit behavior and it is dynamically linked with the kernel. The fitness function used to optimize the ADC was defined as f ( x ) ≈ (1 − e noise _ desired − noise _ achieved ⋅ (1 − e ) ⋅ (1 − e PowerDiss _ desir . − PowerDiss _ achiev. DNL _ desired − DNL _ achieved )⋅ (2) ) In order to calculate the value of the ADC fitness it is necessary to devise expressions for the input-referred noise, for the overall power dissipation and for the maximum expected DNL error. 2 ⋅ FS 2 ⋅ CTOT i ⋅ (1 + BPPC ) ⋅ Vref (6) where K OTA , I bias , I out , CTOTi , BPPC , V ref represent, respectively, the number of current branches of the op-amp’s first-stage, the bias current of this stage, the current in the output-stage, the overall loading capacitance, the percentage of bottom-plate parasitic capacitance and the reference voltage. For a specific loading condition, there are minimum values for Ibias and Iout, which are able to guarantee that the output voltage of the MDAC(i) settles with the required accuracy in the available time-slot. For the N-bit flash quantizers a similar expression can be devised, yielding ( ) PFLASH (i ) = 2 N − 2 ⋅ A – Noise The mean-squared value of the total thermal noise referred to the 2 input of the converter, v ni , is given by Vni2 2 ⋅ I out ⋅ V DD + 2 = NS −1 V 2 , no MDAC i i i =0 Gn2 n =1 ∑ ∏ ) (7) where I comp , Ccomp , Klatch represent, respectively, the bias current C ∧ Gn = S CF (3) 2 where vno , MDACi represents the output-referred mean squared noise contribution of MDACi, and Gn represents the closed-loop gain of MDACi during residue amplification (for simplicity reasons, the input S/H is regarded here as MDAC0). The computation of the squared noise contributions should take into account the noise from the switches and the noise from the amplifier in the form kT 2 Vno , MDACi = 2 ⋅ CF ( I comp ⋅ VDD 2 + 2 N +1 ⋅ Ccomp ⋅ Vref + (N − 1)Klatch ⋅ FS 2 ( ) N 1 + C S + Cip + 2 − 2 × Cu CF CF 2 kT ⋅ γ (4) + 3β ⋅ Cc where k , T , γ , β , C ip , C c , represents respectively the Boltzmann’s constant, the absolute temperature, the excess noise factor of the I - 923 of the pre-amp, the sum of the capacitance values of the input SC network and the dynamic energy per conversion of the output latch. The power dissipated by the synchronization logic, by the digital correction logic and by the clock generator follows a proportional rule defined as Pdigital ∝ NGATE ⋅ KGATE ⋅ FS (8) where N GATE , K GATE are, respectively, the number of gates of the digital cell and the energy used per clock cycle as a function of the switching activity, i.e., related with the probability of the gate’s output to make a logic transition during one clock cycle. When clock-boosting is employed a similar expression can be devised. The main difference resides on the fact that the dynamic power becomes also proportional to the sum of the capacitance values connected to the switches driven by the clock-boosting circuits. C – Differential Non-Linearity errors (DNL) It can be demonstrated that the maximum DNL error expected in a pipelined ADC can be expressed for a yield estimation of 99.7 % by expression (9). AC , N , C u (i ) , C POX represent, respectively, a technology parameter (a standard deviation in % ⋅ µm ), the resolution of the ADC, the unit capacitance value of MDACi and the dielectric capacitance per unit area (in fF / µm 2 ). It can be observed that the DNL characteristic improves twice for each additional bit in the resolution of the front-end stage. Max( DNL) = 3 ⋅ AC NS −1 ∑( i =1 2 Cu (i ) −2 ⋅ 2N CPOX Ni ⋅ 1 i ∏ Gn (9) )2 n =1 4. OPTIMIZATION EXAMPLE AND RESULTS The optimization of a 1.5-Volt, 10-bit, 40 MS/s CMOS pipeline ADC was made for the both realizations (switched-opamp and clock-boost) and for a standard 0.35µm double-poly CMOS technology. The desired specifications for both techniques were, respectively, for the input-referred squared-noise, for the power dissipation and for the maximum DNL error, 79.5 nV2 (quantization noise below the 11-bit level), 29 mW and 0.5 LSB. With these specs, it is expected to reach an ENOB of about 9.5 bits with only 1pJ of used energy per conversion. The chromosome was defined by the unit capacitance values for each MDAC, Cu(i), the resolution of each stage, Ni, and the by the compensation capacitance for each op-amp in each MDAC, Cc(i). For practical reasons, the minimum value for all capacitances was limited to 50 fF. The optimization run for 120 generations (less than 1min. in a Pentium-III) and both realizations reached the desired specifications. Table 1 summarises the output final results (obtained using the best chromosome). Firstly, it can be observed that a 2.5-b resolution-per-stage was considered better than the usually adopted resolution of 1.5-b. On the other hand, it can also be observed that switched-opamp implementation lead to larger unit capacitance values in the MDACs than the clock-boost one as expected. This obviously increases the current consumption of the MDACs. However, the clock-boost implementation has an additional dynamic power contribution from the clock-boosting circuitry which is directly related with the values of Cu(i). Fig. 6 shows the power distribution (in %) of the basic building blocks for both low-voltage methods. As it can be observed, about 20% of the overall power dissipation (~29 mW) is dissipated by the clockboosting circuitry. Moreover, the occupied die area by these circuits can not be neglected at all. Table 1: Output results of the tool for both, SO and CB methods. SO # Stage of bits S/H --1rs 2.5 2nd 2.5 3rd 2.5 4th 2.5 5th 2 Cu (fF) 633 308 50 50 50 --- Opamp Itot Cc (mA) (fF) 3.3 2523 5.6 761 3.9 389 2.8 360 1.0 176 --- --- CB Av (dB) 66 73 61 49 37 --- # of bits --2.5 2.5 2.5 2.5 2 Cu (fF) 437 276 50 50 50 --- Opamp Itot Cc (mA) (fF) 2.8 1596 3.8 590 2.8 479 2.0 473 0.7 235 --- --- Av (dB) 66 73 61 49 37 --- I - 924 Fig. 6 – Power distribution for both implementations. 5. CONCLUSIONS This paper presented an optimization methodology based on genetic algorithms for designing low-voltage low-power pipelined ADC’s. It was demonstrated that multi-bit rather than minimum resolution-per-stage architectures are better suited for low-voltage operation and also that, either switched-opamp or clock-boosting techniques can produce equivalent realizations in terms of power efficiency. By carefully tailoring the pipelined architecture with the proposed optimization approach it was clearly demonstrated that reducing the supply voltage does not necessarily increases the used energy per conversion. Acknowledgments The research work that led to this implementation was partially supported by the Portuguese Foundation for Science and Technology under ADOPT (PCTI/1999/ESE/33311) Project. REFERENCES [1] International Technology Roadmap for Semiconductors, Semiconductor Industry Association, 1999. [2] Bang-S. Song, Seung-H. Lee, Michael F. Tompsett, "A 10-b 15-MHz CMOS Recycling Two-Step A/D Converter", IEEE J. Solid-State Circuits, Vol. 25, No. 6, pp. 1328-1338, Dec. 1990. [3] S. H. Lewis, "Optimizing the Stage Resolution in Pipelined, Multistage, Analog-to-Digital Converters for Video-Rate Applications", IEEE Trans. Circuits and Systems – II, vol. 39, No. 8, pp. 516-523, August 1992. [4] João Goes, et. al., "Systematic Design for Optimization of High-Speed Pipelined A/D Converters using Self-Calibration", IEEE Trans. Circuits and Systems – II, pp. 1513-1526, Dec. 1998. [5] D. Cline, P. Gray, "A Power Optimized 13-b 5 Msamples/s Pipelined Analog-to-Digital Converter in 1.2 µm CMOS", IEEE J. Solid-State Circuits, Vol.31, No. 3, pp. 294-302, Mar 1996. [6] Sung-U. Kwak, Bang-Sup Song and Kantilal Bracania, “A 15b 5Msample/s Low-Spurious CMOS ADC”, Proc. IEEE ISSCC’97, pp. 146147, Feb.1997. [7] L. Singer, T. Brooks, “A 14-bit 10 MHz Calibration-Free CMOS pipelined A/D Converter”, Proc. IEEE VLSI’96, pp. 94-95, 1996. [8] FranK Goodenough, “Analog Technology of All Varieties Dominate ISSCC”, Electr. Design, No. 19, pp. 96-111, Feb. 1996. [9] Mikko Waltari, Kari Halonen, “1.0-Volt, 9-bit Pipelined CMOS ADC”, IEEE 26rd European Solid-State Circuits Conference, pp. 359-363, Stockholm, Sweden, September 2000. [10] Andrew M. Abo and Paul R. Gray, “A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter”, IEEE Journal of Solid-State Circuits, Vol. 34, no. 5, May 1999. [10] N. Paulino, J. Goes and A. S.-Garção, “Design Methodology for Optimisation of Analogue Building-Blocks using Genetic Algorithms”, IEEE ISCAS’2001, vol. 5, pp. 435-438, Sydney, Australia, May 2001. [11] B. Vaz, R. Costa, N. Paulino, J. Goes, R. Tavares and A. S.-Garção, “A General-purpose Kernel based on Genetic Algorithms for Optimization of Complex Analog Circuits”, Proc. IEEE MWSCAS’2001, pp. 83-86, Dayton, Ohio, USA, August 2001.