* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download A 0.8V 5.9GHz WIDE TUNING RANGE CMOS VCO USING

Pulse-width modulation wikipedia , lookup

Utility frequency wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Chirp spectrum wikipedia , lookup

Current source wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Electrical ballast wikipedia , lookup

Power electronics wikipedia , lookup

Surge protector wikipedia , lookup

Voltage regulator wikipedia , lookup

Opto-isolator wikipedia , lookup

Three-phase electric power wikipedia , lookup

Stray voltage wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Alternating current wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Rectiverter wikipedia , lookup

Buck converter wikipedia , lookup

Voltage optimisation wikipedia , lookup

A 0.8V 5.9GHz WIDE TUNING RANGE CMOS VCO USING

INVERSION-MODE BANDSWITCHING VARACTORS

Chung-Yu Wu, Fellow, IEEE

Chi-Yao Yu

Department of Electronics Engineering and Institute of

Electronic

National Chiao Tung University

Hsinchu, Republic of China

Department of Electronics Engineering and Institute of

Electronic

National Chiao Tung University

Hsinchu, Republic of China

Abstract—This paper presents a completely integrated 0.8V

5.9GHz CMOS voltage-controlled oscillator (VCO) with

inversion-mode MOS (IMOS) bandswitching varactors. IMOS

varactors are used to maintain a large tuning range when the

supply voltage is lower than 1V. Moreover, a large resistance

connects to the bulk of each IMOS varactor to further improve

the VCO tuning capability. Through this large resistance, the

tuning range increases by 500MHz. A bandswitching topology

is used to ameliorate the adverse effects of highly sensitive

IMOS varactors. The VCO was simulated with a 0.8V supply

with a tuning range of 29.12% from 4.4 to 5.9 GHz when tuned

from 0 to 0.8V. The simulated phase noise is -109.65dBc/Hz at

1MHz offset from the carrier frequency of 5.52GHz. The

VCO-core power dissipation is 1.2mW. When the supply is

reduced to 0.6V, the tuning range becomes 22.64% from 4.7 to

5.9GHz. The VCO-core dissipates 0.9mW, and the phase noise

is -105.24dBc/Hz at 1MHz offset from the carrier frequency of

5.65GHz. The VCO circuit has been designed using TSMC

0.18-µm CMOS technology with deep n-well processing.

I.

supply voltage is 0.8V, the tuning range of the VCO is

29.12% from 4.4 to 5.9GHz and the phase noise is 109.65dBc/Hz at 1MHz offset from the carrier at 5.52GHz.

The VCO core dissipates 1.2mW of power. When the supply

voltage is reduced to 0.6V, the tuning range of the VCO

becomes 22.64% from 4.7 to 5.9GHz and the phase noise is 105.24dBc/Hz at 1MHz offset from the carrier at 5.65GHz.

In this case, the VCO core consumes only 0.9mW. The VCO

was implemented in TSMC 0.18-µm CMOS technology with

deep n-well processing.

This paper is organized as follows. Section II describes

the passive elements in the VCO circuit. Next, the IMOS

varactors are introduced. Next, the bandswitching topology

is introduced. Finally, the integrated spiral inductor model

used in simulation is described. Section III describes the

design of the proposed VCO. Section IV presents the

simulation results. Finally, the conclusion is drawn in

Section V.

INTRODUCTION

Due to the large parasitic capacitance of bulk CMOS

technology, integrated LC oscillators suffer from a small

frequency tuning range. This problem is even worse when

the supply voltage is lowered due to technology scaling.

Accumulation MOS (AMOS) varactors have been a popular

choice when the tuning voltage is larger than 1V [1]-[4].

However, when the tuning voltage is lower than 1V, the

accumulation MOS (AMOS) varactors cannot achieve their

physical maximum and minimum capacitance. This will

degrade the VCO tuning capability considerably.

To maintain a fine VCO tuning range in the case of low

supply voltages, IMOS varactors are used in this VCO

design because of their natural abrupt gradient of the C-V

curve (capacitance relative to tuning voltage curve). To

improve the tuning capability further, a large resistance

connects to the bulk of each IMOS varactor to isolate the

gate to bulk parasitic capacitance of IMOS from the

oscillatory output port. The simulation results show that

using the new modified IMOS structure, the effective

minimal capacitance (Cmin) is reduced from 775 to 590fF and

the frequency tuning range increases by 500MHz. When the

II.

THE PASSIVES

A.

Inversion-mode MOS Varactors

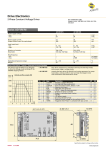

Figure 1 shows the circuit schematic and equivalent

models of the IMOS varactors used in the VCO design. A

large poly resistance Rs connects the bulk of the NMOS and

the ac ground terminal Vbias. When the terminal DS in Figure

1(a) is biased at the positive end voltage, the IMOS is

operated in the depletion mode and Figure 1(b) shows the

equivalent model. The value of Cparasitic is dominated by the

gate-source and gate-drain overlap capacitance; Cox is the

gate-oxide capacitance and Cdep is the depletion capacitance.

The conductance looking into terminal G in Figure 1(b) is

G dep =

jω (C ox || C d )G s

+ jωC parasitic

jω (C ox || C d ) + G s

(1)

where Gs is the inverse of the resistance of Rs. If Gs is much

smaller than ω(Cox||Cd) and ωCparasitic across the entire

frequency tuning range, then Gdep is approximately equal to

jωCparasitic and the minimum capacitance Cmin can be

estimated by Cparasitic. However, if the bulk is connected

DS (Drain and Source)

Cparasitic

DS

G

Cox

Cdep

Rs

Cparasitic+Cox

1.37p

bulk connects to

ground

Vbias

G

(Gate)

(b)

Capacitance (F)

Cparasitic

DS

Rs = 10k ohm

G

Vbias

Rch/12

Cdep

Rs

Vbias

Cox

(a)

(c)

bulk connects

to Rs

Cparasitic+Cox||Cdep

775f

Figure 1. (a) Circuit schematic of an IMOS varactor with a large bulk

resistor Rs (b) The equivalent model in depletion mode (c) The

equivalent model in inversion mode

185f (Cox||Cdep)

Cparasitic

590f

Vc

220m

Voltage of DS terminal (volt)

0

Rch ≈ L

(

k nW V gs − Vtn

),

(2)

where W and L are the width and length of the MOS

transistor, kn is the gain factor for NMOS transistors, Vgs is

the voltage difference between G and DS, and Vtn is the

threshold voltage of the NMOS transistor. To simplify,

assuming Rs goes to infinite, the conductance looking into

terminal G in Figure 1(c) is

Ginv =

12 jωC ox G ch

+ jωC parasitic

jωC ox + 12G ch

(3)

where Gch is the inverse of the resistance of Rch. From (2),

the ratio of 12Gch/ωCox is larger than 20 at the carrier

frequency from 4 to 6GHz when L is 0.36µm. Thus, the

imaginary part of Ginv is approximately equal to

ω(Cox+Cparasitic) and the maximum capacitance Cmax can be

estimated by Cox+Cparasitic.

The HSPICE simulated C-V characteristics of an IMOS

varactor are shown in Figure 2. The resistance of Rs is set to

10k in this simulation. The voltage of terminal G in figure 1

is set to a fixed voltage, 0.8V, and the voltage of DS is swept

from 0 to 0.8V. The improvement of the Cmax/Cmin ratio using

the modified varactor of Figure 1(a) is close to 25%. It

should be noted that the center voltage Vc in Figure 2 can be

right-shifted by increasing the bulk biased voltage, Vbias in

Figure 1. In the proposed VCO design, Vbias is biased at 0.4V.

B. Bandswitching Varactors

Large varactor sensitivity kv degrades of phase noise

performance L(∆f , k v ) . The effect of kv on phase noise can

be shown by the following equation [1],

800m

Figure 2. C-V curves of IMOS varactors

1.19p

Capacitance (F)

directly to the ac ground (case of infinite Gs), Cmin will

become Cparasitic+Cox||Cdep. Thus, Cmin can be decreased by

Cox||Cdep by using a large resistance Rs in Figure 1(a). When

DS is biased at the negative end, a sheet of electrons

accumulates at the surface of the channel and the IMOS is

operated in the inversion mode. Figure 1(c) shows the

equivalent model. Rch is the channel resistance, which can be

estimated by following equation [5],

535f

-1.8

0.8

0

Voltage of AMOS bulk terminal (volt)

1.8

Figure 3. C-V curves of AMOS varactors

f

L(∆f , k v ) = 10 log o

2Q∆f

2

f

FkT

1 + c

2Po ∆f

k v vn

+

2k CL ∆f

2

, (4)

where fo is the carrier frequency, Q is the quality factor,

∆f is the offset frequency from the carrier, F is the noise

factor of the gain element, k is Boltzmann’s constant, T is the

flicker noise corner frequency, and kCL is a function of C and

L in the resonator. If the required tuning range is large, a

bandswitching topology is suggested to reduce varactor

sensitivity kv [1]. However, Figure 3 shows the C-V

characteristics of an AMOS varactor with the same size and

bias condition as the IMOS varactor simulated in Figure 2.

AMOS cannot be fully switched when tuned from 0 to 0.8V.

Thus, there is no benefit to implement bandswitching

topology with AMOS varactors to reduce kv with low tuning

voltage. On the other hand, from Figure 2, the gradient of

the IMOS C-V curve is relatively small when the voltage of

DS is 0 or 0.8V. This means that kv is also relatively small at

0 and 0.8V. It makes sense using IMOS as on/off only

varactors in a bandswitching topology to improve phase

noise performance with low supply voltages.

Ct

Ls1

Rs1

p3

Cox1

Csub1

Rs2

Rsub3

p2

Rsub2

Csub2

500MHz

5.6

Cox2

Cox3

Rsub1 Csub3

5.8

Ls2

Frequency (GHz)

p1

bulk connects to Rs

bulk connects to ground

6.0

Figure 4. Layout and equivalent model of spiral inductor

5.4

5.2

5.0

4.8

4.6

4.4

VDD

Vo+

4Cv/3

4.2

4Cv/3

0.2

0.4

0.6

0.8

Tuned Voltage (volt)

Vo-

Figure 6. Tuning range of VCO without bandswitching

Cv

Vc2

Cv

Cv

Vc3

Cv

Idc

Figure 5. VCO schematic

C. Spiral Inuctor

Figure 4 is the layout and equivalent model of the spiral

inductor. The spiral inductor is implanted using the thick top

metal and the inner radius is 80µm. A symmetrical

architecture with center tapping is used to save chip area.

ADS Momentum is used for simulation. The two-turn

inductor provides 1.55nH of inductance, and the quality

factor is from 9.5 to 11 across the entire tuning range.

VCO DESIGN

The VCO was designed in TSMC 0.18µm CMOS

technology. Figure 5 shows the circuit schematic for the

VCO. It is an LC cross-coupled VCO with nMOS latch to

generate negative resistance. The current source Idc draws

1.5mA. The bandswitching IMOS varactor array consists of

one continuous tuning varactor controlled by tuning voltage

Vc1 and two on/off only digital switching varactors

controlled by Vc2 and Vc3. Gate terminals (G in Figure 1) of

each IMOS connect to the oscillatory outputs (Vo+ and Vo- in

Figure 5) and the drain and source terminals (DS in Figure 1)

connects to the tuning ports (Vc1 to Vc3 in Figure 5). The C-V

curve of the three varactors on each side was shown in

Figure 2.

Frequency (GHz)

Vc1

III.

0.0

Vc2 = Vc3 = 0V

Vc2 = 0.8V Vc3 =0V

Vc2 = Vc3 = 0.8V

5.9

5.8

5.7

5.6

5.5

5.4

5.3

5.2

5.1

5.0

4.9

4.8

4.7

4.6

4.5

4.4

0.0

0.2

0.4

0.6

0.8

Tuned voltage Vc1 (volt)

Figure 7. Tuning range of bandswitching VCO

IV.

SIMULATION RESULTS

The VCO circuit in Figure 5 is simulated with a 0.8V

supply. Figure 6 shows the tuning characteristics of the VCO

when Vc1, Vc2 and Vc3 are connected together and tuned from

0 to 0.8V. From the simulation results shown in Figure 6, the

frequency tuning range can be improved by 500MHz (50%,

from 1 to 1.5GHz) through the large resistance Rs connected

to the IMOS bulk. Figure 7 shows the tuning range of the

VCO with the bandswitching IMOS varactor array

mentioned before. The carrier frequency can be tuned

between 4.4 to 5.9GHz, achieving 29.12% tuning range with

the center frequency at 5.15GHz. Figure 8 shows the phase

noise simulation result when the VCO operates at a carrier

frequency 5.52GHz. It has -88.01dBc/Hz at 100KHz offset

and -109.65dBc/Hz at 1MHz offset. The phase noise is

simulated when Vc1 is 0.3V and Vc2 and Vc3 are 0.8V. When

the supply voltage is reduced to 0.6V, the tuning range

becomes 22.64% from 4.7 to 5.9GHz. The phase noise is

81.52dBc/Hz at 100KHz offset and -105.24dBc/Hz at 1MHz

offset from the carrier at 5.65GHz.

TABLE I.

VCO PERFORMANCE SUMMARY

Process

Supply voltage

0.8V

0.6V

Frequency

4.4 – 5.9GHz

4.7 – 5.9GHz

Tuning range

29.12%

22.64%

Power dissipation

1.2mW

0.9mW

Phase Noise @ 100k

-88.01dBc/Hz

-81.52dBc/Hz

Phase Noise @ 1M

-109.65dBc/Hz

-105.24dBc/Hz

FOM

-184dBc/Hz

-180.9dBc/Hz

TABLE II.

Figure 8. Phase noise simulation results

A widely used figure of merit (FOM) to make

comparisons between different VCOs is defined as

f

FOM = L{∆f } − 20 log o

∆f

P

+ 10 log

1mW

(5)

where L{∆f } is the phase noise at ∆f offset from the carrier

at f o and P is the power dissipation of the VCO-core. The

FOM is this design is -183.65dBc/Hz at 5.52GHz at a 0.8V

supply voltage. When the supply voltage is reduced to 0.6V,

the FOM becomes -180.74dBc/Hz at 5.65GHz.

Table 1 summarizes the performance of the proposed

VCO while Table 2 provides a comparison with some

recently published VCOs. It can be seen that the proposed

VCO has good tuning capability even if the tuned voltage is

lower than 1V.

V.

fo

[GHz]

Tuning

Range

VDD

[V]

P

[mW]

L{1MHx}

[dBc/Hz]

[dBc/Hz]

Technology,

Var. type

[1]

3.065

5.612

58.7%

(1.4V)

1V

3.0

2.0

-120.8

@3.065G

-185.6

-186.6

0.13µm SOI

CMOS, AMOS

[3]

4.2

5.05

18%

(2.5V)

2.5V

13.8

-114

@5G

-176.6

0.25µm CMOS,

AMOS

[6]

5.87

4.73

21.5%

(4V)

2V

4

-106

@5G

-173.96

0.25µm CMOS

[7]

1.8

2.45

26.5%

(4V)

2V

2

-125

@1.9G

-187.6

0.35 µm CMOS,

AMOS

[8]

5.51

6.53

16.8%

(1.5V)

1.5V

18

-98.4

@6.29G

-161.82

0.35 µm CMOS,

No Var.

4.4

5.9

29.12%

(0.8V)

0.8V

1.2

-109.65

@5.52G

-183.65

4.7

5.9

22.64%

(0.6V)

0.18 µm CMOS,

IMOS

0.9

-105.24

@5.65G

-180.74

(simulation result)

This

work

0.6V

FOM

REFERENCES

[1]

CONCLUSION

[3]

[4]

[5]

[6]

ACKNOWLEDGEMENT

C. Y. Yu would like to thank M. P. Houlgate, T. W. Yu,

C. Y. Chou, S. Wang, and H. Y. Su for their advice and

thank National Chip Implementation Center (CIC) for

technical support.

VCO PERFOMANCE COMPARISON

Ref.

[2]

A 0.8V 5.9GHz fully-integrated cross-coupled LC VCO

is presented. IMOS varactors with large bulk resistance are

used to achieve 29.12% frequency tuning range. To correct

for the adverse effects of IMOS varactors caused by high

sensitivity, the bandswitching topology is used. When the

supply voltage is reduced to 0.6V, the proposed VCO still

has 22.64% frequency tuning range. Therefore, the proposed

IMOS varactors provide a solution to maintain the VCO

frequency tuning capability when the supply voltage is lower

than 1V.

TSMC 0.18µm CMOS

[7]

[8]

Neric H. W. Fong, J. O. Plouchart, N. Zamdmer, D. Liu, Lawrence F.

Wagner, C. Plett, and N. G. Tarr, “Design of Wind-Band CMOS

VCO for Multiband Wirless LAN Application,” IEEE Journal of

Solid-State Circuit, vol. 38, pp. 1333-1342, Aug. 2003.

P. Andreani and S. Mattisson, “On the Use of MOS Varactors in RF

VCO’s,” IEEE Journal of Solid-State Circuit, vol. 35, pp. 905-910,

Jun. 2000.

C. Samori, S. Levantino, and V. Boccuzzi, “A -94 dBc/Hz@100kHz,

fully-integrated, 5 GHz, CMOS VCO with 18% tuning range for

Bluetooth application,” in Proc. IEEE Custom Integrated Circuits

Conf., pp. 201-204, 2001.

J. Maget, M. Tiebout, and R. Kraus, “Influence of novel MOS

varactors on performance of a fully-integrated UMTS VCO in

standard 0.25-µm CMOS technology,” IEEE Journal of Solid-State

Circuit, vol. 35, pp. 1360-1367, Sept. 2001.

P. Andreani and S. Mattisson, “A 2.4-GHz CMOS Monolithic VCO

based on an MOS Varactor,” In Proc. ISCAS’ 99, pp. 557-560, MayJune 1999.

B. Jung and R. Harjani, “A Wide Tuning Range VCO Using

Capacitive Source Degeneration,” In Proc. ISCAS’ 04, pp. 145-148,

2004.

F. Svelto, S. Deantoni and R. Castello, “A 1mA, -120.5 dbc/Hz at 600

kHz from 1.9GHz fully tunable LC CMOS VCO,” in Proc. IEEE

Custom Integrated Circuit Conf., pp. 577-580 , 2000.

T. P. Liu, “A 6.5GHz Monolithic CMOS Voltage-Controlled

Oscillator,” in IEEE Int. Solid-State Circuit Conf. Dig. Tech. Papers,

pp. 404-405, Feb. 1999.