* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Analog-Digital Conversion

Power inverter wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Alternating current wikipedia , lookup

Current source wikipedia , lookup

Control system wikipedia , lookup

Stray voltage wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Voltage optimisation wikipedia , lookup

Mains electricity wikipedia , lookup

Power electronics wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Oscilloscope history wikipedia , lookup

Voltage regulator wikipedia , lookup

Buck converter wikipedia , lookup

Schmitt trigger wikipedia , lookup

Integrating ADC wikipedia , lookup

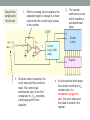

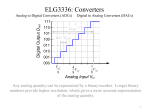

Switched-mode power supply wikipedia , lookup

Analog-Digital Conversion • Other types of ADC i. • • • • Dual Slope ADCs use a capacitor connected to a reference voltage. the capacitor voltage starts at zero and is charged for a set time by the output voltage of a sample-and-hold circuit. the capacitor is then switched to a known negative voltage reference, and charged in the opposite direction until it reaches zero volts again. this second charge is timed with a digital counter. The final count is proportional to the input voltage. Advantages: This technique is very precise and can produce ADCs with high resolution Disadvantages: very slow and generally more expensive than successive approximation ADCs. Output from sample and hold circuit 1. When an analog value is applied, the capacitor begins to charge in a linear manner and the control logic passes to the counter 2. The counter continues to count until is reaches a pre-determined value. VO1 1 Control Logic, (AND Gate) Register 3. Once the value is reached, the count stops and the counter is reset. The control logic switches the input to the first comparator to –Vref, providing a discharge path for the capacitor. 4. As the capacitor discharges the counter counts and VO1 reaches zero, the comparator o/p goes to zero, the count stops and the value is stored in the register t t1 -VO1 1. Fixed time, variable slope during charging 2. Variable time, fixed slope during discharging DUAL SLOPE • The resolution of a n-bit analog-to-digital Converter (ADC) is a function of how many parts the maximum signal can be divided into. The formula to calculate resolution is 2n. For example, a 12 bit ADC has a resolution of 212 = 4,096 Digital Signal Conditioning • In many DSP applications, we must reconstruct an analog signal after the digital processing stage. This is done using a digital-to-analog converter (DAC), which is considerably less expensive than the ADC. Reference Voltage Digital Value DAC Analog Voltage • Types of DAC Voltage Source Multiplying DAC or Binary Weighted Input DAC This method use a reference voltage which is switched in or out by the digital data. i. The converter is so-named because it multiplies a certain gain value with a source voltage (Vcc or sometime referred to as the reference voltage) • Let’s consider a 2 bit example MSB LSB Digital Analog 00 01 0V 0.5Vcc 10 Vcc 11 1.5Vcc EXAMPLE Take VR = 10 V Calculate the value of Vout for the digital input of 1001 if R = 10 kΩ and Rf = 5 kΩ Vout = -5.625 V ii. R/2R DAC • A disadvantage of the former DAC design was its requirement of several different precise input resistor values: one unique value per binary input bit. • Manufacture may be simplified if there are fewer different resistor values to purchase, stock, and sort prior to assembly. • By constructing a different kind of resistor network on the input of our summing circuit, we can achieve the same kind of binary weighting with only two kinds of resistor values, and with only a modest increase in resistor count. This “ladder” network looks like this: 3 bit R/2R DAC Iin I2 I1 I0 ITOTAL In order to calculate Iin, must calculate Req3 • Req3 = R • Iin = Vref / Req3 = Vref / R • I2 = Vref / 2R • I1 = Vref / 4R • I0 = Vref / 8R R= 15 kΩ 2R = 30 kΩ RF = 15 kΩ • Req3 = R = 15 kΩ • Iin = Vref / Req3 = Vref / R = 5/15 = 0.333 mA • I2 = Vref / 2R = 5 / 30 = 0.1667 mA • I1 = Vref / 4R = 5 / 60 = 0.0833 mA • I0 = Vref / 8R = 5 / 120 = 0.04167 mA IT = 0.25 mA Vo = - IT x Rf = -3.75 V Example: 4 bits R/2R DAC • Input = (0101)2 B3 B2 B1 B0 0 1 0 1 • VREF = 10 V • R = 2 kΩ • Rf = 4 kΩ • Req4 = R = 2 kΩ • Iin = Vref / Req4 = Vref / R = 10/2 = 5 mA • I3 = Vref / 2R = 10 / 4 = 2.5 mA • I2 = Vref / 4R = 10 / 8 = 1.25 mA • I1 = Vref / 8R = 10 / 16 = 0.625 mA • I0 = Vref / 16R = 10 / 32 = 0.3125 mA IT =1.5625 mA Vo = - IT x Rf = - 6.25 V • Smoothing out the output of DAC • The output of a DAC is stepped, just like the analog waveforms that were sampled and held. • The stepped or staircase effect is a distortion, and it may be desirable to reduce this effect. • Hence, at the end a low pass smoothing filter is used. This filter is referred to as a reconstruction filter. An example of a reconstruction filter is the Sallen-Key filter circuit configuration 𝑓𝑐 = • Performance Specifications Resolution ii. Settling Time iii. Linearity i. 1 2𝜋 𝑅1𝐶1𝑅2𝐶2 RESOLUTION Better Resolution(3 bit) Poor Resolution(1 bit) Vout Vout Desired Analog signal Desired Analog signal 111 110 2 V Levels 8 V Levels 1 101 100 011 010 001 0 Approximate output 0 Digital Input 110 101 100 011 010 001 000 000 Approximate output Digital Input 18 SETTLING TIME • Settling Time: The time required for the input signal voltage to settle to the expected output voltage(within +/- VLSB). • Any change in the input state will not be reflected in the output state immediately. There is a time lag, between the two events. LINEARITY • Linearity: is the difference between the desired analog output and the actual output over the full range of expected values. • Ideally, a DAC should produce a linear relationship between a digital input and the analog output, this is not always the case. 20 NON-Linearity(Real World) Desired/Approximate Output Analog Output Voltage Analog Output Voltage Linearity(Ideal Case) Desired Output Approximate output Digital Input Perfect Agreement Digital Input Miss-alignment