* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Lab 7

Electrical substation wikipedia , lookup

Electromagnetic compatibility wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Alternating current wikipedia , lookup

Mains electricity wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Flexible electronics wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power inverter wikipedia , lookup

Power electronics wikipedia , lookup

Chirp spectrum wikipedia , lookup

Two-port network wikipedia , lookup

Schmitt trigger wikipedia , lookup

Chirp compression wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Buck converter wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Regenerative circuit wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Time-to-digital converter wikipedia , lookup

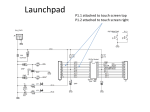

Laboratory Exercise 7 – Timing Circuits We’ll transition to the subject of digital circuits by first considering a special type of combination signal, those that vary continuously in time or frequency but can only have digital voltage levels. The allowable voltages will be the power supply rails, which we’ll call on or off, yes or no, 1 or 0. A common set of digital voltage levels will be introduced in this regard, the nominal TTL (transistor-transistor logic) levels of 0 and 5 volts. These timing circuits are powerful and useful and are commonly encountered in time-sensitive chemical instrumentation (e.g., fluorescence lifetime and chemical kinetics measurements). We’ll start by identifying a few of the general types of frequencies and/or times that we will control. The obvious one is the frequency of a repetitive waveform, like those that the function generator produces for us. Note that frequency is still a well-defined quantity when the waveform is strongly asymmetric: for example a single narrow square voltage pulse followed by a longer “off” time, as shown below. The period is defined as the time between either the rising or falling edges, as indicated below in the top trace and the frequency is the inverse of the period, as usual. A pulse width may be defined for either the “up” or “down” parts of the pulse train, as shown in the lower trace. If we divide the pulse width by the period (and multiply by 100% to obtain a percentage), we obtain the duty cycle. Actually, a duty cycle for either the “on” or the “off” part can be defined (they have to sum to 100%) depending on the application. If we imagine that the second waveform shown below is initiated by the first, we can define a delay time (in this case from the first “up” of the top waveform). These are all parameters that we often need to control in time-sensitive experiments. There are few subtle points that can be illustrated by the above figure. The delay time was initiated (triggered) by the upwards transition on the first pulse train. In some applications, it is more desirable to have the downwards edge of a signal do the triggering. The schematic will sometimes indicate the type of edge-triggering that is used; or that level-triggering is used, where only the voltage level is important, not the transition from one level to the other. The second subtlety illustrated in the figure is a design question: “While the lower pulse is on, another potential trigger has arrived from the upper pulse train. Do we want the second pulse train to ignore this new trigger and continue doing what it was, or do we want it to immediately begin another cycle at this point?” Both types of triggering schemes exist and proper design of timing applications requires choosing an operating mode and knowing how to implement it on the chosen device. When using digital and timing circuits, we often rely on a repetitive waveform to define the frequency and start times for the other logical devices. This waveform is called a “clock” and is generally a pulse train or square wave (a special case of a pulse train with a 50% duty cycle). We will investigate two ways of producing this clock waveform, but the second way (using the 555 timer chip) is the most common solution in scientific applications due to its ease of use, low cost, and stability. The Oscillator (comparator version) We will demonstrate the operating principles of analog timing circuits using a comparator circuit that can behave as a stable oscillator (a.k.a., astable). A comparator is integral to (i.e., built into and important for) the operation of the 555 and the other timing chips that we will use. As intimated earlier in the course, all of the actual “timing” for these circuits is based on the simple RC charging curve that we saw back in Lab 2. Concept Question 1 – What time is implied by a resistance of 100 K and a capacitance of 0.1 F? Circuit Exercise 1 – Breadboard the circuit shown below, noting that the pinout of the 311 comparator is NOT the same as a standard op amp and that the pin numbers are given next to the terminals on the schematic below. Also, note that there is nothing driving this circuit! (What will you trigger the scope with?) Observe the output on the scope as shown. It is illuminating to use the other scope probe to look at pin 3 on the 311. Describe the output waveform (qualitatively, as well as the amplitude, frequency, duty cycle and pulse width). Changing which component would most easily give you a similar waveform with a different frequency? Give it a try and note the new parameters. Is the duty cycle the same as before? Rationalize the output of this circuit. Hint: assume the output is at one rail to start and then figure out what happens next... The 555 Timer Chip - Astable The 555 timer is an IC chip that incorporates the key features of the RC oscillator circuit. It allows us to easily construct an astable by selecting the proper capacitor and resistors as indicated in the circuit below, according to the relationship fosc = (0.7 [RA + 2RB] C)-1. We will see that the 555 chip can also be used in monostable configurations to produce delay generators and pulse width controllers. (Astables are designed to switch back and forth between the two logic levels, while monostables are supposed to stay in one state until told to switch.) Later, we will use the 74123 monostable multivibrators (multivibrator ~ oscillator) to produce the same effects as the 555 at frequencies higher than 200 kHz. When the highest accuracy, precision and speed are desired, RC-based analog oscillators (such as the 555 and 74123) are replaced with crystal oscillators and digital circuitry. Concept Question 2 - Predict the frequency of the astable circuit shown below. In order to produce a variable frequency clock, it would be easiest to replace which component (resistor or cap) with a variable alternative? Ever see a variable cap? Ask me. Circuit Exercise 2 – Breadboard the 555 timer chip in the classic astable configuration as shown below. Observe the output on the scope. Again, this circuit drives itself; there is no input apart from power and ground. Note that we have switched to the 5 VDC power supply - often referred to as VCC. The CC in VCC refers to the collector of a transistor, within the 555. The analogous low voltage for the chips is sometimes called VEE (but is usually just ground in these circuits). Try to put the circuit together in one small region of the breadboard, and don’t tear it down when you finish. (You will use this circuit to drive the next couple of circuits!) It’s also interesting to look at the voltage waveform at the DIS pin (between the two resistors) with the other scope probe, but you don’t have to take any measurements there. What are the voltage levels that correspond to “on” and “off”? Report the frequency and the “on” duty cycle (on time / period x 100 %). Does your frequency result agree with your prediction in the Concept Question above? The “off” duty cycle is predicted to be RB / (RA + 2 RB). How does your measured value compare? Why is it difficult to produce a square wave (a 50 % duty cycle pulse train) with a 555? The 555 Timer Chip – Monostable The monostable, or one-shot, multivibrator is an oscillator with a preferred “resting” voltage level that responds to a trigger from an external source by transitioning to the other state (voltage level) for a controllable time before returning to the resting state. If this seems confusing, have a look at the timing diagram below. The monostable is the bottom trace. It sits around at 0 volts until a trigger is received from the clock and then it goes “high” (+5 V) for a predetermined length of time (pulse width) and finally returns to 0 volts. Generally we would like it to ignore any other potential triggers while it is doing its job, but in some cases that isn’t true. Concept Question 3 – The only important characteristic of a monostable is its pulse width, which is predicted to be tW = 1.1 RAC. Looking at the right hand side of the circuit below, what time do you predict it will produce? Circuit Exercise 3 – Add the circuit shown below on the right: a 555 in a monostable configuration. The monostable (on the right) produces a controlled pulse width triggered by your astable circuit from Circuit Exercise 2 (on the left). Connect the output of the astable to the input of the monostable as shown and then look at both traces on the scope. Note that the astable needs to be modified slightly (resistor B) to produce a better duty cycle for testing the monostable. A quirk of this device is that the trigger has to have returned to the “high” state before the end of the monostable pulse, so you may occasionally see some odd behavior, depending on the actual value of your components. Is the monostable circuit rising edge or falling edge triggered? What is the pulse width you obtained? How does this compare with your prediction from above? Given that the entire timing function of this circuit is based on an RC time, what do you think would happen to the pulse width if the value of the resistor was halved? (You can verify that this works if you want.) Again, don’t tear out the astable circuit unless you are out of time - you will use it below! The 74123 Timer Chip – Variable Delay Generator We treated the output of the circuit above as a pulse width but we could also use the falling edge of the monostable output waveform as the trigger for another monostable, allowing us to use the first monostable to generate a delay time with respect to the trigger from the astable. A variable delay time can be produced by replacing RA in the circuit above with a variable resistor. In principle you could do the same with a variable capacitor, but they are less commonly used. The 74123 IC is an example of a monostable multivibrator capable of operating at higher frequencies (or producing shorter times) than the classic 555 timer chip. The 74123 also contains two multivibrators per chip (saving us the trouble of making two sets of power and ground connections) in a standard 16 pin IC. (The pinout will be on the board or you can find it on the web.) The 74123 also produces both the normal monostable output and its complement (ups become downs and vice versa) allowing a lot of flexibility. In this final exercise, we will build a variable delay from the first half of the chip and a defined output pulse width from the second half of the chip. We will use the astable from Exercise 2 again as the clock to control the frequency of operation of this circuit. Concept Question 4 – For the 74123, the output pulse width for a capacitor greater than 1000 pF should be tw = 0.28 R Cext (1 + 0.7/R), where tw is in nsec, R is in k, and Cext is in pF. What widths do you predict for the two monostable stages in the schematic shown below, when the variable resistor is at its maximum resistance? What is the pulse width for the first stage when the pot is at its minimum resistance? Circuit Exercise 4 – Replace the 555 monostable circuit from above with the following circuit on your breadboard, fed by the astable circuit from Exercise 2. (In this case we aren’t showing the astable explicitly.) Note that the 74123 has two monostables on one chip so you only need one 74123. The numbers on the schematic are the pin numbers on the chip, which is divided roughly in half end-to-end. To make the 74123 work, you must also provide VCC = 5 V to pin 16 and ground to pin 8. Put the output from the astable (the input for this circuit that goes to pin 1) on Channel 1 on the scope and trigger the scope off the negative going edge of the pulse. View the Q(bar) output of the first monostable (pin 13) on Channel 2. Vcc 10 K 14 0.1 uF 1K Cext 15 1 2 3 Astable Out R/Cext A B CL 13 Q 4 Q 74LS123 6 Cext 0.1 uF 7 10 K 10 11 9 R/Cext A B CL 5 Q 12 Q 74LS123 Adjust the pot to its maximum and minimum resistances. Does the pulse width you measure vary as you predicted in the Concept Question above? Have a look at the complementary output of the first monostable (pin 4). In what sense is it the opposite of the other output? Now switch the scope probe to the overall output of the delay generator, the Q output of the second monostable (pin 12). What pulse width is observed here? Is it a positive or negative going pulse? What do you observe when you change the resistance of the pot in the first stage of the monostable? (Measure the pulse width and delay time with respect to the falling edge of the astable.) Give an overall description of what this circuit is doing (your words) starting way back at the astable. These applications demonstrate just a hint of the usefulness of these devices in controlling the timing of experiments and other real world processes. They only incorporate a small selection of the various modes of operation of the chips involved (especially the 74123). After we finish the digital section and are more familiar with truth tables, you could probably glance at the product spec sheets and design these circuits on your own. They are simple to understand based on RC time calculations and are very forgiving. You rarely have to go to that much trouble though, since most manufacturers provide application notes that include schematics and hints for typical applications. Real World Example Describe a chemically relevant experiment where the time between two events needs to be controlled.