PROJECT REPORT On WIRELESS MONITOR AND CONTROL

... CPU divider options. As Configuration bits, these are set when the device is programmed and left in that configuration until the device is reprogrammed. The OSCCON register (Register 2-2) selects the Active Clock mode; it is primarily used in controlling clock switching in power-managed modes. The O ...

... CPU divider options. As Configuration bits, these are set when the device is programmed and left in that configuration until the device is reprogrammed. The OSCCON register (Register 2-2) selects the Active Clock mode; it is primarily used in controlling clock switching in power-managed modes. The O ...

EBVW020A0B

... safety and system protection, always use an input line fuse. The safety agencies require a fast-acting fuse with a maximum rating of 15 A (see Safety Considerations section). Based on the information provided in this Data Sheet on inrush energy and maximum dc input current, the same type of fuse wit ...

... safety and system protection, always use an input line fuse. The safety agencies require a fast-acting fuse with a maximum rating of 15 A (see Safety Considerations section). Based on the information provided in this Data Sheet on inrush energy and maximum dc input current, the same type of fuse wit ...

LT1994

... Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. Note 2: The inputs are protected by a pair of back-to-back diodes. If the d ...

... Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. Note 2: The inputs are protected by a pair of back-to-back diodes. If the d ...

RF / IR Encoder / Decoder Chipset RF Evaluation Boards,

... RF600D has the capability to learn up to 7 unique RF600E transmitters. With the addition of an EEPROM memory device this is increased to 48 RF600E encoders. The RF600D requires only the addition of the following components 1. A ‘learn’ switch which is used in the process of learning a transmitter/en ...

... RF600D has the capability to learn up to 7 unique RF600E transmitters. With the addition of an EEPROM memory device this is increased to 48 RF600E encoders. The RF600D requires only the addition of the following components 1. A ‘learn’ switch which is used in the process of learning a transmitter/en ...

MAX3097E/MAX3098E ±15kV ESD-Protected, 32Mbps, 3V/5V, Triple RS-422/RS-485 Receivers with Fault Detection General Description

... Place a capacitor from the DELAY pin to GND to set the delay (see Setting Delay Time). A high logic level indicates a fault condition on at least one receiver input pair. A low level on this pin indicates no fault condition is present. ...

... Place a capacitor from the DELAY pin to GND to set the delay (see Setting Delay Time). A high logic level indicates a fault condition on at least one receiver input pair. A low level on this pin indicates no fault condition is present. ...

DS4266 DDR Clock Oscillator General Description Features

... The DS4266 consists of a fundamental-mode crystal and synthesizer IC packaged in a 5mm x 3.2mm x 1.49mm, 10-pin LCCC ceramic package. The device produces a frequency output of 266.00MHz. Two differential output types are available: LVDS and LVPECL. The device output can be enabled or disabled throug ...

... The DS4266 consists of a fundamental-mode crystal and synthesizer IC packaged in a 5mm x 3.2mm x 1.49mm, 10-pin LCCC ceramic package. The device produces a frequency output of 266.00MHz. Two differential output types are available: LVDS and LVPECL. The device output can be enabled or disabled throug ...

74LVT244A; 74LVTH244A 1. General description 3.3 V octal buffer/line driver; 3-state

... Please consult the most recently issued document before initiating or completing a design. ...

... Please consult the most recently issued document before initiating or completing a design. ...

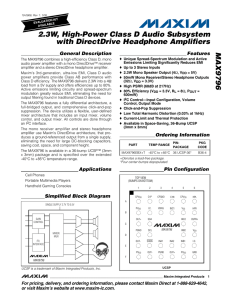

MAX9796 2.3W, High-Power Class D Audio Subsystem with DirectDrive Headphone Amplifiers General Description

... The MAX9796 features a fully differential architecture, a full-bridged output, and comprehensive click-and-pop suppression. The device utilizes a flexible, user-defined mixer architecture that includes an input mixer, volume control, and output mixer. All controls are done through an I2C interface. ...

... The MAX9796 features a fully differential architecture, a full-bridged output, and comprehensive click-and-pop suppression. The device utilizes a flexible, user-defined mixer architecture that includes an input mixer, volume control, and output mixer. All controls are done through an I2C interface. ...

atwinc1500 - Atmel Corporation

... ATWINC1500A is a single chip IEEE 802.11 b/g/n Radio/Baseband/MAC network controller optimized for low-power mobile applications. ATWINC1500A supports single stream 1x1 802.11n mode providing up to 72Mbps PHY rate. ATWINC1500A features fully integrated Power Amplifier, LNA, Switch, and Power Managem ...

... ATWINC1500A is a single chip IEEE 802.11 b/g/n Radio/Baseband/MAC network controller optimized for low-power mobile applications. ATWINC1500A supports single stream 1x1 802.11n mode providing up to 72Mbps PHY rate. ATWINC1500A features fully integrated Power Amplifier, LNA, Switch, and Power Managem ...

MAX8576–MAX8579 3V to 28V Input, Low-Cost, Hysteretic Synchronous Step-Down Controllers General Description

... The MAX8576–MAX8579 synchronous PWM buck controllers use a hysteretic voltage-mode control algorithm to achieve a fast transient response without requiring loop compensation. The MAX8576/MAX8577 contain an internal LDO regulator allowing the controllers to function from only one 3V to 28V input supp ...

... The MAX8576–MAX8579 synchronous PWM buck controllers use a hysteretic voltage-mode control algorithm to achieve a fast transient response without requiring loop compensation. The MAX8576/MAX8577 contain an internal LDO regulator allowing the controllers to function from only one 3V to 28V input supp ...

Digital Electronics

... We will use positive logic (usually the case) Simplest binary function: inversion ...

... We will use positive logic (usually the case) Simplest binary function: inversion ...

a Low Noise, Precision Instrumentation Amplifier AMP01*

... Input offset voltage is very low (20 µV), which generally eliminates the external null potentiometer. Temperature changes have minimal effect on offset; TCVIOS is typically 0.15 µV/°C. Excellent low-frequency noise performance is achieved with a minimal compromise on input protection. Bias current i ...

... Input offset voltage is very low (20 µV), which generally eliminates the external null potentiometer. Temperature changes have minimal effect on offset; TCVIOS is typically 0.15 µV/°C. Excellent low-frequency noise performance is achieved with a minimal compromise on input protection. Bias current i ...

Evaluation Board User Guide UG-119

... The record path includes an integrated microphone bias circuit and six inputs. The inputs can be mixed and muxed before the ADC, or they can be configured to bypass the ADC. The ADAU1361 includes a stereo digital microphone input. The ADAU1361 includes five high power output drivers (two differentia ...

... The record path includes an integrated microphone bias circuit and six inputs. The inputs can be mixed and muxed before the ADC, or they can be configured to bypass the ADC. The ADAU1361 includes a stereo digital microphone input. The ADAU1361 includes five high power output drivers (two differentia ...

MAX8845Z/MAX8845Y/MAX8845X/MAX8845W 28V Linear Li+ Battery Chargers with Battery General Description

... battery-pack detection circuit (DETBAT) that disables the charger when the battery pack is absent. Other features include an active-low control input (EN), an active-low input power source detection output (POK), and a fully charged top-off threshold detection output (CHG). The MAX8845Z/MAX8845Y/MAX ...

... battery-pack detection circuit (DETBAT) that disables the charger when the battery pack is absent. Other features include an active-low control input (EN), an active-low input power source detection output (POK), and a fully charged top-off threshold detection output (CHG). The MAX8845Z/MAX8845Y/MAX ...

AT91SAM7X512

... In Normal Mode, the voltage regulator consumes less than 100 μA static current and draws 100 mA of output current. The voltage regulator also has a Low-power Mode. In this mode, it consumes less than 25 μA static current and draws 1 mA of output current. Adequate output supply decoupling is mandator ...

... In Normal Mode, the voltage regulator consumes less than 100 μA static current and draws 100 mA of output current. The voltage regulator also has a Low-power Mode. In this mode, it consumes less than 25 μA static current and draws 1 mA of output current. Adequate output supply decoupling is mandator ...

Structural computer-aided design of current

... segments, that have the desired values at the discrete points allowed in the multiple-valued logic system. After a few of these C K L circuits, the logic levels have to be restored, because of the generation and propagation of deviations from the exact logic values. A level restoration circuit can b ...

... segments, that have the desired values at the discrete points allowed in the multiple-valued logic system. After a few of these C K L circuits, the logic levels have to be restored, because of the generation and propagation of deviations from the exact logic values. A level restoration circuit can b ...

Design of Arithmetic Circuits Using Resonant Tunneling Diodes and

... Figure 6: Ripple carry adder with 3j2 counters (left) and 2; 3j3 counters (right). has a logic depth of d = n + 1. To decrease the delay time T which is directly proportional to the logic depth d (under the assumption that the wiring delay can be neglected if the cells are locally interconnected) Co ...

... Figure 6: Ripple carry adder with 3j2 counters (left) and 2; 3j3 counters (right). has a logic depth of d = n + 1. To decrease the delay time T which is directly proportional to the logic depth d (under the assumption that the wiring delay can be neglected if the cells are locally interconnected) Co ...

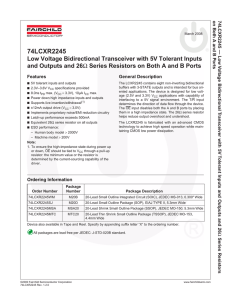

74LCXR2245

... buffers with 3-STATE outputs and is intended for bus oriented applications. The device is designed for low voltage (2.5V and 3.3V) VCC applications with capability of interfacing to a 5V signal environment. The T/R input determines the direction of data flow through the device. The OE input disables ...

... buffers with 3-STATE outputs and is intended for bus oriented applications. The device is designed for low voltage (2.5V and 3.3V) VCC applications with capability of interfacing to a 5V signal environment. The T/R input determines the direction of data flow through the device. The OE input disables ...

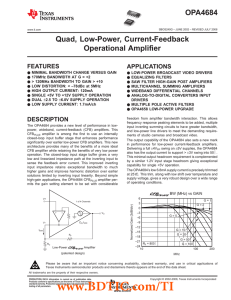

OPA4684 Quad, Low-Power, Current-Feedback Operational Amplifier FEATURES

... freedom from amplifier bandwidth interaction. This allows frequency response peaking elements to be added, multiple input inverting summing circuits to have greater bandwidth, and low-power line drivers to meet the demanding requirements of studio cameras and broadcast video. The output capability o ...

... freedom from amplifier bandwidth interaction. This allows frequency response peaking elements to be added, multiple input inverting summing circuits to have greater bandwidth, and low-power line drivers to meet the demanding requirements of studio cameras and broadcast video. The output capability o ...

Digital Control of Boost PFC Converters Operating in both

... the control of these converters has been performed [10]–[16], input current waveforms with very low harmonic distortion can be achieved, as long as a continuous inductor current is assured. Nevertheless, when these converters are operated at light load, DCM will appear close to the crossover of the ...

... the control of these converters has been performed [10]–[16], input current waveforms with very low harmonic distortion can be achieved, as long as a continuous inductor current is assured. Nevertheless, when these converters are operated at light load, DCM will appear close to the crossover of the ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.