Introducción a los Circuitos Digitales - fc

... Race Condition Back-to-back flops can malfunction from clock skew Second flip-flop fires late Sees first flip-flop change and captures its result Called hold-time failure or race condition CLK1 CLK2 Q1 ...

... Race Condition Back-to-back flops can malfunction from clock skew Second flip-flop fires late Sees first flip-flop change and captures its result Called hold-time failure or race condition CLK1 CLK2 Q1 ...

MAX11162 16-Bit, 500ksps, +5V Unipolar Input, SAR ADC, in Tiny 10-Pin µMAX

... Serial Data Input and Mode Select Input. Daisy-chain mode is selected if SDI is low during the CNVST rising edge. In this mode, SDI is used as a data input to daisy-chain the conversion results of two or more ADCs onto a single SDO line. CS mode is selected if SDI is high during the CNVST rising edg ...

... Serial Data Input and Mode Select Input. Daisy-chain mode is selected if SDI is low during the CNVST rising edge. In this mode, SDI is used as a data input to daisy-chain the conversion results of two or more ADCs onto a single SDO line. CS mode is selected if SDI is high during the CNVST rising edg ...

OPA683 Very Low-Power, Current Feedback OPERATIONAL AMPLIFIER With Disable FEATURES

... performance for very low-power current feedback amplifiers. Delivering a full ±4VPP swing on ±5V supplies, the OPA683 also has the output current to support this swing into a 100Ω load. This minimal output headroom requirement is complemented by a similar 1.2V input stage headroom giving exceptional ...

... performance for very low-power current feedback amplifiers. Delivering a full ±4VPP swing on ±5V supplies, the OPA683 also has the output current to support this swing into a 100Ω load. This minimal output headroom requirement is complemented by a similar 1.2V input stage headroom giving exceptional ...

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... are four storage nodes of SNM [2].For quaternary SRAM inverter input/output characteristics can be shown as in figure 8. Cell ratio (CR) is the ratio between sizes of the driver transistor to the load transistor during the read operation [1]. Pull up ratio (PR) is also nothing but a ratio between si ...

... are four storage nodes of SNM [2].For quaternary SRAM inverter input/output characteristics can be shown as in figure 8. Cell ratio (CR) is the ratio between sizes of the driver transistor to the load transistor during the read operation [1]. Pull up ratio (PR) is also nothing but a ratio between si ...

Evaluates: MAX1566/MAX1567 MAX1567 Evaluation Kit General Description Features

... The MAX1567 evaluation kit (EV kit) is a fully assembled and tested printed-circuit board (PCB) that accepts 2.8V to 4.2V input voltages and provides all the output voltages required for a typical digital still camera. The outputs consist of the main step-down output (3.3V), a stepdown output (1.8V) ...

... The MAX1567 evaluation kit (EV kit) is a fully assembled and tested printed-circuit board (PCB) that accepts 2.8V to 4.2V input voltages and provides all the output voltages required for a typical digital still camera. The outputs consist of the main step-down output (3.3V), a stepdown output (1.8V) ...

R RE ES SE

... Low-Input-Voltage, 500mA LDO Regulator with RESET in SOT and TDFN The MAX1589A low-dropout linear regulator operates from a +1.62V to +3.6V supply and delivers a guaranteed 500mA continuous load current with a low 175mV dropout. The high-accuracy (±0.5%) output voltage is preset to internally trimme ...

... Low-Input-Voltage, 500mA LDO Regulator with RESET in SOT and TDFN The MAX1589A low-dropout linear regulator operates from a +1.62V to +3.6V supply and delivers a guaranteed 500mA continuous load current with a low 175mV dropout. The high-accuracy (±0.5%) output voltage is preset to internally trimme ...

Multiple-Valued Regenerative CMOS Logic Circuits With High

... In the given equations k is ratio of transconductanse of input MOS transistors and MOS transistors in feedback loop. Vtn is threshold voltage of MOS transistors. Dynamic characteristics depend on parameters of the circuit in the same way as for simple standard MV CMOS circuits with high-impedance ou ...

... In the given equations k is ratio of transconductanse of input MOS transistors and MOS transistors in feedback loop. Vtn is threshold voltage of MOS transistors. Dynamic characteristics depend on parameters of the circuit in the same way as for simple standard MV CMOS circuits with high-impedance ou ...

Data Sheet MGA-83563 +22 dBm P 3V Power Amplifier

... loss is typically 8 dB) and may be adequate for many applications as is. The design of the MGA-83563 is such that the second stage will enter into compression before the first stage. The isolation provided by the first stage therefore results in a minimal impact on the input matching as the amplifie ...

... loss is typically 8 dB) and may be adequate for many applications as is. The design of the MGA-83563 is such that the second stage will enter into compression before the first stage. The isolation provided by the first stage therefore results in a minimal impact on the input matching as the amplifie ...

ZL40200 - Microsemi

... The ZL40200 is an LVPECL clock fanout buffer with two identical output clock drivers capable of operating at frequencies up to 750MHz. Inputs to the ZL40200 are externally terminated to allow use of precision termination components and to allow full flexibility of input termination. The ZL40200 can ...

... The ZL40200 is an LVPECL clock fanout buffer with two identical output clock drivers capable of operating at frequencies up to 750MHz. Inputs to the ZL40200 are externally terminated to allow use of precision termination components and to allow full flexibility of input termination. The ZL40200 can ...

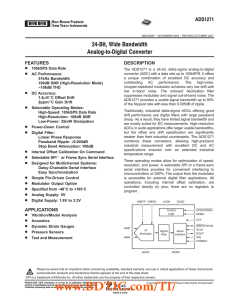

ADS1271 数据资料 dataSheet 下载

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

Delay Sensitivity to Vth Variations

... The fact that series are better than parallel led us to insert a “serializing” dummy transistor into the structure of a gate For a 2-input NAND gate, two potential configurations: ...

... The fact that series are better than parallel led us to insert a “serializing” dummy transistor into the structure of a gate For a 2-input NAND gate, two potential configurations: ...

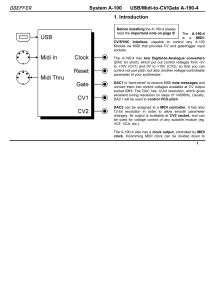

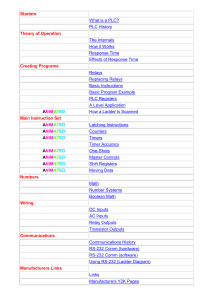

What is a PLC

... After seeing a few of these it will become obvious why its called a ladder diagram. We have to create one of these because, unfortunately, a plc doesn't understand a schematic diagram. It only recognizes code. Fortunately most PLCs have software which convert ladder diagrams into code. This shields ...

... After seeing a few of these it will become obvious why its called a ladder diagram. We have to create one of these because, unfortunately, a plc doesn't understand a schematic diagram. It only recognizes code. Fortunately most PLCs have software which convert ladder diagrams into code. This shields ...

MAX9759 3.2W, High-Efficiency, Low-EMI, Filterless, Class D Audio Amplifier General Description

... The MAX9759 mono Class D, audio power amplifier provides Class AB amplifier audio performance with the benefits of Class D efficiency, eliminating the need for a heatsink and extending battery life. The MAX9759 delivers up to 3.2W of continuous power into a 4Ω load while offering greater than 90% ef ...

... The MAX9759 mono Class D, audio power amplifier provides Class AB amplifier audio performance with the benefits of Class D efficiency, eliminating the need for a heatsink and extending battery life. The MAX9759 delivers up to 3.2W of continuous power into a 4Ω load while offering greater than 90% ef ...

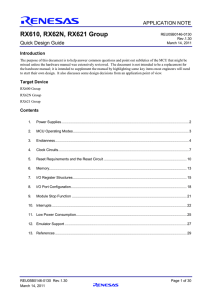

RX610, RX62N, RX621 Group

... Once the MCU has switched from the main clock oscillator (MCO) to the on-chip oscillator (OCOCLK), it continues to run on OCOCLK even if MCO is re-established; a reset of the MCU is required to switch back to the main clock oscillator. The Oscillation Stop Detection circuit is enabled by default aft ...

... Once the MCU has switched from the main clock oscillator (MCO) to the on-chip oscillator (OCOCLK), it continues to run on OCOCLK even if MCO is re-established; a reset of the MCU is required to switch back to the main clock oscillator. The Oscillation Stop Detection circuit is enabled by default aft ...

PTN3381B Enhanced performance HDMI/DVI level shifter with

... Refer to Figure 2 “Functional diagram of PTN3381B”. The PTN3381B level shifts four lanes of low-swing AC-coupled differential input signals to DVI and HDMI compliant open-drain current-steering differential output signals, up to 1.65 Gbit/s per lane. Speed of operation and cable length drive may be ...

... Refer to Figure 2 “Functional diagram of PTN3381B”. The PTN3381B level shifts four lanes of low-swing AC-coupled differential input signals to DVI and HDMI compliant open-drain current-steering differential output signals, up to 1.65 Gbit/s per lane. Speed of operation and cable length drive may be ...

AD5320 数据手册DataSheet 下载

... Serial Data Input. This device has a 16-bit shift register. Data is clocked into the register on the falling edge of the serial clock input. Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates up to 30 MHz. ...

... Serial Data Input. This device has a 16-bit shift register. Data is clocked into the register on the falling edge of the serial clock input. Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates up to 30 MHz. ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.