ICS674-01 - Integrated Device Technology

... for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extende ...

... for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extende ...

SCADAPack LP Hardware Manual

... For 12VDC power-input voltages a 12V to 24V DC/DC converter is used to power 20mA analog input and output devices. The DC/DC converter is controlled by the user application program and may turned on or off. Refer to section 4.2.3-12V to 24V DC/DC Converter Control for more information on DC/DC conve ...

... For 12VDC power-input voltages a 12V to 24V DC/DC converter is used to power 20mA analog input and output devices. The DC/DC converter is controlled by the user application program and may turned on or off. Refer to section 4.2.3-12V to 24V DC/DC Converter Control for more information on DC/DC conve ...

LT5557 - 400MHz to 3.8GHz 3.3V Active Downconverting Mixer.

... The LT®5557 active mixer is optimized for high linearity, wide dynamic range downconverter applications. The IC includes a high speed differential LO buffer amplifier driving a double-balanced mixer. Broadband, integrated transformers on the RF and LO inputs provide single-ended 50Ω interfaces. The ...

... The LT®5557 active mixer is optimized for high linearity, wide dynamic range downconverter applications. The IC includes a high speed differential LO buffer amplifier driving a double-balanced mixer. Broadband, integrated transformers on the RF and LO inputs provide single-ended 50Ω interfaces. The ...

LMV1099 数据资料 dataSheet 下载

... equidistance from the two microphones. This configuration allows the amplitude of the far field signal to be equal at the two microphone inputs, however a slight phase difference may still exist. To simulate a real world application a slight phase delay was added to the FFNSE test. The block diagram ...

... equidistance from the two microphones. This configuration allows the amplitude of the far field signal to be equal at the two microphone inputs, however a slight phase difference may still exist. To simulate a real world application a slight phase delay was added to the FFNSE test. The block diagram ...

MAX3233E/MAX3235E ±15kV ESD-Protected, 1µA, 250kbps, 3.3V/5V, Dual RS-232 Transceivers with Internal Capacitors

... the connected peripherals are inactive, and the UART driving the transmitter inputs is inactive for more than 30 seconds. They turn on again when they sense a valid transition at any transmitter or receiver input. AutoShutdown Plus saves power without changes to the existing BIOS or operating system ...

... the connected peripherals are inactive, and the UART driving the transmitter inputs is inactive for more than 30 seconds. They turn on again when they sense a valid transition at any transmitter or receiver input. AutoShutdown Plus saves power without changes to the existing BIOS or operating system ...

thesis

... while also addressing some of the other limitations of the all-analog subsamplers. For my Master’s of Engineering Thesis, I completed a characterization of this existing Analog Devices subsampling circuit, evaluated alternative architectures, and designed, simulated, and assisted with the layout of ...

... while also addressing some of the other limitations of the all-analog subsamplers. For my Master’s of Engineering Thesis, I completed a characterization of this existing Analog Devices subsampling circuit, evaluated alternative architectures, and designed, simulated, and assisted with the layout of ...

Applications of the CA3080 High-Performance

... Figure 19 shows the configuration for this form of basic gain control (a modulation system). The output signal current (IO) is equal to -gM x VX; the sign of the output signal is negative because the input signal is applied to the inverting input terminal of the OTA. The transconductance of the OTA ...

... Figure 19 shows the configuration for this form of basic gain control (a modulation system). The output signal current (IO) is equal to -gM x VX; the sign of the output signal is negative because the input signal is applied to the inverting input terminal of the OTA. The transconductance of the OTA ...

AD7873

... The AD7873 features direct battery measurement, temperature measurement, and touch pressure measurement. The AD7873 also has an on-board reference of 2.5 V that can be used for the auxiliary input, battery monitor, and temperature measurement modes. When not in use, the internal reference can be shu ...

... The AD7873 features direct battery measurement, temperature measurement, and touch pressure measurement. The AD7873 also has an on-board reference of 2.5 V that can be used for the auxiliary input, battery monitor, and temperature measurement modes. When not in use, the internal reference can be shu ...

LM139 - Tehnopage.ru

... The differential input voltage may be larger than V a without damaging the device. Protection should be provided to prevent the input voltages from going negative more than b0.3 VDC (at 25§ C). An input clamp diode can be used as shown in the applications section. The output of the LM139 series is t ...

... The differential input voltage may be larger than V a without damaging the device. Protection should be provided to prevent the input voltages from going negative more than b0.3 VDC (at 25§ C). An input clamp diode can be used as shown in the applications section. The output of the LM139 series is t ...

1.8V to 28V Input, PWM Step-Up Controllers in µMAX General Description Features

... DC-DC conversion efficiency is optimized with a low 100mV current-sense voltage as well as with Maxim’s proprietary Idle Mode™ control scheme. The controller operates in PWM mode at medium and heavy loads for lowest noise and optimum efficiency, then pulses only as needed (with reduced inductor curr ...

... DC-DC conversion efficiency is optimized with a low 100mV current-sense voltage as well as with Maxim’s proprietary Idle Mode™ control scheme. The controller operates in PWM mode at medium and heavy loads for lowest noise and optimum efficiency, then pulses only as needed (with reduced inductor curr ...

IL260 - NVE Corporation

... limits stated in the specifications. However, NVE recommends that all integrated circuits be handled with appropriate care to avoid damage. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure. ...

... limits stated in the specifications. However, NVE recommends that all integrated circuits be handled with appropriate care to avoid damage. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure. ...

CSE 477. VLSI Systems Design

... since VSB of M2 is not zero (when VB = 0) due to the presence of Cint ...

... since VSB of M2 is not zero (when VB = 0) due to the presence of Cint ...

MAX987/MAX988/MAX991/MAX992/MAX995/MAX996 High-Speed, Micropower, Low-Voltage, SOT23, Rail-to-Rail I/O Comparators ________________General Description

... smaller of the two resulting resistor values. For example, if VREF = 1.2V and VCC = 5V, then the two R3 resistor values are 1.2MΩ and 3.8MΩ. Choose a 1.2MΩ standard value for R3. 2) Choose the hysteresis band required (VHB). For this example, choose 50mV. 3) Calculate R1 according to the following e ...

... smaller of the two resulting resistor values. For example, if VREF = 1.2V and VCC = 5V, then the two R3 resistor values are 1.2MΩ and 3.8MΩ. Choose a 1.2MΩ standard value for R3. 2) Choose the hysteresis band required (VHB). For this example, choose 50mV. 3) Calculate R1 according to the following e ...

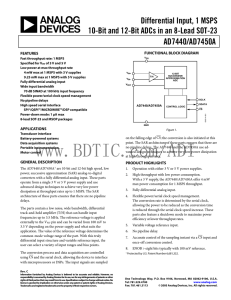

AD7440 数据手册DataSheet下载

... power, successive approximation (SAR) analog-to-digital converters with a fully differential analog input. These parts operate from a single 3 V or 5 V power supply and use advanced design techniques to achieve very low power dissipation at throughput rates up to 1 MSPS. The SAR architecture of thes ...

... power, successive approximation (SAR) analog-to-digital converters with a fully differential analog input. These parts operate from a single 3 V or 5 V power supply and use advanced design techniques to achieve very low power dissipation at throughput rates up to 1 MSPS. The SAR architecture of thes ...

DESIGN OF A HIGH-SPEED CMOS COMPARATOR Master Thesis in Electronics System at

... The latch consists of the cross coupled inverters connected to the ground through the clock as shown in figure 1.5. The latch operates in two modes, reset and evaluation, respectively. During reset phase, the latch output voltage is in the middle of the power supply rail voltages, which give a short ...

... The latch consists of the cross coupled inverters connected to the ground through the clock as shown in figure 1.5. The latch operates in two modes, reset and evaluation, respectively. During reset phase, the latch output voltage is in the middle of the power supply rail voltages, which give a short ...

A Quad of Independently Func Comparators

... Q4 make up a PNP Darlington differential input stage with Q5 and Q6 serving to give single-ended output from differential input with no loss in gain. Any differential input at Q1 and Q4 will be amplified causing Q6 to switch OFF or ON depending on input signal polarity. It can easily be seen that op ...

... Q4 make up a PNP Darlington differential input stage with Q5 and Q6 serving to give single-ended output from differential input with no loss in gain. Any differential input at Q1 and Q4 will be amplified causing Q6 to switch OFF or ON depending on input signal polarity. It can easily be seen that op ...

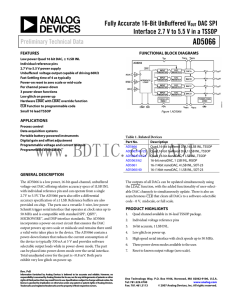

AD5066 数据手册DataSheet 下载

... low, it powers on the SCLK and DIN buffers and enables the input shift register. Data is transferred in on the falling edges of the next 32 clocks. If SYNC is taken high before the 32nd falling edge, the rising edge of SYNC acts as an interrupt and the write sequence is ignored by the device. Power ...

... low, it powers on the SCLK and DIN buffers and enables the input shift register. Data is transferred in on the falling edges of the next 32 clocks. If SYNC is taken high before the 32nd falling edge, the rising edge of SYNC acts as an interrupt and the write sequence is ignored by the device. Power ...

MAX13487E/MAX13488E Half-Duplex RS-485-/RS-422-Compatible Transceiver with AutoDirection Control General Description

... receiver to keep the bus in the correct state. This AutoDirection circuitry consists of a state machine and an additional receive comparator that determines whether this device is trying to drive the bus, or another node on the network is driving the bus. The internal state machine has two inputs: • ...

... receiver to keep the bus in the correct state. This AutoDirection circuitry consists of a state machine and an additional receive comparator that determines whether this device is trying to drive the bus, or another node on the network is driving the bus. The internal state machine has two inputs: • ...

A 21mW 8-b 125 MS/s ADC in 0.09 mm2 0.13 um

... The amplifier used in the CADC is implemented using a cascoded differential pair with resistive load, as shown in Fig. 3. A fully differential implementation is used to achieve low sensitivity to substrate noise and achieve sufficient power supply rejection. The gates of the cascode transistors are ...

... The amplifier used in the CADC is implemented using a cascoded differential pair with resistive load, as shown in Fig. 3. A fully differential implementation is used to achieve low sensitivity to substrate noise and achieve sufficient power supply rejection. The gates of the cascode transistors are ...

General Description Features and Benefits

... Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Expo ...

... Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Expo ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.