DS1232LP/LPS Low Power MicroMonitor Chip FEATURES PIN ASSIGNMENT

... The watchdog timer function forces RST and RST signals to the active state when the ST input is not stimulated for a predetermined time period. The time period is set by the TD input to be typically 150 ms with TD connected to ground, 600 ms with TD left unconnected, and 1.2 seconds with TD connecte ...

... The watchdog timer function forces RST and RST signals to the active state when the ST input is not stimulated for a predetermined time period. The time period is set by the TD input to be typically 150 ms with TD connected to ground, 600 ms with TD left unconnected, and 1.2 seconds with TD connecte ...

ADSP-BF534,36,37

... that 16-bit opcodes represent the most frequently used instructions, resulting in excellent compiled code density. Complex DSP instructions are encoded into 32-bit opcodes, representing fully featured multifunction instructions. Blackfin processors support a limited multi-issue capability, where a 3 ...

... that 16-bit opcodes represent the most frequently used instructions, resulting in excellent compiled code density. Complex DSP instructions are encoded into 32-bit opcodes, representing fully featured multifunction instructions. Blackfin processors support a limited multi-issue capability, where a 3 ...

MAX8739 TFT, LCD, DC-DC Converter with Operational Amplifiers General Description

... The step-up DC-DC converter provides the regulated supply voltage for the panel source driver ICs. The converter is a high-frequency (600kHz/1.2MHz) currentmode regulator with an integrated 14V n-channel MOSFET that allows the use of ultra-small inductors and ceramic capacitors. It provides fast tra ...

... The step-up DC-DC converter provides the regulated supply voltage for the panel source driver ICs. The converter is a high-frequency (600kHz/1.2MHz) currentmode regulator with an integrated 14V n-channel MOSFET that allows the use of ultra-small inductors and ceramic capacitors. It provides fast tra ...

580393681ADM3202_22_1385_c.pdf

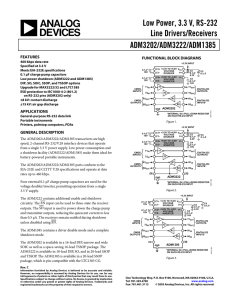

... data transmission at rates well in excess of the EIA/RS-232E specifications. RS-232 voltage levels are maintained at data rates up to 460 kbps even under worst-case loading conditions. This allows high speed data links between two terminals and is suitable for the new generation ISDN modem standards ...

... data transmission at rates well in excess of the EIA/RS-232E specifications. RS-232 voltage levels are maintained at data rates up to 460 kbps even under worst-case loading conditions. This allows high speed data links between two terminals and is suitable for the new generation ISDN modem standards ...

ISD2560/75/90/120 - uri=media.digikey

... and direct addressing are not compatible and cannot be used simultaneously. There are two important considerations for using Operational Modes. First, all operations begin initially at address 0 of its memory. Later operations can begin at other address locations, depending on the Operational Mode(s ...

... and direct addressing are not compatible and cannot be used simultaneously. There are two important considerations for using Operational Modes. First, all operations begin initially at address 0 of its memory. Later operations can begin at other address locations, depending on the Operational Mode(s ...

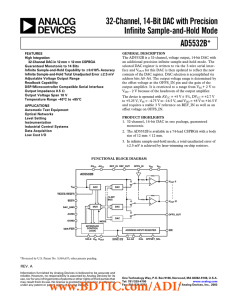

AD5532B: 英文产品数据手册下载

... Offset Input. The user can supply a voltage here to offset the output span. OFFS_OUT can also be tied to this pin if the user wants to drive this pin with the offset channel. Offset Output. This is the acquired/programmed offset voltage that can be tied to OFFS_IN to offset the span. This output tel ...

... Offset Input. The user can supply a voltage here to offset the output span. OFFS_OUT can also be tied to this pin if the user wants to drive this pin with the offset channel. Offset Output. This is the acquired/programmed offset voltage that can be tied to OFFS_IN to offset the span. This output tel ...

PLC cpm2c data sheet

... Note: 1. The DM area, HR area, AR area, and counter values are backed up. If the backup battery or capacitor is discharged, the contents of these ares will be lost and the data values will revert to the defaults. 2. The contents of the program area, read-only DM area (DM 6144 to DM 6599), and PC set ...

... Note: 1. The DM area, HR area, AR area, and counter values are backed up. If the backup battery or capacitor is discharged, the contents of these ares will be lost and the data values will revert to the defaults. 2. The contents of the program area, read-only DM area (DM 6144 to DM 6599), and PC set ...

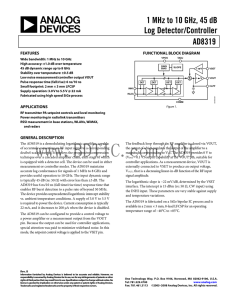

AD8319 数据手册DataSheet 下载

... The AD8319 is a demodulating logarithmic amplifier, capable of accurately converting an RF input signal to a corresponding decibel-scaled output. It employs the progressive compression technique over a cascaded amplifier chain, each stage of which is equipped with a detector cell. The device can be ...

... The AD8319 is a demodulating logarithmic amplifier, capable of accurately converting an RF input signal to a corresponding decibel-scaled output. It employs the progressive compression technique over a cascaded amplifier chain, each stage of which is equipped with a detector cell. The device can be ...

1.5-Gbps LVDS/LVPECL/CML-to

... tsk(p) is the magnitude of the time difference between the tPLH and tPHL. tsk(pp) is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devicesoperate with the same supply voltages, at the same temperature, and have identical packages ...

... tsk(p) is the magnitude of the time difference between the tPLH and tPHL. tsk(pp) is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devicesoperate with the same supply voltages, at the same temperature, and have identical packages ...

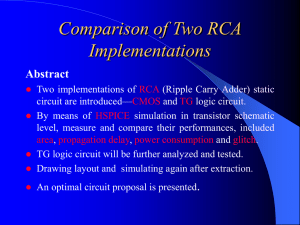

Comparison of Two RCA Implementations_Winter2002

... 3. Sizing of series transistors can be determined by simulation. It may or may not pay to increase size of the series n-transistors and p-transistors. For instance, it may not pay to increase the size of the series transistors connected to A and B in the carry gate in a ripple carry adder, because t ...

... 3. Sizing of series transistors can be determined by simulation. It may or may not pay to increase size of the series n-transistors and p-transistors. For instance, it may not pay to increase the size of the series transistors connected to A and B in the carry gate in a ripple carry adder, because t ...

78M6612 Single-Phase, Dual-Outlet Power and Energy

... power and energy measurement and monitoring system-onchip (SoC) that includes a 32-bit compute engine (CE), an MPU core, RTC, and flash. Our Single Converter Technology® with a 22-bit delta-sigma ADC, four analog inputs, digital temperature compensation, and precision voltage reference supports a wi ...

... power and energy measurement and monitoring system-onchip (SoC) that includes a 32-bit compute engine (CE), an MPU core, RTC, and flash. Our Single Converter Technology® with a 22-bit delta-sigma ADC, four analog inputs, digital temperature compensation, and precision voltage reference supports a wi ...

MQHR-28-28S

... event, there is a startup inhibit delay which will prevent the converter from restarting for approximately 100ms. After the 100ms delay elapses, if the enable inputs are high and the input voltage is within the operating range, the converter will restart. If the VIN input is brought down to nearly 0 ...

... event, there is a startup inhibit delay which will prevent the converter from restarting for approximately 100ms. After the 100ms delay elapses, if the enable inputs are high and the input voltage is within the operating range, the converter will restart. If the VIN input is brought down to nearly 0 ...

ADM3202 数据手册DataSheet 下载

... receivers. Step-up voltage converters coupled with level-shifting transmitters and receivers allow RS-232 levels to be developed while operating from a single 3.3 V supply. ...

... receivers. Step-up voltage converters coupled with level-shifting transmitters and receivers allow RS-232 levels to be developed while operating from a single 3.3 V supply. ...

EC2357-VLSI DESIGN LABORATORY LABORATORY MANUAL FOR SIXTH SEMESTER B.E (ECE)

... In this section, you will use the FPGA Editor to view the design. You can view your design on the FPGA device, as well as edit the placement and routing with the FPGA Editor. 1. Double-click the View/Edit Routed Design (FPGA Editor) process found in the Place & Route group of processes. Your impleme ...

... In this section, you will use the FPGA Editor to view the design. You can view your design on the FPGA device, as well as edit the placement and routing with the FPGA Editor. 1. Double-click the View/Edit Routed Design (FPGA Editor) process found in the Place & Route group of processes. Your impleme ...

LSK489 Applica on Note

... The idea of combining the low noise and simplicity of a BJT op amp with the high input impedance of a JFET input would be ideal, as the IC JFET op amps offer many advantages over BJT op amps, including the absence of input bias current and input noise current. However, they have a greater r than 8 nV ...

... The idea of combining the low noise and simplicity of a BJT op amp with the high input impedance of a JFET input would be ideal, as the IC JFET op amps offer many advantages over BJT op amps, including the absence of input bias current and input noise current. However, they have a greater r than 8 nV ...

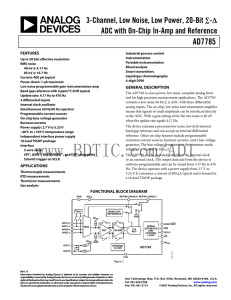

AD7785 3-Channel, Low Noise, Low Power, 20-Bit ∑-Δ

... CS falling edge to DOUT/RDY active time DVDD = 4.75 V to 5.25 V DVDD = 2.7 V to 3.6 V SCLK active edge to data valid delay 4 DVDD = 4.75 V to 5.25 V DVDD = 2.7 V to 3.6 V Bus relinquish time after CS inactive edge ...

... CS falling edge to DOUT/RDY active time DVDD = 4.75 V to 5.25 V DVDD = 2.7 V to 3.6 V SCLK active edge to data valid delay 4 DVDD = 4.75 V to 5.25 V DVDD = 2.7 V to 3.6 V Bus relinquish time after CS inactive edge ...

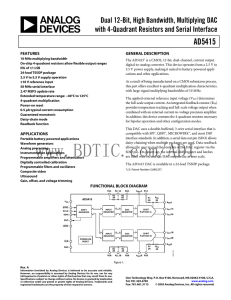

AD5415 数据手册DataSheet 下载

... Load DAC Input. This pin allows asynchronous or synchronous updates to the DAC output. The DAC is asynchronously updated when this signal goes low. Alternatively, if this line is held permanently low, an automatic or synchronous update mode is selected, whereby the DAC is updated on the 16th clock f ...

... Load DAC Input. This pin allows asynchronous or synchronous updates to the DAC output. The DAC is asynchronously updated when this signal goes low. Alternatively, if this line is held permanently low, an automatic or synchronous update mode is selected, whereby the DAC is updated on the 16th clock f ...

ICS674-01 - Integrated Device Technology

... for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extende ...

... for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extende ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.