MB88152A-100/101/102/110/111/112

... CKOUT pin at most the lock-up time (tLK) after the level at the XENS pin is determined. Note : When the pin setting is changed, the CKOUT pin output clock stabilization time is required. Until the output clock signal becomes stable, the output frequency, output clock duty cycle, modulation period, a ...

... CKOUT pin at most the lock-up time (tLK) after the level at the XENS pin is determined. Note : When the pin setting is changed, the CKOUT pin output clock stabilization time is required. Until the output clock signal becomes stable, the output frequency, output clock duty cycle, modulation period, a ...

LTC3672B-2

... inductor from such a large selection of devices can be overwhelming, but following a few basic guidelines will make the selection process much simpler. The buck regulator is designed to work with inductors in the range of 2.2μH to 10μH. A 4.7μH inductor is a good starting point. Larger value inducto ...

... inductor from such a large selection of devices can be overwhelming, but following a few basic guidelines will make the selection process much simpler. The buck regulator is designed to work with inductors in the range of 2.2μH to 10μH. A 4.7μH inductor is a good starting point. Larger value inducto ...

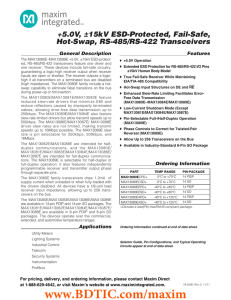

+5.0V, ±15kV ESD-Protected, Fail-Safe, Hot-Swap, RS-485/RS-422 Transceivers General Description Features

... The MAX13080E–MAX13089E +5.0V, ±15kV ESD-protected, RS-485/RS-422 transceivers feature one driver and one receiver. These devices include fail-safe circuitry, guaranteeing a logic-high receiver output when receiver inputs are open or shorted. The receiver outputs a logichigh if all transmitters on a ...

... The MAX13080E–MAX13089E +5.0V, ±15kV ESD-protected, RS-485/RS-422 transceivers feature one driver and one receiver. These devices include fail-safe circuitry, guaranteeing a logic-high receiver output when receiver inputs are open or shorted. The receiver outputs a logichigh if all transmitters on a ...

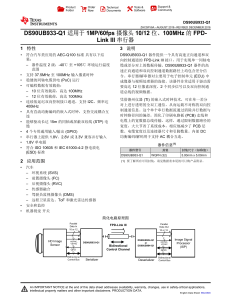

DS90UB933-Q1 FPD-Link III Serializer for 1-MP/60

... Vertical SYNC input. Note: VS transition restrictions: 1. 12-bit mode: No VS restrictions (raw) 2. 10-bit mode: VS restricted to no more than one transition per 10 PCLK cycles. Leave open if unused. ...

... Vertical SYNC input. Note: VS transition restrictions: 1. 12-bit mode: No VS restrictions (raw) 2. 10-bit mode: VS restricted to no more than one transition per 10 PCLK cycles. Leave open if unused. ...

H7E Series - OMRON Industrial Automation

... • When mounting, insert the Counter into the cutout, insert the adapter from the back and push in the Counter while making the gap between the front panel and the cutout panel as small as possible. Use screws to secure the Counter. If waterproofing is desired, insert the waterproof packing. • When s ...

... • When mounting, insert the Counter into the cutout, insert the adapter from the back and push in the Counter while making the gap between the front panel and the cutout panel as small as possible. Use screws to secure the Counter. If waterproofing is desired, insert the waterproof packing. • When s ...

Timing Analysis in Presence of Power Supply and Ground Voltage

... timing. As we will show below, if the supplies are allowed to vary by up to 12.5%, one can observe (by simulation) up to 2.4X increase in gate delay, in 0.13µm CMOS. Thus, for today’s and future technology, the issue of circuit timing is tightly coupled to the question of supply voltage drop. To com ...

... timing. As we will show below, if the supplies are allowed to vary by up to 12.5%, one can observe (by simulation) up to 2.4X increase in gate delay, in 0.13µm CMOS. Thus, for today’s and future technology, the issue of circuit timing is tightly coupled to the question of supply voltage drop. To com ...

High-Speed EMC Optimized Can Transceiver

... during which the driver is switched off while the receiver remains fully functional. In silent mode, all bus activity is passed by the receiver output to the local protocol controller. When data transmission is required, the local protocol controller reverses this low-current silent mode by placing ...

... during which the driver is switched off while the receiver remains fully functional. In silent mode, all bus activity is passed by the receiver output to the local protocol controller. When data transmission is required, the local protocol controller reverses this low-current silent mode by placing ...

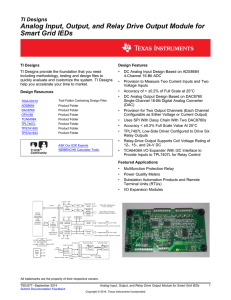

Analog Input, Output, and Relay Drive Output

... The 4-channel analog input design is based on the ADS8684 16-bit SAR ADC device. The ADS8684 is a 4-channel integrated data acquisition systems based on a 16-bit SAR ADC. The device features integrated AFE circuitry for each input channel with over-voltage protection up to ±20 V, a 4-channel multipl ...

... The 4-channel analog input design is based on the ADS8684 16-bit SAR ADC device. The ADS8684 is a 4-channel integrated data acquisition systems based on a 16-bit SAR ADC. The device features integrated AFE circuitry for each input channel with over-voltage protection up to ±20 V, a 4-channel multipl ...

Dual-Output, Low Dropout Volt Regs w/ Integrated SVS for Split

... a high signal to EN (enable) shuts down both regulators, reducing the input current to 1 mA at TJ = +25°C. The device is enabled when the EN pin is connected to a low-level input voltage. The output voltages of the two regulators are sensed at the VSENSE1 and VSENSE2 pins respectively. The input sig ...

... a high signal to EN (enable) shuts down both regulators, reducing the input current to 1 mA at TJ = +25°C. The device is enabled when the EN pin is connected to a low-level input voltage. The output voltages of the two regulators are sensed at the VSENSE1 and VSENSE2 pins respectively. The input sig ...

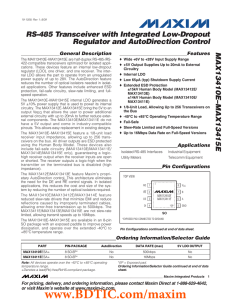

MAX13410E–MAX13415E RS-485 Transceiver with Integrated Low-Dropout Regulator and AutoDirection Control General Description

... Junction Temperature ......................................................+150°C θJA (Note 1)...................................................................52.0°C/W θJC (Note 1).....................................................................6.0°C/W Lead Temperature (soldering, 10s) ....... ...

... Junction Temperature ......................................................+150°C θJA (Note 1)...................................................................52.0°C/W θJC (Note 1).....................................................................6.0°C/W Lead Temperature (soldering, 10s) ....... ...

AH5795 SINGLE PHASE HALL EFFECT LATCH SMART FAN MOTOR CONTROLLER

... nominal motor voltage. The motor speed is proportional to the PWM signal duty. For example, with 5V nominal motor, Vdd pin is maintained at 5V typical while varying the PWM control signal duty to adjust the motor speed linearly. Figure below shows the output O1 and O2 in relation to PWM speed contro ...

... nominal motor voltage. The motor speed is proportional to the PWM signal duty. For example, with 5V nominal motor, Vdd pin is maintained at 5V typical while varying the PWM control signal duty to adjust the motor speed linearly. Figure below shows the output O1 and O2 in relation to PWM speed contro ...

Calculating the Capacitor of the Reset Input

... the reset. Indeed, normally the input is considered to be low when its level reaches Vil1. But in reality the trigger is somewhere between Vih1 and Vil1. So, the worst case condition is considered at the Vih1 level. When the reset is released, the program execution starts and the ALE signal toggles ...

... the reset. Indeed, normally the input is considered to be low when its level reaches Vil1. But in reality the trigger is somewhere between Vih1 and Vil1. So, the worst case condition is considered at the Vih1 level. When the reset is released, the program execution starts and the ALE signal toggles ...

MAX9316A 1:5 Differential (LV)PECL/(LV)ECL/ HSTL Clock and Data Driver General Description

... a single-ended input. This is accomplished by connecting the on-chip reference voltage, VBB, to the inverting or noninverting input of the differential input as a reference. For example, the differential CLK, CLK input is converted to a noninverting, single-ended input by connecting VBB to CLK and c ...

... a single-ended input. This is accomplished by connecting the on-chip reference voltage, VBB, to the inverting or noninverting input of the differential input as a reference. For example, the differential CLK, CLK input is converted to a noninverting, single-ended input by connecting VBB to CLK and c ...

New Components for Building Fuzzy Logic Circuits

... defined above. Some such examples are provided in Table 1. While the initial stored value of Q is 0v and when given 4v for inputs J and K, the resulting Q will continuously toggling between 4v and 2v. Similar unstable conditions appears when initial stored value is 2 and given 4v for inputs J and K. ...

... defined above. Some such examples are provided in Table 1. While the initial stored value of Q is 0v and when given 4v for inputs J and K, the resulting Q will continuously toggling between 4v and 2v. Similar unstable conditions appears when initial stored value is 2 and given 4v for inputs J and K. ...

ADL5511 数据手册DataSheet 下载

... Reference Voltage for Envelope Output. The nominal value is 1.1 V. Envelope Output. The voltage on this pin represents the envelope of the input signal and is referred to EREF. VENV can source a current of up to 15 mA. Capacitive loading should not exceed 10 pF to achieve the specified envelope band ...

... Reference Voltage for Envelope Output. The nominal value is 1.1 V. Envelope Output. The voltage on this pin represents the envelope of the input signal and is referred to EREF. VENV can source a current of up to 15 mA. Capacitive loading should not exceed 10 pF to achieve the specified envelope band ...

MAX17502 60V, 1A, Ultra-Small, High-Efficiency, Synchronous Step-Down DC-DC Converter General Description

... cycle using a PWM comparator, a high-side current-sense amplifier, and a slope-compensation generator. At each rising edge of the clock, the high-side p-channel MOSFET turns on and remains on until either the appropriate or maximum duty cycle is reached, or the peak current limit is detected. During ...

... cycle using a PWM comparator, a high-side current-sense amplifier, and a slope-compensation generator. At each rising edge of the clock, the high-side p-channel MOSFET turns on and remains on until either the appropriate or maximum duty cycle is reached, or the peak current limit is detected. During ...

AD7910 数据手册DataSheet下载

... approximation ADC with accurate control of the sampling instant via a CS input and once-off conversion control. ...

... approximation ADC with accurate control of the sampling instant via a CS input and once-off conversion control. ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.