DIGITAL ELECTRONICS: LOGIC AND CLOCKS

... Logic signals interact by means of gates. The three fundamental gates, AND, OR, and NOT, are named after the three fundamental operations of logic that they carry out. The AND and OR gates each have two inputs and one output. The output state is determined by the states of the two inputs. The NOT ga ...

... Logic signals interact by means of gates. The three fundamental gates, AND, OR, and NOT, are named after the three fundamental operations of logic that they carry out. The AND and OR gates each have two inputs and one output. The output state is determined by the states of the two inputs. The NOT ga ...

Nonvolatile memory chips

... o The signal at c is delayed too, but only by the signal propagation time (at the speed of light). Thus for all intents and purposes, the signal at c is as good as identical to the signal at a. o When the inputs to the AND gate, b and c, are ANDed together, the result is a short pulse, as shown in ...

... o The signal at c is delayed too, but only by the signal propagation time (at the speed of light). Thus for all intents and purposes, the signal at c is as good as identical to the signal at a. o When the inputs to the AND gate, b and c, are ANDed together, the result is a short pulse, as shown in ...

Circuits for pulse shortening

... Monostable flip-flops These circuits have only one stable state, which is break by trigger pulse. Trigger pulse may be longer or shorter than the output pulse. According to the type of connection is the output pulse more or less steep, and therefore needs to consider the connection. Otherwise it can ...

... Monostable flip-flops These circuits have only one stable state, which is break by trigger pulse. Trigger pulse may be longer or shorter than the output pulse. According to the type of connection is the output pulse more or less steep, and therefore needs to consider the connection. Otherwise it can ...

Flip-Flop Circuits

... MASTER-SLAVE JK FLIP-FLOP: Although JK flip-flop is an improvement on the clocked SR flip-flop it still suffers from timing problems called "race" if the output Q changes state before the timing pulse of the clock input has time to go "OFF", so the timing pulse period (T) must be kept as short as po ...

... MASTER-SLAVE JK FLIP-FLOP: Although JK flip-flop is an improvement on the clocked SR flip-flop it still suffers from timing problems called "race" if the output Q changes state before the timing pulse of the clock input has time to go "OFF", so the timing pulse period (T) must be kept as short as po ...

Review of essential terms and concepts T103 Chapter 3

... combinational circuits: A logic device whose output is always based entirely on the given inputs. sequential circuits: a logic device whose output is defined in term of its current inputs in addition to its previous outputs. 17. What is the basic element of a sequential circuit? Flip-flop is the bas ...

... combinational circuits: A logic device whose output is always based entirely on the given inputs. sequential circuits: a logic device whose output is defined in term of its current inputs in addition to its previous outputs. 17. What is the basic element of a sequential circuit? Flip-flop is the bas ...

Electricity revision

... Transformers are used to step up or step down voltage. They only work on AC because an alternating current in the primary coil causes a constantly alternating magnetic field . This will “induce” an alternating current in the secondary coil. ...

... Transformers are used to step up or step down voltage. They only work on AC because an alternating current in the primary coil causes a constantly alternating magnetic field . This will “induce” an alternating current in the secondary coil. ...

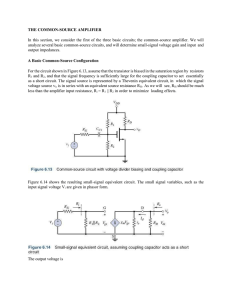

the common-source amplifier

... For the circuit shown in Figure 6.13, assume that the transistor is biased in the saturation region by resistors R1 and R2, and that the signal frequency is sufficiently large for the coupling capacitor to act essentially as a short circuit. The signal source is represented by a Thevenin equivalent ...

... For the circuit shown in Figure 6.13, assume that the transistor is biased in the saturation region by resistors R1 and R2, and that the signal frequency is sufficiently large for the coupling capacitor to act essentially as a short circuit. The signal source is represented by a Thevenin equivalent ...

Lecture 9: Introduction:

... L = ABC + AB C + ABC + A B C = A(BC + B C ) + A(BC + B C) = A(B + C )(B + C) + A(B ⊕ C) = AB CBC + A(B ⊕ C) = AB C + BC + A(B ⊕ C) = AB ⊕ C + A(B ⊕ C) = A ⊕ (B ⊕ C) ...

... L = ABC + AB C + ABC + A B C = A(BC + B C ) + A(BC + B C) = A(B + C )(B + C) + A(B ⊕ C) = AB CBC + A(B ⊕ C) = AB C + BC + A(B ⊕ C) = AB ⊕ C + A(B ⊕ C) = A ⊕ (B ⊕ C) ...

Q.1 What is the lowest positive integer whose Least significant digit

... ‘consecutive ones pairs’ in continuous input stream. Counting is mod 4 i.e returns to 00 after counting 11. (011110… has three pairs of consecutive ones). Q.5 Ckt diag for Xor using only inverters and pass transistors. Q.6 Combinational ckt to output 2’s complement of continuous input stream. Q.7 To ...

... ‘consecutive ones pairs’ in continuous input stream. Counting is mod 4 i.e returns to 00 after counting 11. (011110… has three pairs of consecutive ones). Q.5 Ckt diag for Xor using only inverters and pass transistors. Q.6 Combinational ckt to output 2’s complement of continuous input stream. Q.7 To ...

A|B

... A Digital circuit is based on a number of discrete voltage levels, as distinct from an analog circuit that uses continuous voltages to represent variables directly. ...

... A Digital circuit is based on a number of discrete voltage levels, as distinct from an analog circuit that uses continuous voltages to represent variables directly. ...

Lecture 5

... the input at either the positive- or negative-going clock trigger. • May be implemented with a J-K FF by tying the J input to the K input through an inverter. • Useful for parallel data transfer. ...

... the input at either the positive- or negative-going clock trigger. • May be implemented with a J-K FF by tying the J input to the K input through an inverter. • Useful for parallel data transfer. ...

Automotive Qualified AUIRS2117S and AUIRS2118S Deliver

... • The AUIRS2117S features output signals in phase with the input signal and CMOS Schmitt-triggered inputs with pull-down. • The AUIRS2118S features output signals out of phase with the input signal and CMOS Schmitt-triggered inputs with pull-up. • The new ICs feature proprietary high-voltage integra ...

... • The AUIRS2117S features output signals in phase with the input signal and CMOS Schmitt-triggered inputs with pull-down. • The AUIRS2118S features output signals out of phase with the input signal and CMOS Schmitt-triggered inputs with pull-up. • The new ICs feature proprietary high-voltage integra ...

Physics 517/617 Experiment 6 Digital Circuits

... Almost all of the circuits in this part of the course will be built using the "DIGI DESIGNER" and tested using a logic probe. You should become familiar with both of these tools before you start the lab. The spec sheets for all the chips used in this lab are available in a separate handout. 1) Verif ...

... Almost all of the circuits in this part of the course will be built using the "DIGI DESIGNER" and tested using a logic probe. You should become familiar with both of these tools before you start the lab. The spec sheets for all the chips used in this lab are available in a separate handout. 1) Verif ...

cis480-6

... Consider giving the adder two upper halves operating in parallel by duplicating the upper half’s hardware. Now instead of a single 32-bit adder, we have three 16-bit adders. Call the upper halves U0 and U1. A 0 is fed into U0 as a carry and a 1 is fed into U1 as a carry. Now both start at the sa ...

... Consider giving the adder two upper halves operating in parallel by duplicating the upper half’s hardware. Now instead of a single 32-bit adder, we have three 16-bit adders. Call the upper halves U0 and U1. A 0 is fed into U0 as a carry and a 1 is fed into U1 as a carry. Now both start at the sa ...

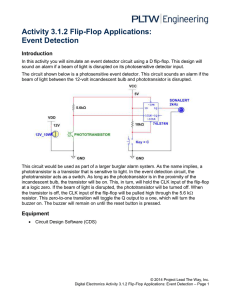

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.