Project: sun tracker

... – attach Q0-Q3 to 4 LEDs in series with 1kΩ resistors to ground – Set function generator to make a 5V square wave (2.5V offset) with frequency = 1Hz, attach it to the clock input – Short D0, D2, D3, and SDR to ground, short D1 and SDL to 5V ...

... – attach Q0-Q3 to 4 LEDs in series with 1kΩ resistors to ground – Set function generator to make a 5V square wave (2.5V offset) with frequency = 1Hz, attach it to the clock input – Short D0, D2, D3, and SDR to ground, short D1 and SDL to 5V ...

LABORATORY VI : Flip-Flops 1 Introduction 2 Laboratory Preliminaries

... Don’t take the circuit apart, we’ll need it for the next exercise. ...

... Don’t take the circuit apart, we’ll need it for the next exercise. ...

CD54HC377/3A CD54HCT377/3A Octal D-Type Flip-Flop with Data Enable Functional Diagram

... CD54HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V CD54HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, VIN, VOUT . . . . . . . . . . . . . . . 0V to VCC ...

... CD54HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V CD54HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, VIN, VOUT . . . . . . . . . . . . . . . 0V to VCC ...

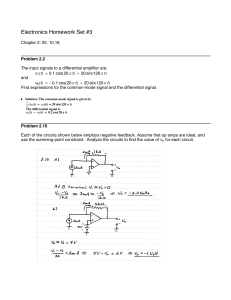

Optional Homework Set 2

... four inputs or one output of five inputs. There was also a restriction that a CLB could have only a total of 5 inputs. To extend the usefulness of such a restricted CLB, they added some multiplexers in front of the LUT. The arrangement is shown below to the right of the gate-level circuit. (The Spar ...

... four inputs or one output of five inputs. There was also a restriction that a CLB could have only a total of 5 inputs. To extend the usefulness of such a restricted CLB, they added some multiplexers in front of the LUT. The arrangement is shown below to the right of the gate-level circuit. (The Spar ...

SP8716/8/9 520MHz LOW CURRENT TWO-MODULUS DIVIDERS

... The set-up time ts is defined as the minimum time that can elapse between a L → H transition of the control input and the next L → H clock pulse transition to ensure that the ÷P mode is obtained. The release time tr is defined as the minimum time that can elapse between a H → L transition of the con ...

... The set-up time ts is defined as the minimum time that can elapse between a L → H transition of the control input and the next L → H clock pulse transition to ensure that the ÷P mode is obtained. The release time tr is defined as the minimum time that can elapse between a H → L transition of the con ...

Final Exam review Solution

... 5. Design a serial parity-bit generator_ Assume the input x is received sequentially_ The parity bit generator will convert every third bit of the input sequence to the even parity bit of the first two bit. For example, if the inputs are 11b01b10b00b… where b denotes don’t cares, then the correspon ...

... 5. Design a serial parity-bit generator_ Assume the input x is received sequentially_ The parity bit generator will convert every third bit of the input sequence to the even parity bit of the first two bit. For example, if the inputs are 11b01b10b00b… where b denotes don’t cares, then the correspon ...

FLSTCD10200909

... 2-, 3- or 4-channel output, unity-gain clock distribution circuits that are ideal for providing a common frequency clock to multi-mode mobile RF applications. They can also be used in mobile phones as a clock reference for baseband peripheral applications such as WLAN, Bluetooth, GPS and FM radio. T ...

... 2-, 3- or 4-channel output, unity-gain clock distribution circuits that are ideal for providing a common frequency clock to multi-mode mobile RF applications. They can also be used in mobile phones as a clock reference for baseband peripheral applications such as WLAN, Bluetooth, GPS and FM radio. T ...

Press release: Acquisition of inductive displacement - ADDI-DATA

... 16 inputs for the acquisition of inductive displacement transducers (Half-Bridge or LVDT) with 16bit resolution, as well as 16 optically isolated digital inputs and outputs, 24 V. For the acquisition of transducer signals, the following acquisition modes are available: Simple mode, Sequence mode and ...

... 16 inputs for the acquisition of inductive displacement transducers (Half-Bridge or LVDT) with 16bit resolution, as well as 16 optically isolated digital inputs and outputs, 24 V. For the acquisition of transducer signals, the following acquisition modes are available: Simple mode, Sequence mode and ...

Solution - University of California, Berkeley

... What can you infer about the dynamic power consumption of static gates being driven by this gate compared to domino logic? Vx switches every clock period even if the inputs are constant while Out remains constant. The activity factor of gates being driven by domino logic will be higher than LSDL and ...

... What can you infer about the dynamic power consumption of static gates being driven by this gate compared to domino logic? Vx switches every clock period even if the inputs are constant while Out remains constant. The activity factor of gates being driven by domino logic will be higher than LSDL and ...

Improved sense-amplifier-based flip-flop

... Thus SAFF is a flip-flop where the SA stage provides a negative pulse on one of the inputs to the slave latch: or (but not both), depending whether the output is to be set or reset. The pulse-generating stage of this flip-flop is the SA described in [5], [6]. It senses the true and complementary dif ...

... Thus SAFF is a flip-flop where the SA stage provides a negative pulse on one of the inputs to the slave latch: or (but not both), depending whether the output is to be set or reset. The pulse-generating stage of this flip-flop is the SA described in [5], [6]. It senses the true and complementary dif ...

CD54HC160/3A CD54HCT160/3A Synchronous Presettable Counters Functional Diagram

... HCT INPUT LOAD TABLE ...

... HCT INPUT LOAD TABLE ...

4.1 Cross coupled sense amplifier flip-flop

... Fig 3.2(a): clock gated sense amplifier flip-flop pulse generating stage In clock gated sense amplifier flip-flop pulse generating stag , to compare the previous and current input values two comparators are used to produce the signals X and Y, by making use of the inputs D and DB and the outputs Q1 ...

... Fig 3.2(a): clock gated sense amplifier flip-flop pulse generating stage In clock gated sense amplifier flip-flop pulse generating stag , to compare the previous and current input values two comparators are used to produce the signals X and Y, by making use of the inputs D and DB and the outputs Q1 ...

A Novel High Speed Differential Ultra Low-Voltage

... 0, the nMOS floating gate is close to Vof f set+ + kin VDD and the pMOS floating-gate is close to Vof f set− + kin VDD due to a positive input transition in the previous evaluation phase. In this case the output needs to be pulled to 1 and this is done by the pMOS and nMOS transistors in parallel. N ...

... 0, the nMOS floating gate is close to Vof f set+ + kin VDD and the pMOS floating-gate is close to Vof f set− + kin VDD due to a positive input transition in the previous evaluation phase. In this case the output needs to be pulled to 1 and this is done by the pMOS and nMOS transistors in parallel. N ...

CD54HC162/3A CD54HCT162/3A Synchronous Presettable Counters Functional Diagram

... for n-bit cascading. In all counters, reset action occurs regardless of the level of the SPE, PE and TE input. If a decade counter is preset to an illegal state or assumes an illegal state when power is applied, it will return to the normal sequence in one count. The look-ahead carry feature simplif ...

... for n-bit cascading. In all counters, reset action occurs regardless of the level of the SPE, PE and TE input. If a decade counter is preset to an illegal state or assumes an illegal state when power is applied, it will return to the normal sequence in one count. The look-ahead carry feature simplif ...

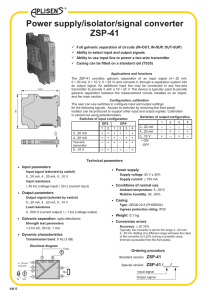

Power supply/ /signal converter ZSP

... 0 ÷ 20 mA, 0 ÷ 10 V, 0 ÷ 20 V) and converts it, through a separation system into an output signal. An additional input line may be connected to any two-wire transmitter to provide it with a 19 ÷ 24 V. The device is typically used to provide galvanic separation between the measurement circuits instal ...

... 0 ÷ 20 mA, 0 ÷ 10 V, 0 ÷ 20 V) and converts it, through a separation system into an output signal. An additional input line may be connected to any two-wire transmitter to provide it with a 19 ÷ 24 V. The device is typically used to provide galvanic separation between the measurement circuits instal ...

Maximum Output Current: Voltage amplifiers are designed to amplify

... and compute Av = Vo /Vi . Note that Av is in general depends on frequency. There may also been some phase difference between Vi and Vo similar to filters. Measuring input and output resistances (or impedances) is not trivial. Part of the difficulty is due to the fact that an Am-meter is limited to 6 ...

... and compute Av = Vo /Vi . Note that Av is in general depends on frequency. There may also been some phase difference between Vi and Vo similar to filters. Measuring input and output resistances (or impedances) is not trivial. Part of the difficulty is due to the fact that an Am-meter is limited to 6 ...

HCF4013B

... technology available in DIP and SOP packages. The HCF4013B consists of two identical, independent data type flip-flops. Each flip-flop has independent data, set, reset, and clock inputs and ...

... technology available in DIP and SOP packages. The HCF4013B consists of two identical, independent data type flip-flops. Each flip-flop has independent data, set, reset, and clock inputs and ...

Small Signal Model and H parameters

... is in the range of 20 to 200. (input open-circuit). It is ...

... is in the range of 20 to 200. (input open-circuit). It is ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.