NTS0104 1. General description Dual supply translating transceiver; open drain; auto

... (An and Bn), one output enable input (OE) and two supply pins (VCC(A) and VCC(B)). VCC(A) can be supplied at any voltage between 1.65 V and 3.6 V and VCC(B) can be supplied at any voltage between 2.3 V and 5.5 V, making the device suitable for translating between any of the voltage nodes (1.8 V, 2.5 ...

... (An and Bn), one output enable input (OE) and two supply pins (VCC(A) and VCC(B)). VCC(A) can be supplied at any voltage between 1.65 V and 3.6 V and VCC(B) can be supplied at any voltage between 2.3 V and 5.5 V, making the device suitable for translating between any of the voltage nodes (1.8 V, 2.5 ...

Design of Signed Multiplier using T-Flip Flop

... Razor relies on a combination of architectural and circuit level techniques for efficient error detection and correction of delay path failures. The concept of razor is illustrated in Fig:4.1 for a pipeline stage. Each flip-flop in the design is augmented with a so called shadow latch which is contr ...

... Razor relies on a combination of architectural and circuit level techniques for efficient error detection and correction of delay path failures. The concept of razor is illustrated in Fig:4.1 for a pipeline stage. Each flip-flop in the design is augmented with a so called shadow latch which is contr ...

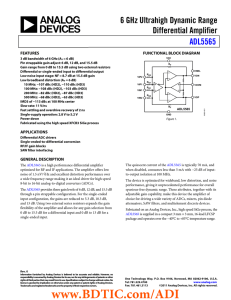

6 GHz Ultrahigh Dynamic Range Differential Amplifier ADL5565

... AV = 6 dB, RL = 200 Ω, VOUT = 2 V p-p AV = 12 dB, RL = 200 Ω, VOUT = 2 V p-p AV = 15.5 dB, RL = 200 Ω, VOUT = 2 V p-p AV = 6 dB, RL = 200 Ω, VOUT = 2 V p-p composite (2 MHz spacing) AV = 12 dB, RL = 200 Ω, VOUT = 2 V p-p composite (2 MHz spacing) AV = 15.5 dB, RL = 200 Ω, VOUT = 2 V p-p composite (2 ...

... AV = 6 dB, RL = 200 Ω, VOUT = 2 V p-p AV = 12 dB, RL = 200 Ω, VOUT = 2 V p-p AV = 15.5 dB, RL = 200 Ω, VOUT = 2 V p-p AV = 6 dB, RL = 200 Ω, VOUT = 2 V p-p composite (2 MHz spacing) AV = 12 dB, RL = 200 Ω, VOUT = 2 V p-p composite (2 MHz spacing) AV = 15.5 dB, RL = 200 Ω, VOUT = 2 V p-p composite (2 ...

- Soundtronics

... resolves the problem of signal delay and signal distortion with chains of MIDI thru to MIDI in (especially where the MIDI thru is via software). MIDI devices such as a master keyboard, sequencer, drum machine etc.. typically only have one output and possibly a MIDI thru port. A MIDI communication si ...

... resolves the problem of signal delay and signal distortion with chains of MIDI thru to MIDI in (especially where the MIDI thru is via software). MIDI devices such as a master keyboard, sequencer, drum machine etc.. typically only have one output and possibly a MIDI thru port. A MIDI communication si ...

B1100-09049

... Form C relays that can be used to report the current system state or control external devices. One or two field-installable 8 port binary output cards can also be inserted in slots B and D, in the bottom row. The SMP I/O binary outputs are specially designed for the power industry. They provide the ...

... Form C relays that can be used to report the current system state or control external devices. One or two field-installable 8 port binary output cards can also be inserted in slots B and D, in the bottom row. The SMP I/O binary outputs are specially designed for the power industry. They provide the ...

ppt

... with exponentially distributed inter-arrival time of input events (rate dat) and sampling with period Tclk (i.e. window TAW is repeated) the upset rate can be calculated ...

... with exponentially distributed inter-arrival time of input events (rate dat) and sampling with period Tclk (i.e. window TAW is repeated) the upset rate can be calculated ...

LAMPIRAN A FOTO WIRELESS SERVICE BELL

... correct device should be chosen according to the requirements of the individual addresses and data. ...

... correct device should be chosen according to the requirements of the individual addresses and data. ...

MAX17003/MAX17004 High-Efficiency, Quad-Output, Main Power- Supply Controllers for Notebook Computers General Description

... Note 1: The MAX17003/MAX17004 cannot operate over all combinations of frequency, input voltage (VIN), and output voltage. For large input-to-output differentials and high switching-frequency settings, the required on-time may be too short to maintain the regulation specifications. Under these condit ...

... Note 1: The MAX17003/MAX17004 cannot operate over all combinations of frequency, input voltage (VIN), and output voltage. For large input-to-output differentials and high switching-frequency settings, the required on-time may be too short to maintain the regulation specifications. Under these condit ...

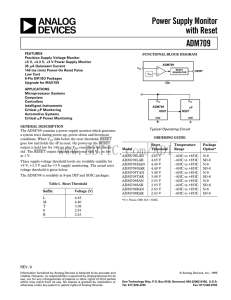

STM809

... the reset time-out period, trec. After this interval, RST returns high. If VCC drops below the reset threshold, RST goes low. Each time RST is asserted, it stays low for at least the reset time-out period. Any time VCC goes below the reset threshold, the internal timer clears. The reset timer starts ...

... the reset time-out period, trec. After this interval, RST returns high. If VCC drops below the reset threshold, RST goes low. Each time RST is asserted, it stays low for at least the reset time-out period. Any time VCC goes below the reset threshold, the internal timer clears. The reset timer starts ...

Old Company Name in Catalogs and Other Documents

... All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renes ...

... All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renes ...

MAX5098A Dual, 2.2MHz, Automotive Buck or Boost Converter with 80V Load-Dump Protection

... load-dump protection circuit utilizes an internal chargepump to drive the gate of an external n-channel MOSFET. When an overvoltage or load-dump condition occurs, the series protection MOSFET absorbs the high voltage transient to prevent damage to lower voltage components. The DC-DC converters opera ...

... load-dump protection circuit utilizes an internal chargepump to drive the gate of an external n-channel MOSFET. When an overvoltage or load-dump condition occurs, the series protection MOSFET absorbs the high voltage transient to prevent damage to lower voltage components. The DC-DC converters opera ...

RNA52A10T Data Sheet Descriptive Title

... 2. For capacitor C1, select a type which has excellent frequency characteristics. For stable operation, place it between the VDD pin and the GND pin and as close as is possible to the chip. 3. The value of capacitor C1 must suit the system environment in terms of the quality of the power supply and ...

... 2. For capacitor C1, select a type which has excellent frequency characteristics. For stable operation, place it between the VDD pin and the GND pin and as close as is possible to the chip. 3. The value of capacitor C1 must suit the system environment in terms of the quality of the power supply and ...

RMR1781ME68F9F-1600

... 1. Maximum DC value may not be greater than 1.425V. The DC value is the linear average of VDD/VDDQ(t) over a very long period of time (e.g., 1 sec). 2. If maximum limit is exceeded, input levels shall be governed by DDR3 specifications. 3. Under these supply voltages, the device operates to this DDR ...

... 1. Maximum DC value may not be greater than 1.425V. The DC value is the linear average of VDD/VDDQ(t) over a very long period of time (e.g., 1 sec). 2. If maximum limit is exceeded, input levels shall be governed by DDR3 specifications. 3. Under these supply voltages, the device operates to this DDR ...

to this file: /ucq_series

... (3) Note that Maximum Power Derating curves indicate an average current at nominal input voltage. At higher temperatures and/or lower airflow, the DC-DC converter will tolerate brief full current outputs if the total RMS current over time does not exceed the Derating curve. All Derating curves are ...

... (3) Note that Maximum Power Derating curves indicate an average current at nominal input voltage. At higher temperatures and/or lower airflow, the DC-DC converter will tolerate brief full current outputs if the total RMS current over time does not exceed the Derating curve. All Derating curves are ...

S8VS (15/30/60/90/120/180/240/480-W Models)

... Do not use an inverter output for the Power Supply. Inverters with an output frequency of 50/60 Hz are available, but the rise in the internal temperature of the Power Supply may result in ignition or burning. *2. For a cold start at 25°C. Refer to Engineering Data on page 18 for details. *3. If the ...

... Do not use an inverter output for the Power Supply. Inverters with an output frequency of 50/60 Hz are available, but the rise in the internal temperature of the Power Supply may result in ignition or burning. *2. For a cold start at 25°C. Refer to Engineering Data on page 18 for details. *3. If the ...

LT1806/LT1807 - 325MHz, Single/Dual, Rail-to-Rail Input and Output, Low Distortion, Low Noise Precision Op Amps

... The LT®1806/LT1807 are single/dual low noise rail-to-rail input and output unity-gain stable op amps that feature a 325MHz gain-bandwidth product, a 140V/μs slew rate and a 85mA output current. They are optimized for low voltage, high performance signal conditioning systems. The LT1806/LT1807 have a ...

... The LT®1806/LT1807 are single/dual low noise rail-to-rail input and output unity-gain stable op amps that feature a 325MHz gain-bandwidth product, a 140V/μs slew rate and a 85mA output current. They are optimized for low voltage, high performance signal conditioning systems. The LT1806/LT1807 have a ...

PCA9513A; PCA9514A 1. General description Hot swappable I

... SCLIN and SCLOUT become identical with each acting as a bidirectional buffer that isolates the input capacitance from the output bus capacitance while communicating the logic levels. A LOW forced on either SDAIN or SDAOUT will cause the other pin to be driven to a LOW by the part. The same is also t ...

... SCLIN and SCLOUT become identical with each acting as a bidirectional buffer that isolates the input capacitance from the output bus capacitance while communicating the logic levels. A LOW forced on either SDAIN or SDAOUT will cause the other pin to be driven to a LOW by the part. The same is also t ...

TPS70102 数据资料 dataSheet 下载

... regulator 1) and is directly proportional to the output current. Additionally, since the PMOS pass element is a voltage-driven device, the quiescent current is very low and independent of output loading (maximum of 230μA over the full range of output current). This LDO family also features a sleep m ...

... regulator 1) and is directly proportional to the output current. Additionally, since the PMOS pass element is a voltage-driven device, the quiescent current is very low and independent of output loading (maximum of 230μA over the full range of output current). This LDO family also features a sleep m ...

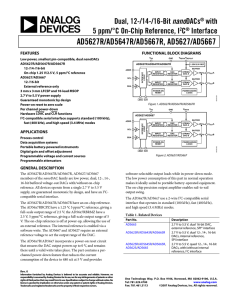

Document

... Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation. Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation. Ground reference point for all circuitry on the part. Pulsing this pin low allows any or all DAC registers to be updated if the inputs ...

... Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation. Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation. Ground reference point for all circuitry on the part. Pulsing this pin low allows any or all DAC registers to be updated if the inputs ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.